集成电路综合自动测试系统软硬件接口设计

冯建呈,闫丽琴,王占选,冯敏洁,周欣萍,孟 旭

(1.北京航天测控技术有限公司,北京 100041;2.北京宇航系统工程研究所,北京 100076)

0 引言

测试是保证集成电路良率的重要手段,其贯穿了集成电路设计、生产、筛选等环节[1-3]。受限于国内集成电路测试设备的发展水平,目前国内集成电路特别是超大规模集成电路的测试,主要采用国外进口设备,如美国泰瑞达公司的J750系列、UltraFlex、日本爱德万公司的V93000以及NI公司的STS测试系统[4-7]。但因集成电路测试系统专业性强、应用范围较为集中,国内外也未形成测试系统标准,这种现状导致各厂家研制的集成电路测试系统之间的软硬件兼容性差。随着国内集成电路产业的发展,集成电路产量急剧增加,并且集成电路的规模越来越大,导致测试程序、测试接口板的开发难度和工作量越来越大。

测试程序开发方面。由于测试系统之间互不兼容,测试厂、封测厂等为了提升测试产能,需要在不同的测试软件中重复开发,导致时间成本、经济成本急剧增加。基于自动测试模型接口采用建模方法,可在测试程序开发之前,即完成全部相关测试内容的模型构建,通过测试程序导入、解析生成测试程序的核心部分,根据不同测试软件的存储格式要求存储模型,可应用于不同的测试软件,一定程度降低了测试程序的移植难度。

测试系统硬件接口方面。因为国产集成电路测试系统的规模相对较小、测试信号的速率相对较低,在测试接入接口方面一般采用固定针的连接器,与国外领先机台之间存在较大的技术差距。如国外系统中的数字通道板最高测试速率可达1.6 Gbps[8-10],而国产集成电路测试设备的测试速率较低,一般在200 MHz以下,主要应用在中小规模数字集成电路、模拟电路和混合信号电路测试中,基本不能满足FPGA、CPU、DSP等典型国产超大规模集成电路的测试需求。通过研制基于弹性接入的硬件平台接口,可满足超大规模集成电路高密度、大通道数、高速率的信号传递需求。

针对当前国内集成电路产业快速发展的现状,基于上述测试接口,进一步研制了国产超大规模集成电路综合自动测试系统,该系统未来可有效满足国产超大规模集成电路在设计验证、量产测试等方面的测试需求。

1 总体接口设计

所研制的超大规模集成电路综合自动测试验证系统(以下简称:测试系统),包含硬件平台、软件平台,对外接口包含硬件平台接口部分和软件平台接口部分。

其中硬件平台提供被测集成电路所需的硬件测试资源,硬件平台接口主要包含测试对接锁紧装置和电气信号接口,实现测试接口板与测试系统中测试头的电气连接。软件平台具备开发运行、数据分析、状态监测、硬件管理等功能,其对外接口主要包含测试程序开发UI和自动测试模型接口。超大规模集成电路综合测试验证系统对外接口组成如图1所示。

图1 超大规模集成电路综合测试验证系统对外接口组成图

2 基于模型描述的软件接口设计

2.1 软件总体组成

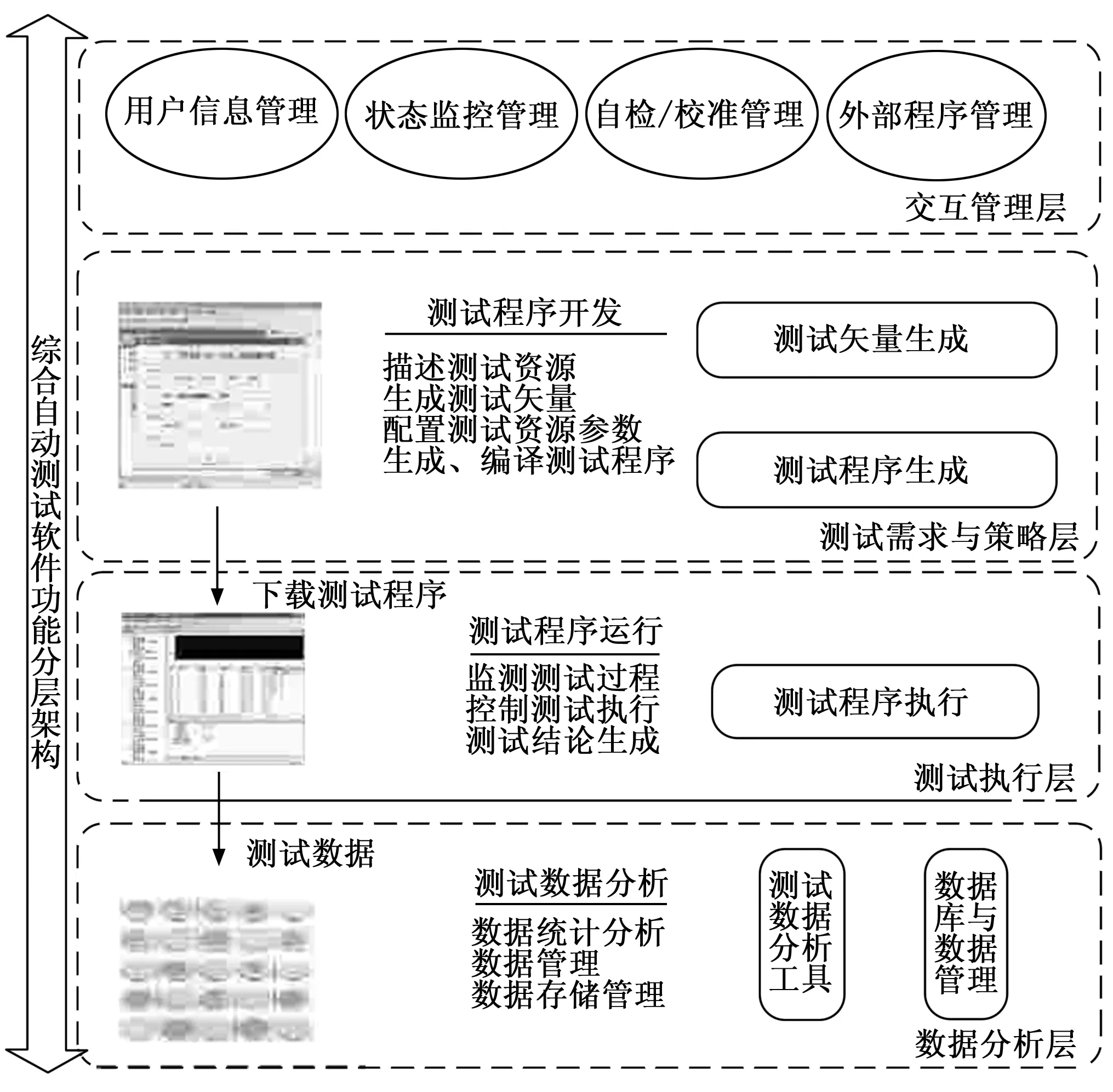

综合自动测试软件[11-13]采用开放式、模块化的软件架构以及层次化的设计方法,提高软件调试过程的灵活性,方便进行功能扩展。软件功能架构共包含4个功能层次:人机交互管理层、测试需求与策略层、测试执行层和数据分析层。

交互管理层提供友好的人机交互界面,用于人机交互管理和维护操作,包括用户信息管理、状态监控管理、系统自检/自校准管理和软件对外围程序的接口管理功能。测试需求与策略层从仿真设计文件出发,最终生成测试系统可以识别的测试程序策略文件;基于测试需求分析,通过对测试资源和测试方法进行描述,生成测试激励数据,相应配置测试资源参数,编译、链接生成测试程序策略文件,主要包含测试开发软件子平台的2个功能模块:测试矢量生成和测试程序生成。测试执行层的核心功能是将测试需求与策略层生成的程序文件下载到测试头硬件资源的存储器中,并具体执行测试流程,控制系统仪器设备完成对被测DUT的测试过程,属于测试执行的实体,实现对待测芯片的具体测试。数据分析层基于可视化数据分析工具和数据库存储分析技术,对测试执行过程输出的结果数据进行分析,主要包括数据分析软件子平台的2个功能模块:测试数据分析工具和数据库与数据管理功能,实现对测试结果数据的总体分析与存储。综合自动测试软件功能层次架构图如图2所示。

图2 软件功能层次架构图

2.2 自动测试模型总体设计[14]

测试程序开发UI主要满足用户在软件平台开发测试程序的需要。自动测试模型接口则是采用建模方法,在测试程序开发之前,即完成全部测试内容模型构建,并生成测试模型,可用于通过模型检查发现测试配置冲突等问题,并通过测试模型导入解析直接生成测试程序。

集成电路自动测试模型建模方法包括UUT(被测对象)模型建模、连接关系模型建模、信号模型建模、测试项目模型建模、测试流程模型建模、模型文件格式等。其中模型文件的具体格式根据所面向的测试软件的不同,格式可自定义。

集成电路自动测试模型建模基本流程为首先建立UUT(被测对象)模型建模,UUT模型为全部模型的基础。在此基础上,依次完成连接关系模型建模、信号模型建模、测试项目模型建模、测试流程模型建模等。其中信号模型建模包含电源属性,电平、时序、向量等数字信号属性,模拟信号、射频信号属性等的设置。在模型建立完毕后,可以导出为模型文件。各模型文件格式根据所面向的测试软件的不同,格式可自定义。集成电路自动测试模型建模方法流程图如图3所示。

图3 集成电路自动测试模型建模方法流程图

上述流程中,UUT模型主要实现被测集成电路的引脚信号及其输入输出属性描述;连接关系模型,主要描述测试仪器通道与被测集成电路引脚之间的连接关系;信号模型,主要描述被测集成电路测试所需的电源属性,电平、时序、向量等数字信号属性,模拟信号、射频信号等属性;测试项目模型,基于信号模型,组合出面向不同测试需求的测试项目;测试流程模型,基于测试项目模型,组合出测试项目的执行顺序、执行失败或通过下的跳转目标、执行开始与结束的动作、中断的标志。

2.3 UUT模型设计

UUT模型是其余测试模型的基础。UUT模型创建过程如下:首先建立UUT引脚名称,UUT引脚名称是所有测试关系互相索引的基础数据。在引脚名称的基础上,配置各引脚的属性:输入、输出、差分、模拟、射频、串行、电源等不同属性。为了提高测试效率,可对UUT引脚分组,如建立输入信号组、输出信号组、数据总线信号组等,并予以命名,在后续的其他模型建模中,可直接引用。上述操作完毕后,可按照模型文件格式保存。

以某型存储器的UUT模型建模为例,首先建立存储器引脚名称:电源引脚、数据引脚、地址引脚、控制引脚等;其次设置各引脚的属性:电源、输入、输出、双向等不同属性。为了提高测试效率,可对存储器引脚分组,如数据总线、控制总线、地址总线。在后续的其他模型建模中,可直接引用。上述操作完毕后,可按照模型文件格式保存。以存储器为例的UUT模型建模流程图如图4所示。

图4 UUT模型建模流程图

2.4 连接关系模型设计

连接关系模型建立被测集成电路与测试仪器资源通道的映射关系。首先读取UUT模型,解析出UUT模型中的引脚名称和信号属性。按照引脚名称为索引,逐个连接或者设置仪器资源通道。在连接通道过程中,对UUT引脚的属性和仪器资源通道属性进行匹配性检查,如不匹配,则输出错误信息。连接关系建立后,可根据模型文件格式保存连接关系模型。

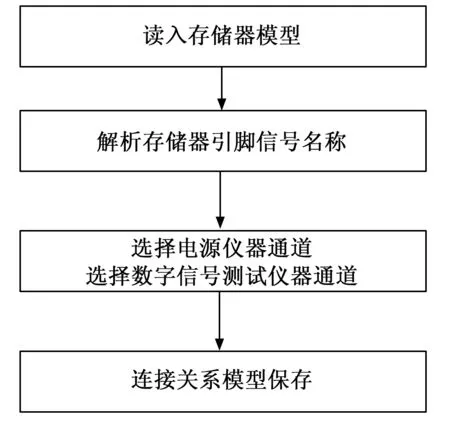

以某型存储器的连接关系模型建模为例。首先读取存储器的UUT模型,解析出存储器模型中的引脚名称和信号属性。按照引脚名称逐个连接电源通道、数字测试仪器通道。在连接通道过程中,对存储器引脚的属性和电源通道、数字测试仪器通道属性进行匹配性检查。以存储器为例的连接关系模型建模流程图如图5所示。

图5 连接关系模型建模流程图

2.5 信号模型设计

信号模型,主要描述被测集成电路测试所需的信号属性。首先读取并解析UUT引脚信号名称及其属性,后续在配置信号模型属性时,将根据各引脚属性进行规则检查,如信号属性与引脚属性冲突,则输出错误信息。如对电源引脚配置数字信号属性,则应输出错误信息。

信号属性分为:电源属性,电平、时序、向量等数字信号属性,模拟信号、射频信号等,可根据测试需要扩展信号类型。

电源信号属性配置:根据测试类型不同,建立电源信号组合,如工作电源信号组合,拉偏电源信号组合,静态电源信号组合等。在每种电源信号组合下,对于各个电源引脚进行参数配置,主要配置测试状态(如开、关)、参数范围(如电压范围、电流范围)、运行模式(如各路电源的开启顺序、开启延时、关闭顺序、关闭延时等)等模式。

电平信号属性配置:根据测试类型不同,建立电平信号组合,如连接性(开短路)电平信号组合,功能测试电平信号组合等。在每种电平信号组合下,对于各个数字引脚进行参数配置,主要根据数字引脚的输入、输出属性,配置VIL、VIH、VOL、VOH、IOH、IOL、负载模式等。

时序信号属性配置:根据测试类型不同,建立时序信号组合,如交流参数时序信号组合,功能测试时序信号组合等。在每种时序信号组合下,对于各个数字引脚进行参数配置,主要根据数字引脚的输入、输出属性,基于事件驱动的原理,配置每个事件动作的特性和发生事件,如事件A为驱动高电平,发生在0 ms,事件B为驱动低电平,发生在1 ms等。

向量关系属性配置:根据测试类型不同,建立向量关系组合,如直流参数测试向量关系组合,交流参数测试向量关系组合,功能测试向量关系组合等。在每种向量关系组合下,首先按照适用的软件平台需要的向量格式编写向量文件,如参照STIL标准,向量文件中的UUT引脚要与前述UUT模型文件完全一致。向量文件的数量应不少于测试向量组合的数量,在编写完向量后,在各个向量组合的属性中选择对应的向量文件。配置完毕后,可根据模型文件格式保存模型。模拟信号、射频信号以及其他根据测试需要扩展信号的属性配置可参照上述过程自定义。

在完成上述全部信号属性定义并保存模型后,按照模型文件格式保存为信号模型文件。

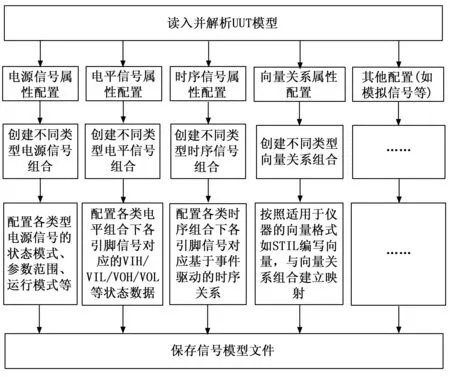

以某型存储器的信号模型建模为例。存储器的信号模型建模包括电源属性,电平、时序、向量等数字信号属性配置。首先读取并解析存储器引脚信号名称及其属性。然后依次配置电源信号属性、电平信号属性、时序信号属性,向量关系属性。其中向量关系属性配置:主要分为针对延时时间、建立时间、读写时间等参数测试的向量关系组合,以及功能测试向量关系组合等。在每种向量关系组合下,采用STIL标准格式编写向量文件。功能测试向量关系组合对应的向量文件主要包含MARCH、WALK、全0全1等。

在完成上述全部信号属性定义并保存模型后,按照模型文件格式保存为信号模型文件。以存储器为例的信号模型建模流程图如图6所示。

图6 信号模型建模流程图

2.6 测试项目模型设计

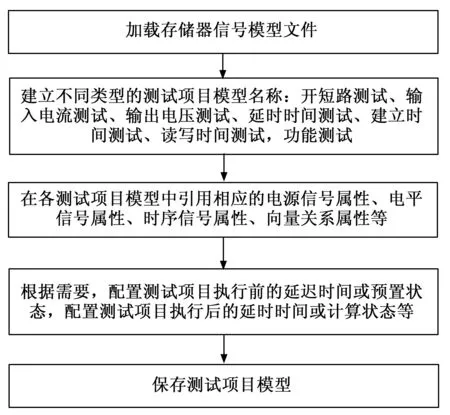

测试项目模型,基于信号模型文件,组合出面向不同测试需求的测试项目。首先加载信号模型文件,根据需要建立不同类型的测试项目模型名称,如开短路测试、直流参数测试(如输入电压测试、输出电流测试等)、交流参数测试(如传输时间测试)、功能测试等;其次在各测试项目中,配置需要引用的信号属性,包括电源、数字信号、模拟信号等的属性。为保证测试程序正确执行,在测试项目执行前或执行后可加入相应的执行动作,如延时、计算等。配置完毕后,可根据模型文件格式保存模型。

以某型存储器的测试项目模型为例。首先加载信号模型文件,依次建立测试项目,配置需要引用的信号属性。以存储器为例的测试项目模型建模流程图如图7所示。

图7 测试项目模型建模流程图

2.7 测试流程模型设计

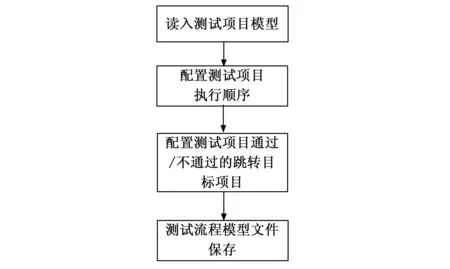

测试流程模型,基于测试项目模型文件,首先解析出测试模型,其次按照测试需求,设置各测试项目的执行顺序,并设置各个测试项目执行失败或通过下的跳转目标,设置测试流程模型的整体的执行开始与结束的动作以及中断的标志。配置完毕后,可根据模型文件格式保存模型。

以某型存储器的测试流程模型为例。基于测试项目模型文件,首先解析出测试模型,其次按照测试需求,设置各测试项目的执行模式等。以存储器为例的测试流程模型建模流程图如图8所示。

图8 测试流程模型建模流程图

3 测试系统集成与校准方案

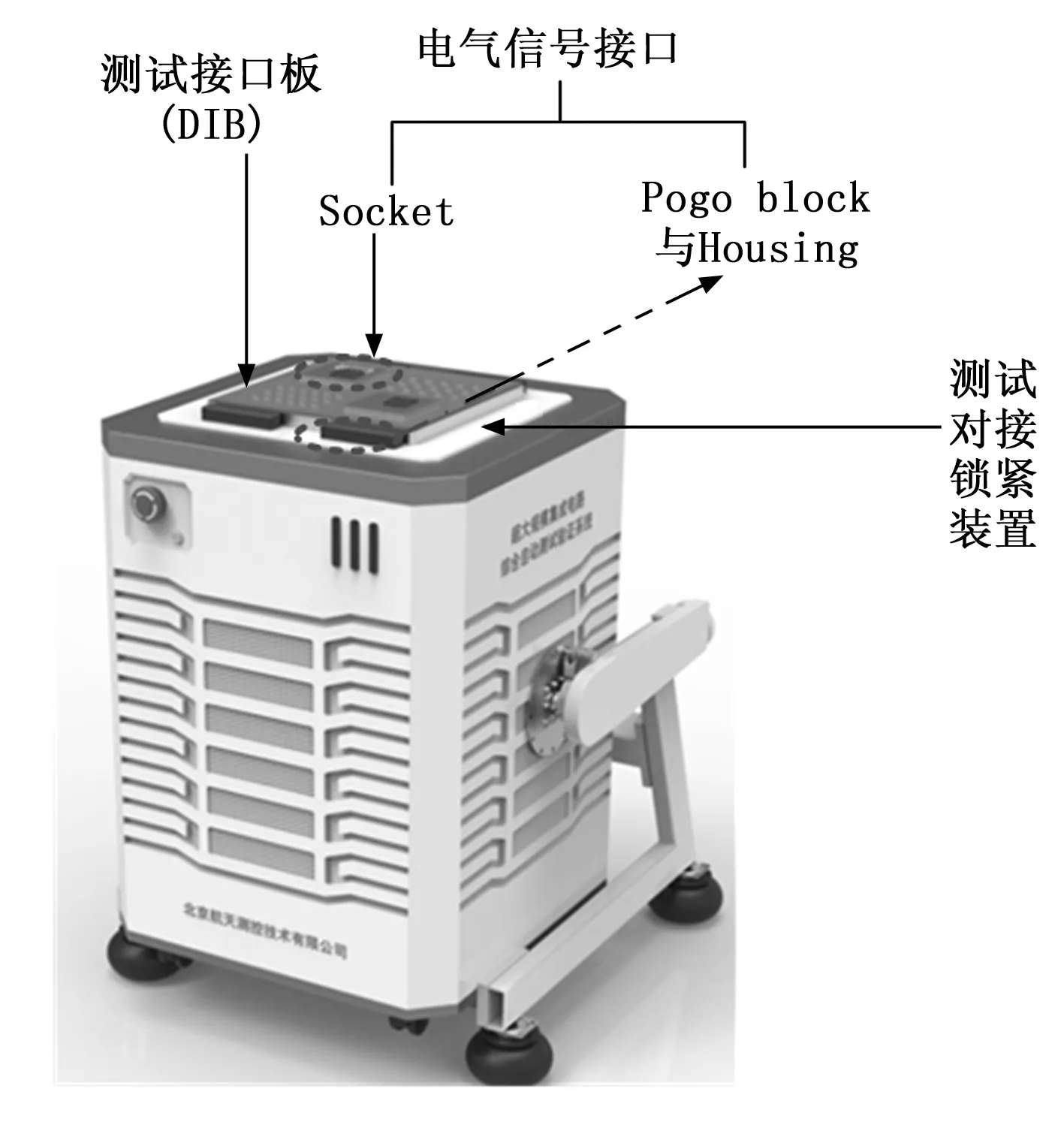

硬件平台接口主要包含测试对接锁紧装置和电气信号接口。测试对接锁紧装置用来锁紧DIB(测试接口板),达到DIB与测试头内部Pogo Pin(弹性连接针)连接的目的。DIB结构用来加强和支撑DIB电路板、并实现锁紧对接的辅助结构。通过硬件平台接口,实现测试头硬件资源通道与测试接口板的资源对接。硬件平台接口组成如图9所示。

图9 硬件接口组成框图

测试头硬件平台接口安装使用示意图如图10所示。

图10 对接装置示意图

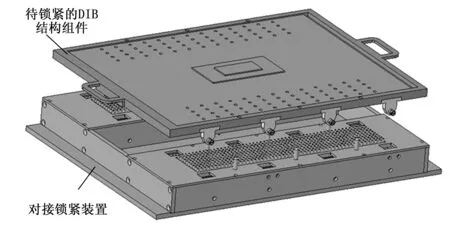

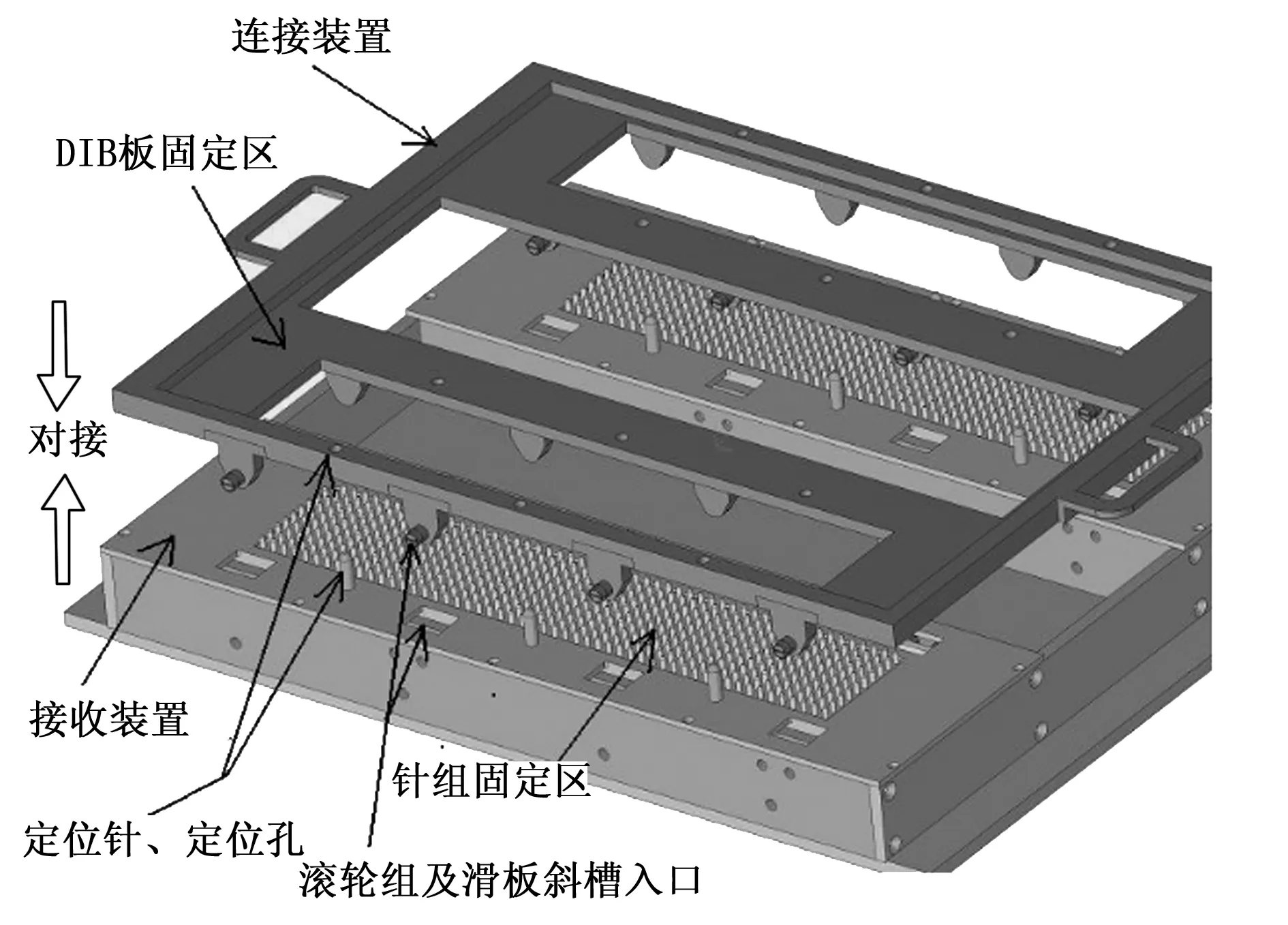

3.1 测试对接锁紧装置

测试对接锁紧装置包含对接锁紧结构及动力装置等。DIB结构和对接锁紧装置安装示意图如图11所示。

图11 DIB结构和对接锁紧装置安装示意图

其工作过程如下:将DIB结构上的滚轮组放入滑动板斜槽入口中,定位针及定位孔保证DIB结构放入的位置精度,所有滑动板同步水平运动,将DIB电路板滚轮垂直压入,实现DIB电路板的锁紧。DIB结构和对接锁紧装置安装示意图如图12所示。

图12 DIB结构和对接锁紧装置安装示意图

测试对接锁紧装置的所有滑板必须同步运动,以实现DIB电路板的垂直、平稳、完全压入。为保障对接的同步性,机构采用4组平面连杆,包括组A和组B各一对,通过轴实现同步运动。运动过程是:动力源水平直线推动杠杆,利用支点反方向拉动连杆A,连杆A带动A组滑板向轴侧运动,通过连杆B及转臂将轴推转,轴带动B组滑板同步运动,从而实现所有滑动板同步运动[15-18]。对接锁紧装置内部机构如图13所示。

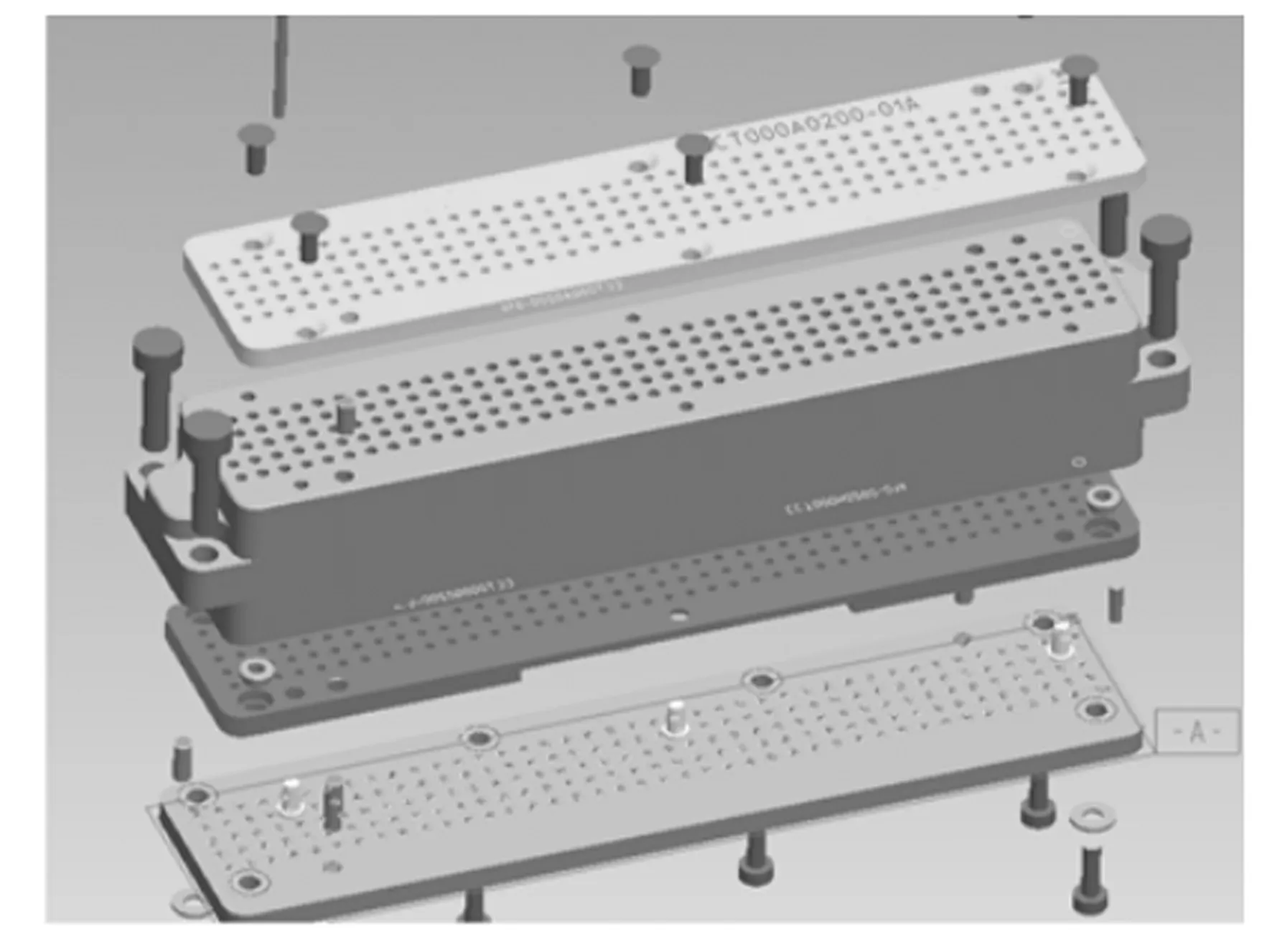

图13 对接锁紧装置内部机构爆炸图

3.2 Pogo Block设计方案

电气信号接口包含Pogo Block(弹性连接器)、测试线缆等,核心为Pogo Block。Pogo Block主要由上盖板、下盖板、本体、PCB四件部件构成。上盖板、下盖板采用工程塑料,起到Pogo Pin导向和压合作用。本体为全金属材料,Pogo Pin与本体在结构上是同轴探针结构。通孔四周由空气绝缘,达到50欧姆的阻抗匹配要求。PCB 通过螺丝与block锁住。

Pogo Pin应用于集成电路测试时测试信号输出与测试DIB之间的精密连接,具有很强的稳定性和耐久性[19-20]。Pogo Pin主要以弹簧针接触体为核心,可传输高速数字信号、模拟信号、直流电源等多类型信号。Pogo Pin主要由针头、外管、弹簧三大基本部件构成。

Pogo Block设计示意图如图14所示。

图14 Pogo Block设计示意图

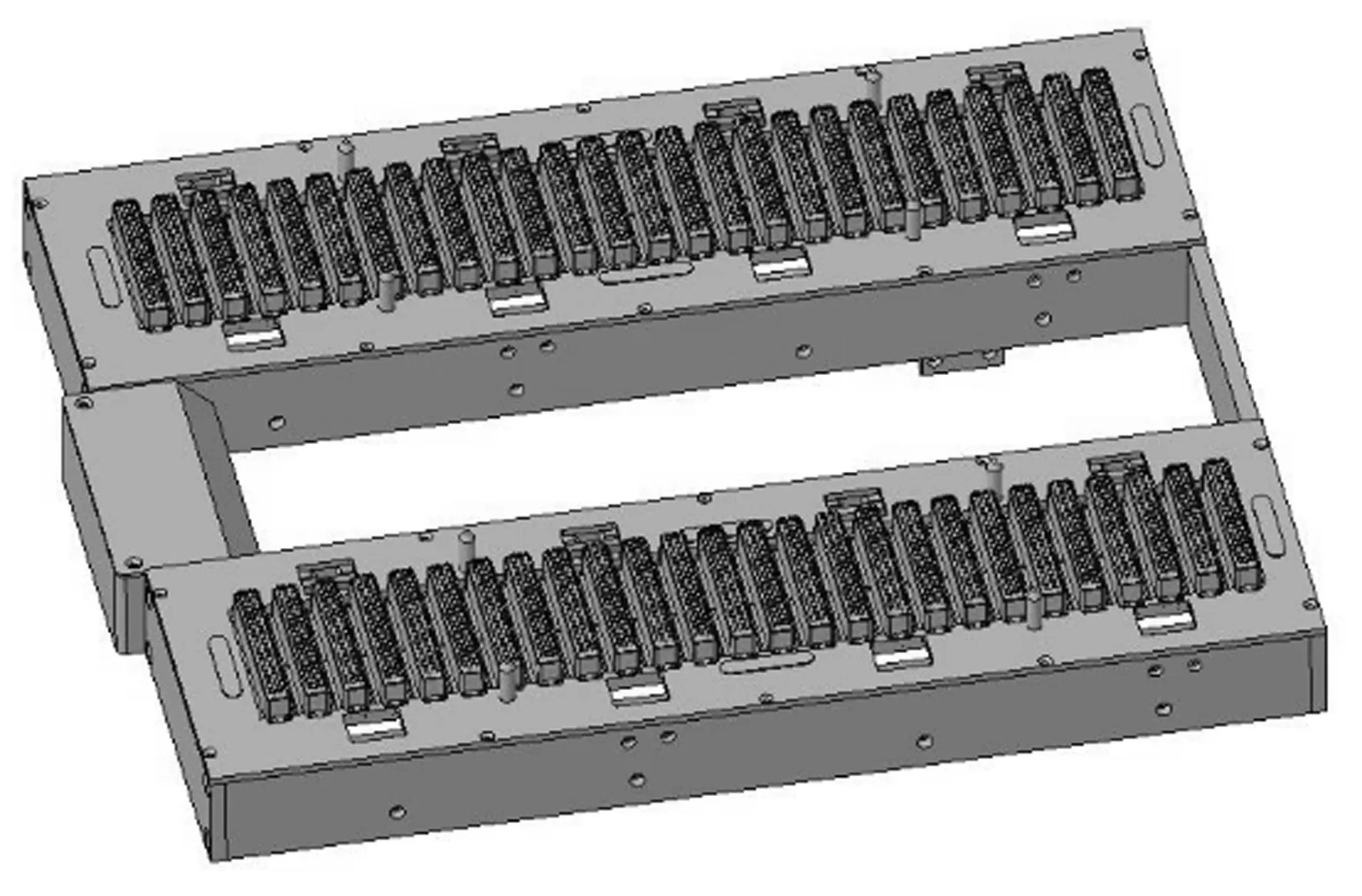

Pogo Block安装结构命名为Housing(安装外框/支架)。Pogo Block上加工导向筋等类似结构,与Housing上的导向槽相配合,保证所有仪表的Pogo Pin的高度保持一致;Pogo Block安装在Housing上后,Pogo Pin垂直于Housing水平面,确保在对接过程中无水平方向位移。Pogo Block与Housing安装示意图如图15所示。

图15 Pogo Block的housing示意图

4 指标测试与分析

4.1 软件接口测试与分析

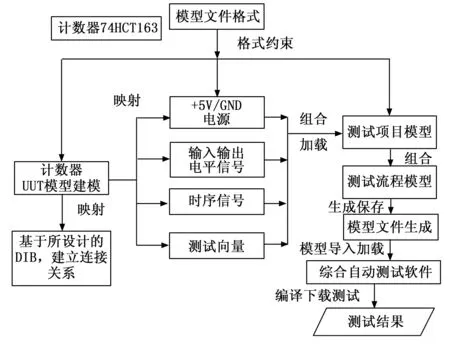

采用74系列计数器74HCT163,开展软件接口测试。在模型格式文件的约束下,建立74HCT163的UUT模型,并基于所研制的DIB,建立连接关系模型。基于UUT模型和连接关系模型,依次完成电源、电平信号模型、时序关系模型和测试向量,将模型进行组合后,进一步生成测试项目模型,按照不同的测试场景,组合为测试流程,采用XML格式保存。其建模过程如图16所示。

图16 测试模型建模与验证过程示意图

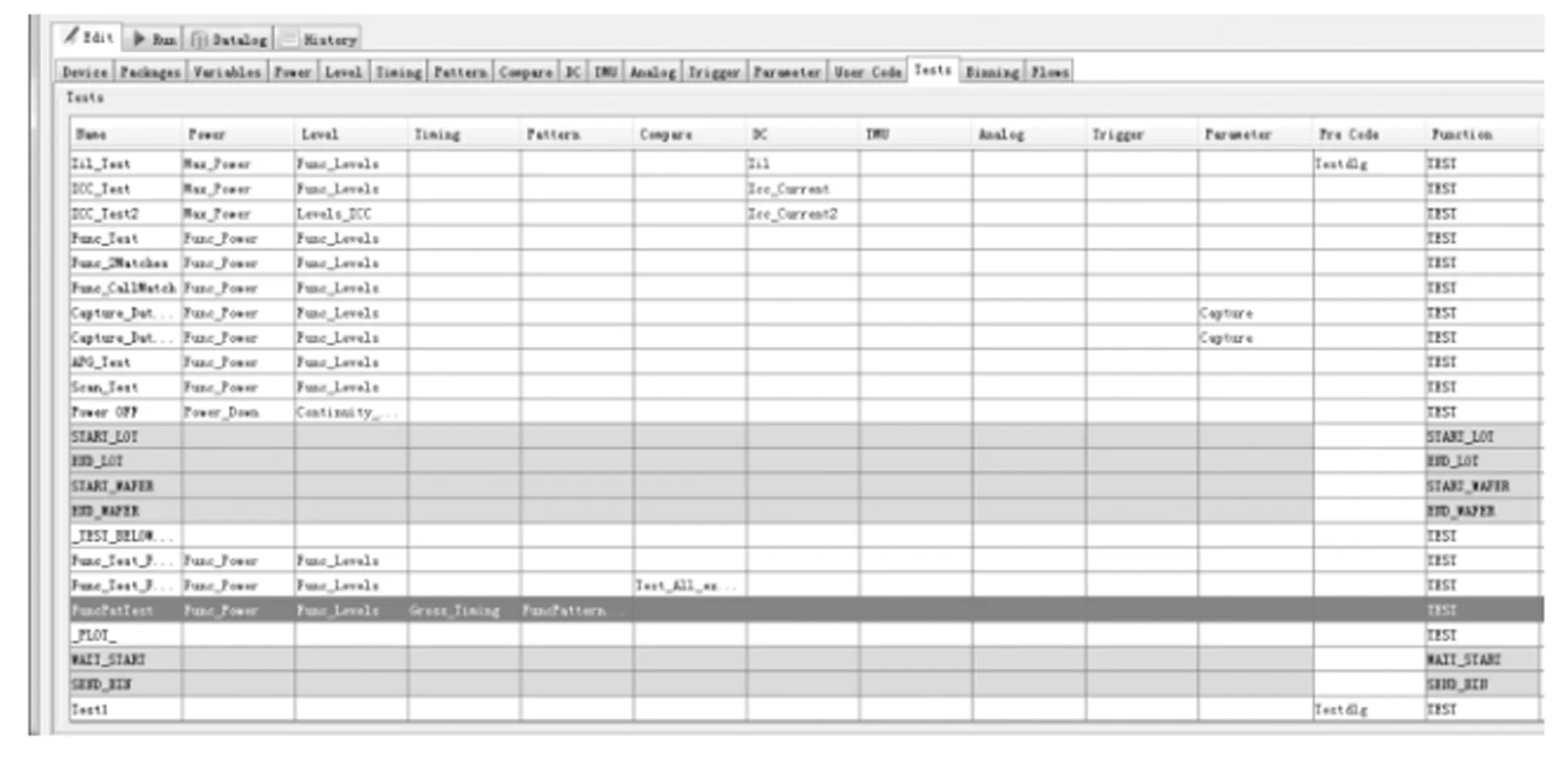

为验证接口,在综合自动测试软件中导入该XML文件,所生成的测试程序中的功能测试流程项目截图如图17所示。

图17 模型导入解析后生成的功能测试流程

对所生成测试程序,通过编译下载,即可加载到测试运行界面。各测试项目、部分DC参数的运行结果如图18所示。

通过查看测试流程的执行结果,该芯片的连接性测试、DC参数测试(输入电流、输出高电压、输出低电压等)、AC参数测试(延迟时间等)均能通过测试,满足器件要求。

通过1)导入XML文件生成测试流程、2)对测试流程的编译下载和执行、3)实际查看对比分析测试流程执行结果等三步操作,验证了软件接口符合预期设计要求,具有较好的可移植性和兼容性。

4.2 硬件接口测试与分析

首先进行Pogo Block结构安装一致性测试。基于高精度图像尺寸测量仪,将所需要的测试尺寸参数、基准测量点坐标输入到测试软件中,在保证良好接地的情况下,测试Pogo Block各个行列中各个的Pogo Pin与基准点的距离。部分测试数据如表1所示。

经测试,距离偏差数据均小于0.1 mm,满足设计要求和实际使用要求。

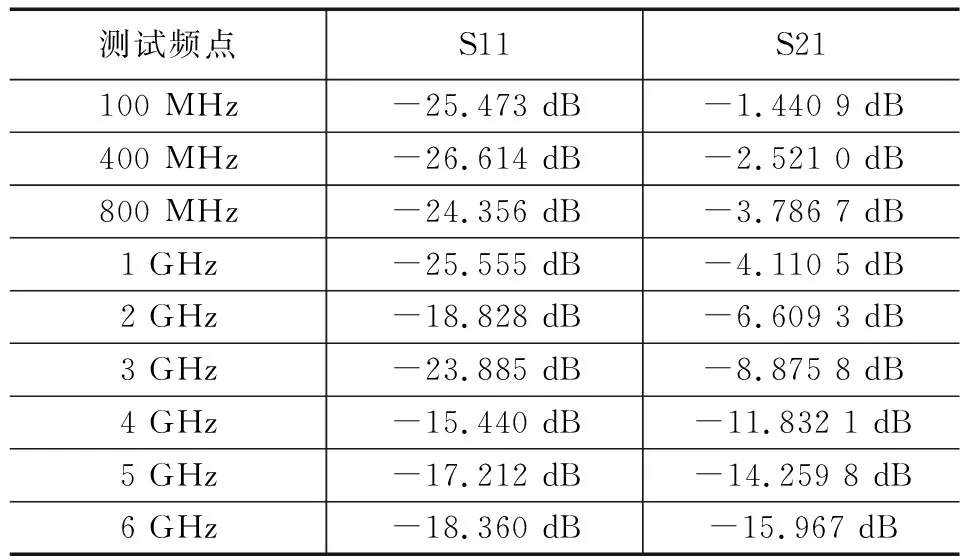

其次开展电气参数测试。主要使用矢量网络分析仪,基于专门设计的信号测试板,测试Pogo Block性能是否满足测试信号的需要。测试时通过信号线连接测试,主要测试网络信号的S11,S21参数。部分测试数据如表2所示。

表2 部分Pogo Block电气特性测试数据

分析测试数据表明,S11为-23.885 dB @3 GHz,S21为-8.875 8 dB @3 GHz,均满足设计要求,满足最高1.6 Gbps数字信号等的传递要求。

5 结束语

本文主要介绍了国产超大规模集成电路综合自动测试系统软硬件平台的测试接口。其中软件平台接口主要采用基于模型的方法,构建可导入、具备一定通用性的测试模型,主要针对当前随着被测对象的规模越来越庞大、测试程序之间不能互相移植问题,并采用存储器、计数器等芯片对测试模型建模过程进行了说明和验证。硬件平台接口主要实现装有被测集成电路芯片的测试接口板与测试头的连接,满足测试仪器与测试对象之间的信号传递关系,采用测试对接锁紧装置实现测试接口板的安装锁紧,采用Pogo Block实现电气信号传递,通过测试,作为硬件平台接口核心的Pogo Block的连接器引脚的偏差小于0.1 mm,电气特征可满足最高1.6 Gbps高速数字信号等的传递要求。未来进一步工程化设计后,本系统将可广泛应用在集成电路的设计验证、量产测试和筛选测试等环节,满足国产集成电路测试需要。