毫米波功率合成技术及三维堆叠封装

朱啸宇,干书剑,赵 超,王培阳,王志奎

(中国航天科工集团8511 研究所,江苏 南京 210007)

0 引言

毫米波技术在通信和雷达领域应用越来越广泛,但毫米波源较低的输出功率制约了其发展,将多个毫米波信号进行功率合成的技术是提高功率的有效技术途径。功率合成技术发展至今,通常采用Lange 电桥[1]和功分器2 种器件实现。Lange 电桥的尺寸和频率相关,毫米波段的Lange 桥尺寸小,需增加过渡微带才能与放大器芯片端口匹配,增加了装配的难度,导致传输损耗和端口驻波恶化。

功分器的形式有很多种,其中基片集成波导[2](SIW)形式的功分器较为适合平面集成、大功率合成和毫米波频段的应用。但是传统的SIW 功分器以PCB 工艺平台为主,大多采用微波介质板或环氧树脂介质为基板,尺寸较大,加工精度较低,不易与功率放大器芯片进行小型化集成。 微机电系统[3](MEMS)作为目前实现器件小型化、高加工精度和高集成度的主要工艺之一,可以弥补传统SIW 功分器的不足。近年来,已有学者利用MEMS 工艺设计出微同轴宽带功分器和太赫兹波导功分器,但是同轴结构和波导结构与芯片互联难度较大,不利于集成度的提高。

因此本文结合MEMS 工艺和SIW 结构,设计了一种硅基SIW 功率合成器和三维堆叠封装,易与芯片互联,兼具了小型化、大功率容量、高加工精度和高集成度等优势。并制作了一款33~37 GHz 的功率合成器和三维堆叠封装,通过软件仿真和实测验证了毫米波功率合成和三维堆叠封装的可行性。

1 功率合成器的设计与测试

1.1 功率合成器的选用

功率合成技术的主要性能指标为合成效率,合成效率定义为:式中,Po为功率合成后输出功率,Pi为功率放大单元输出功率总和。

影响合成效率的因素主要有合成路径引入的损耗、幅度相位的一致性和不同路径的隔离度等。此外进行功率合成时,功率放大器芯片的热量较为集中,需考虑散热设计,以保证放大器芯片的性能和可靠性。

在毫米波段,趋肤效应较明显,平面型功率合成电路传输损耗较大,而波导合成电路尺寸偏大,选用SIW形式的合成网络,既可以保证低传输损耗、高功率传输,又可以缩小尺寸,并且端口位置可根据不同放大器尺寸灵活变动,与芯片可用金丝互联,易于集成。

为了保证每一路合成路径的一致性,需要高加工精度的平台作为保障。选用MEMS 工艺平台,以硅为传输介质,采用高深宽比TSV[4]刻蚀技术,实现密集TSV 孔以等效金属壁;线宽和线间距最小可达10 µm。加工精度误差为微米级,可满足一致性的要求。

不同路径之间需保证较高的隔离度,通过增加隔离电阻可有效提升隔离度。MEMS 工艺通过先在硅晶圆表面形成一层氧化硅和氮化硅的复合介质,随后在需要加电阻区域的介质上溅射一层金属钽,最后在金属层两端镀金,形成电阻层。电阻尺寸为微米级,厚度为埃米级,可忽略不计。对比常规功分器将贴片电阻作为隔离电阻的方式[5],极大地缩小电阻尺寸,并且无需电子装配工艺,简化工艺流程。

综上所述,基于MEMS 工艺的SIW 功分器可以提高毫米波频段的合成效率。

1.2 硅基SIW 功分器的设计

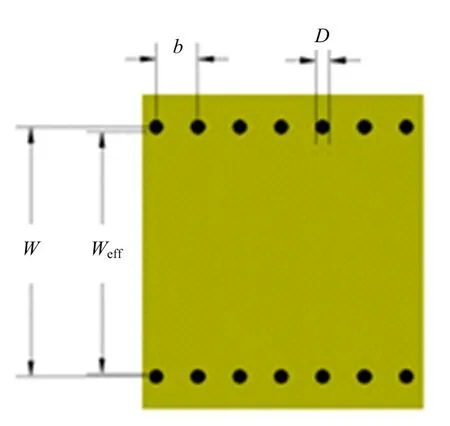

基片集成波导是通过介质中2 排密集排布的金属化孔等效成电壁,结合介质上下2 个金属化面等效为波导结构。结构示意图如图1 所示。Weff为等效为金属波导时的宽度。由文献[6]的理论计算可知:

图1 基片集成波导结构示意图

从而可以根据金属波导中的公式推导出SIW 中的TE10模的截止频率fTE10:

式中,c为真空中光速,εr为介质的相对介电常数。为了防止高次模的干扰,保证只有TE10一种模式可以被传播,设计时还需要保证:

硅基SIW 功分器的介质基板采用200 µm 厚度的硅基板,相对介电常数εr为11.9,TSV 孔径30 µm。工作频率为33~37 GHz,功分器结构示意图如图2 所示。输入和输出端口将SIW 的类波导传输形式过渡为共面波导的传输形式,硅基板厚度与芯片厚度相差较小,可使用金丝进行互联;功分器顶部开槽以减少插入损耗;引入隔离电阻提高端口间隔离度。端口特性阻抗均为50 Ω,通过理论推导得到W1=0.13 mm,W2=0.53 mm,W3=1.96 mm。

图2 SIW 功分器示意图

1.3 SIW 功分器仿真和测试

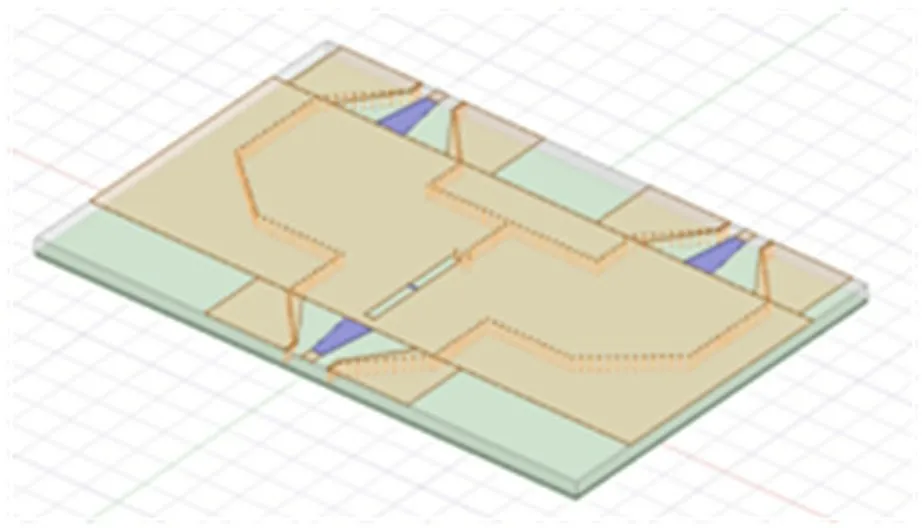

为了验证上述设计方法,对频率为33~37 GHz 的功分器进行仿真。图3 为SIW 仿真优化后的模型示意图,外形尺寸为5.4 mm×6.6 mm×0.2 mm。表1 为优化后的尺寸参数。

表1 优化后参数的尺寸

图3 功分器仿真模型示意图

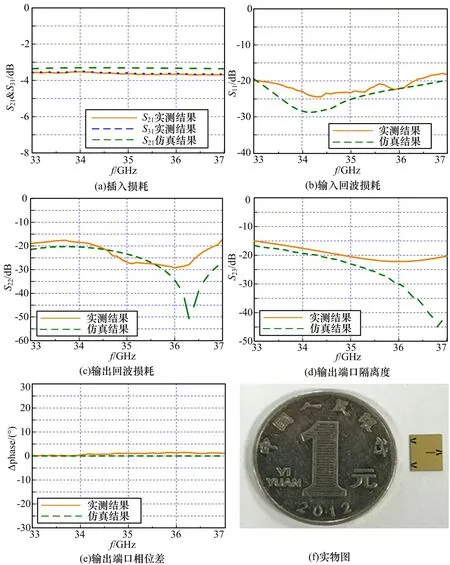

图4描述了仿真和实测结果的对比图以及实物图,实验使用矢量网络分析仪以及探针台进行测试。图4(a)—(e)从对比结果可以看出,仿真结果和实测结果基本吻合。在33~37 GHz 内,实测结果中插入损耗S21在3.5 dB 左右,即单路损耗为0.5 dB;隔离度S23小于-15 dB,在35~37 GHz均小于-20 dB;输入输出回波损耗S11、S22全频段小于-20 dB;不同路径同一频点下的幅度差别小于0.1 dB,相位差不超过1.5°。图4(f)给出了SIW 功分器的实物图。

图4 SIW 功分器 :(a)—(e)仿真与实测对比图;(f)实物图

通过分析,与仿真结果的偏差主要原因是探针台测试时需用砷化镓微带转接探针,砷化镓微带和功分器用金丝键合互联,金丝在毫米波段引入的电感效应较强,容易影响各端口的匹配和引入损耗。

2 三维堆叠封装的设计和测试

2.1 功率合成三维堆叠封装设计

为了方便功分器的工程应用,将功率放大器芯片与功分器进行集成和封装是一个有效途径。载板式封装是实现器件集成最为简单的形式,即将功分器和放大器芯片烧结至金属载板上,后续使用时将载板烧结至组件内即可。

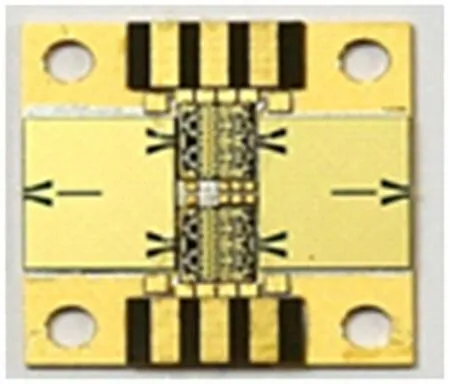

本文选用的功率放大器芯片为氮化镓芯片,平均线膨胀系数约为5.6×10-6/℃,工作频率33~37 GHz,饱和输出功率41 dBm,附加效率约为30%。若工作条件为脉冲工作,占空比10%,周期1 ms,峰值热耗约为30 W,平均热耗3 W。综上考虑,本文选用钼铜(Mo80-Cu)作为金属载板材料,钼铜平均线膨胀系数约为6.8×10-6/℃,热导率约为170 W/(m·K),与芯片热膨胀系数相近,且导热能力较好。将功分器、功率放大器芯片、芯片电容和微带采用金锡焊料烧结和导电胶粘接的形式安装至钼铜载板上。载板可采用烧结或螺丝固定的方式安装至组件上进行应用。实物图如图5 所示。

图5 功率合成载板式封装

装配过程中由于器件较多,尺寸较大,导致装配难度较大,效率低,一致性差等问题。为了提高生产效率和一致性,实现气密封装,方便工程应用,本文基于MEMS 工艺平台,利用TSV 转接板、晶圆级键合[7]技术,提出了功率合成的三维堆叠封装的设计。

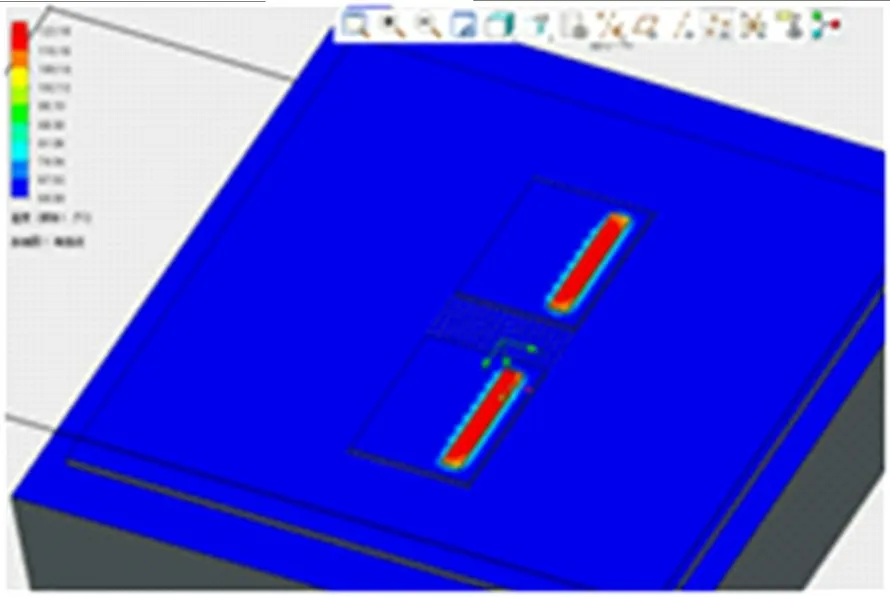

硅的热导率约为150 W/(m·K),硅的平均线膨胀系数约为4.1×10-6/℃,与氮化镓芯片匹配,根据功率合成的实际情况对其进行热仿真。考虑余量设计,单个放大器芯片平均功耗设置为7 W,热量集中在功放芯片的末级管芯处,环境温度设置为60 ℃,仿真结果如图6 所示。由仿真结果可知,芯片结温为123 ℃,远低于氮化镓芯片的极限结温。因此硅可作为功率放大器底部热沉,满足散热需求,保证放大器芯片的性能和可靠性。

图6 硅载板热仿真结果

由于材料相同,将SIW 功分器沉入硅载板,实现一体化设计,省去了功分器装配的步骤;采用晶圆级键合技术,可以大幅提高生产效率和产品的一致性;设计TSV 转接板和硅帽,采用2 次晶圆级键合,实现三维封装的气密性;通过刻蚀工艺形成硅帽,对硅帽内表面进行金属化,与底部载板构成封闭金属腔体,提高电磁屏蔽能力。功率合成的三维堆叠封装示意图如图7 所示。

TSV 转接板示意图如图8 所示。在与硅帽的焊接区域附近用TSV 孔将放大器的馈电走线从转接板上表面过渡到下表面,从而避开焊接区域。

图8 馈电线和焊接框示意图

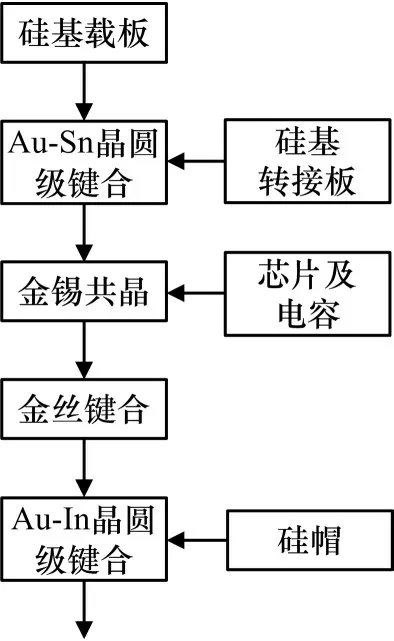

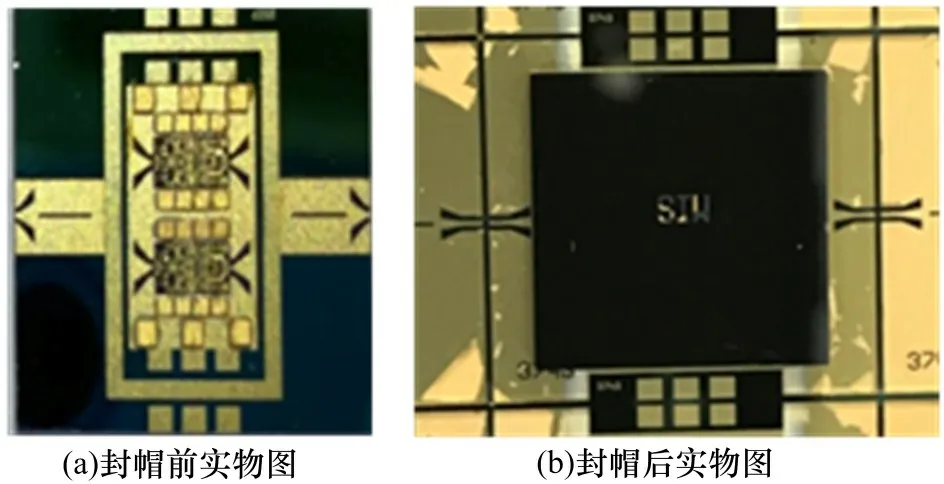

晶圆级键合技术是在较低的温度下,利用低熔点金属与难熔金属之间的化学反应形成更高熔点的金属间化合物的技术,即键合后的金属化合物的熔点高于键合温度,从而实现共晶键合和气密效果。功率放大器的装配工艺采用金锡焊料共晶的形式,烧结温度在290 ℃左右,因此底板和转接板之间采用低温共晶键合常用的金属体系Au-Sn,保证在功率放大器装配过程中载板和转接板的焊料不会出现重熔。盖帽和转接板之间采用共晶温度更低的Au-In 金属体系进行键合。功率合成的三维堆叠封装的工艺流程如图9 所示。三维堆叠封装实物图如图10 所示。

图9 三维堆叠封装的工艺流程

图10 三维堆叠封装实物图

2.2 功率合成三维堆叠封装测试

为了验证三维堆叠封装的射频性能和可行性,使用信号源和功率计对其进行了测试。实验测试条件为工作周期1 ms,占空比10%。图11 为饱和输出功率曲线图。

图11 功率合成实测数据曲线图

功率放大器芯片合成后的饱和输出功率均在43 dBm 以上,输出端损耗约为1 dB,合成效率约为80%。考虑测试架引入的传输损耗,实验结果与功分器单测数据是比较吻合的。实验说明该功率合成技术完全适用于毫米波段的大功率合成应用。

3 结束语

本文从毫米波段功率合成的影响因素出发,提出了一种低传输损耗、高功率、高隔离度、高通道一致性的功率合成技术,端口可根据芯片调整,适用大多数功率放大器芯片的合成;设计了一种三维堆叠功率合成封装,具有气密、散热性好、集成度高、装配效率高、装配一致性好等优点,可以广泛应用在毫米波频段和更高频率的大功率合成中。■