基于SPICE模型的运算放大器ESD故障机制分析

史如新,嵇建飞,张伟

(1.国网江苏省电力有限公司常州供电分公司,常州 213000;2.国网江苏省电力有限公司电力科学研究院,南京 210094)

引言

智能电网是一个综合各种技术的电力工程,其运行过程中产生的电磁场和射频干扰导致集成电路的工作环境差,运算放大器的高故障率,给电网的安全稳定运行带来危险[1,2]。

瞬态干扰通过传导耦合和辐射耦合进入运算放大器的MOS管中,导致工作电压偏移。当能量过大或偏移超过安全临界值时,集成电路容易发生击穿或故障,最终影响系统的安全运行[3,4]。

在文献[5]中,基于黑盒建模方法,建立了集成电路的静电放电(ESD)干扰模型,研究了智能电力设备的瞬态干扰行为和物理结构的抗干扰能力,实现了对电力设备ESD鲁棒性的准确预测。在文献[6-8]中,设计了带有瞬态脉冲和瞬态电压检测的ESD钳位电路,验证了具有12 V双扩散漏源MOS器件的高压CMOS工作过程,揭示了CMOS的ESD干扰特性。

随着半导体行业发展,半导体沟道长度不断减少,集成电路晶体管制造尺寸也越来越小,芯片单位面积内集成晶体管数目不断增多,芯片密度增大,核心电压大幅降低,时钟频率不断增高,导致芯片对系统内部模块间的干扰越来越敏感[9]。根据天线理论,信号线尺寸在1/4波长时,将产生天线效应,而在高频(3~30)GHz情况下,芯片管脚、封装尺寸很容易到达这个长度,甚至内部键合线的尺寸也接近1/4波长。在这种情况下,集成电路上的高频干扰源易通过这些线路耦合到芯片内部,对芯片工作产生影响[10]。

静电放电(Electrostatic Discharge,ESD)作为一种强脉冲干扰,对我国军事装备、航空航天、卫星通信、智能制造等关键领域的发展产生了阻碍[11]。根据半导体行业相关失效数据分析的统计,ESD造成损害成本每年高达数十亿美元。ESD/EOS(Electrical Over Stres,电气过应力)导致集成电路失效占总体失效比例的37 %,是集成电路失效的主要因素[12]。由于集成电路ESD防护窗口的设计会随着集成电路制造工艺提升而不断减小,导致ESD防护也越来越困难,需定制专门的ESD防护方案,因此相应设计成本也会增加[13]。

上述研究都研究了ESD对MOS管的影响,但是这些研究仅关注单个晶体管的工作特性,而实际上集成电路由多个晶体管组成。由于ESD的影响,现有的研究无法确定具体的故障晶体管。本文提出了一种基于SPICE模型分析运算放大器MOS故障机制的方法,可以准确定位导致集成电路失效的晶体管。

2 运算放器的ESD效应分析

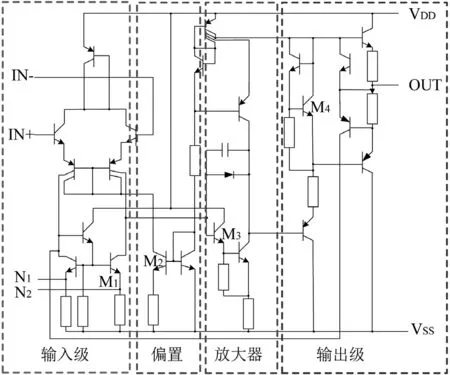

如图1所示,UA741的有源元件主要是非线性晶体管。本文以NMOS为例,研究了ESD干扰对NMOS工作特性的影响。

图1 UA741运算放大器的内部结构

根据跨导的定义,NMOS的栅源电压Ugs为:

式中:

Uth—阈值电压;

W—沟道宽度;

L—沟道长度;

μ—电子迁移率;

Cox—氧化层电容;

IDD和IESD—供应电流和干扰电流。

输入电流Iin为:

假设峰值瞬态干扰电流与电源电流之比为λ:

根据式(2)和式(3)

根据式(1)和式(4)

可以得到式(5)和式(6)的泰勒展开式:

通过对式(6)进行积分,可以得到栅源平均电压,即电压的直流(DC)分量。

从(7)式可以看出,ESD干扰降低了栅源的直流电压并引起偏移。由于晶体管的非线性特性,在MOS没有任何直流分量的情况下被激励时,晶体管的直流工作点会大幅偏移。

3 基于SPICE模型的MOS故障机理

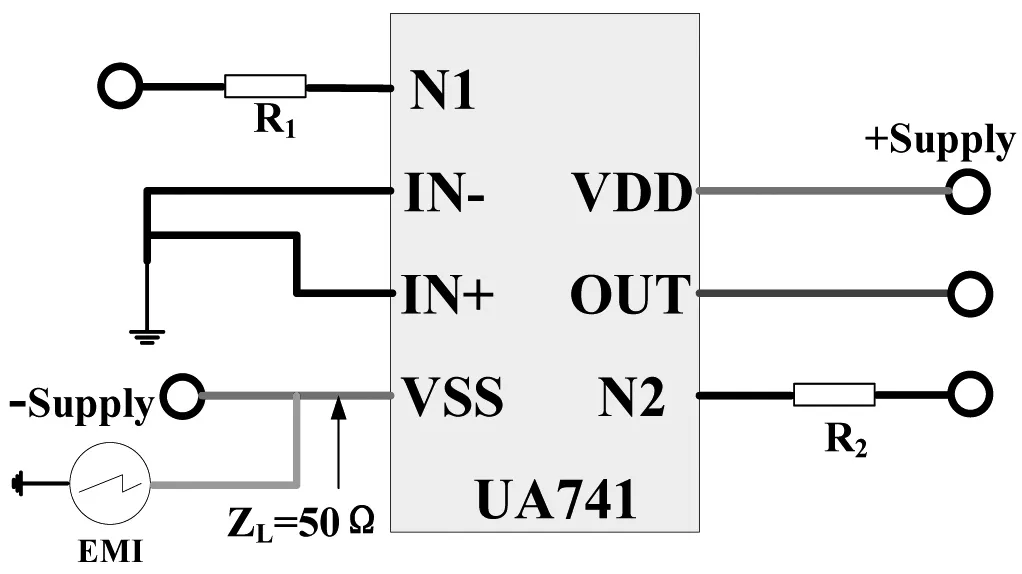

ESD脉冲的负极性模式如图2所示,UA741运算放大器的VDD和VSS引脚连接到正常工作电源,差分输入引脚IN-和IN+接地,N1和N2连接到零电压以确保在没有输入时输出为零,而瞬态脉冲则通过VSS引脚注入。

图2 UA741在负模式下的ESD干扰

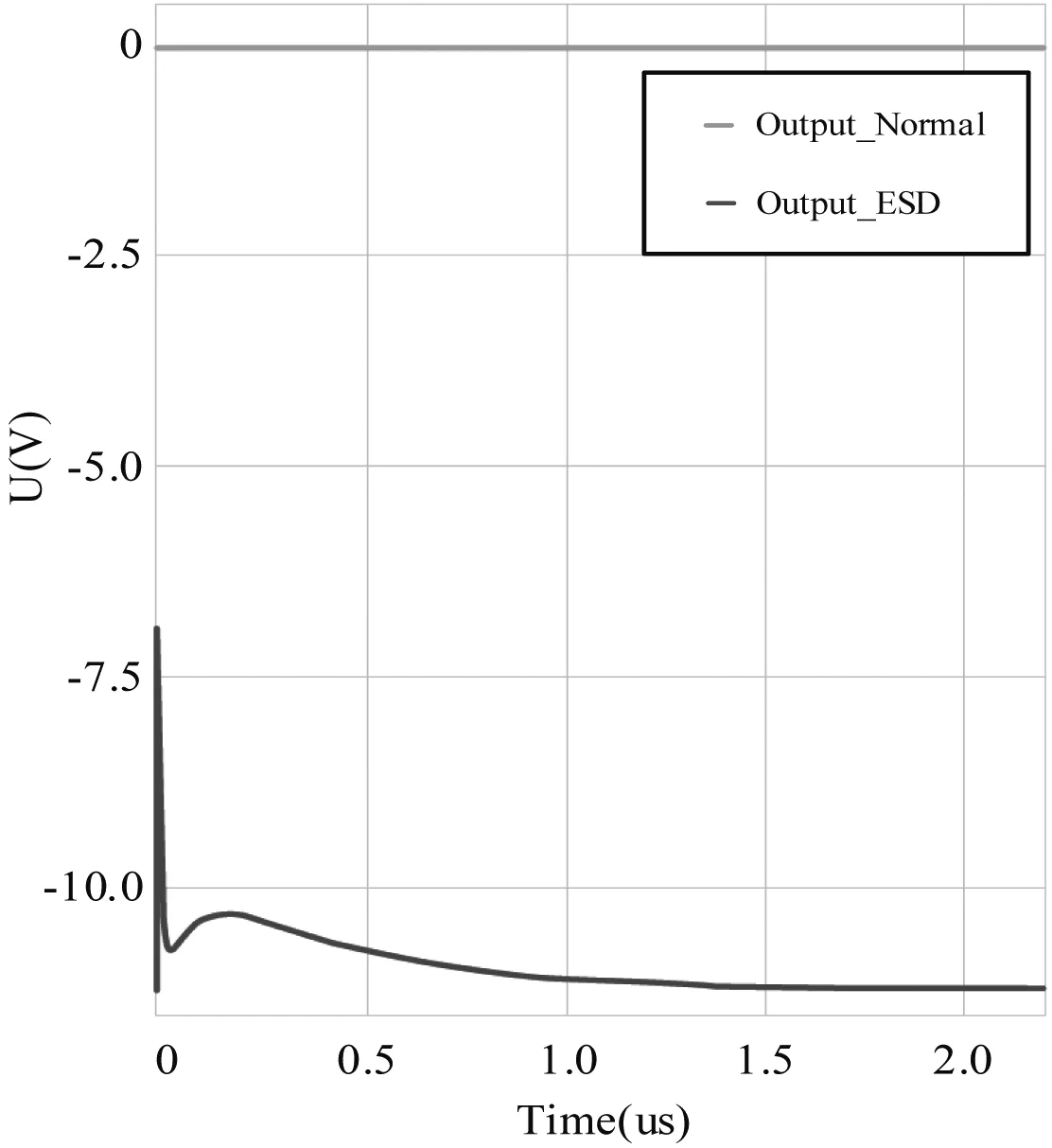

从图3可以看出,输出端口受到高幅值的ESD电压耦合,波形类似ESD脉冲。2 μs后,ESD脉冲消失,稳定的输出电压为-11 V,与正常输出电压相差11 V,工作状态异常。

图3 UA741的输出电压

根据故障理论分析,研究了图1中M1、M2、M3和M4端口的电压和电流特性,并确定了导致UA741运放失效的MOS晶体管。

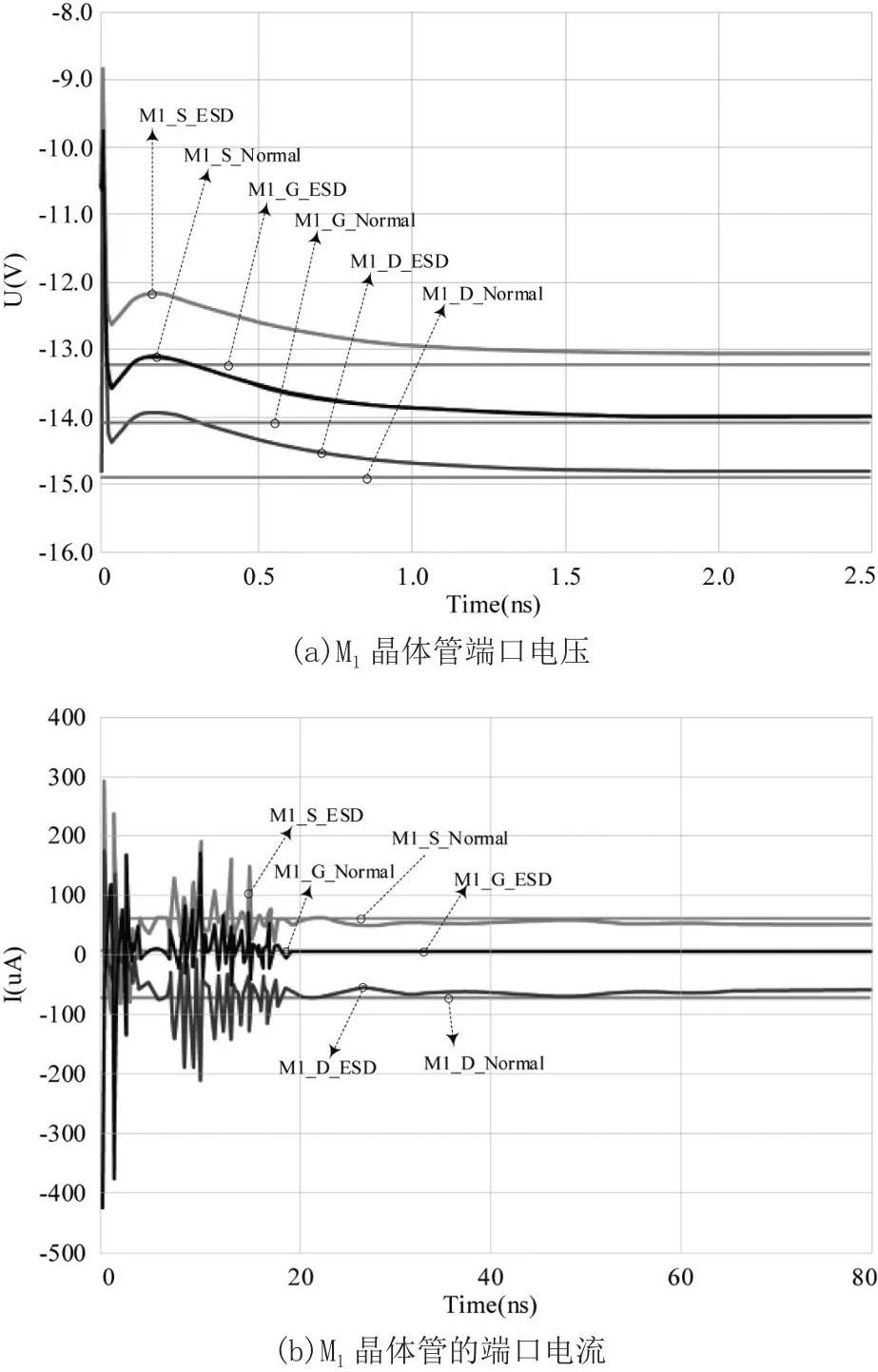

从图4可以看出,M1的源、栅和漏极电压都受到ESD脉冲的耦合,最大值分别为-8.8 V、-9.7 V和-10.5 V。M1的源、栅和漏极电流发生剧烈变化,产生高频噪声,其中栅极电流变化最大,最小达到-384 μA,远低于正常工作状态下的8.3 μA。虽然端口电压和电流在20 ns后回到正常工作状态,但电压和电流的幅值变化很大,M1容易出现反向电压。

图4 M1晶体管的端口电压和电流特性

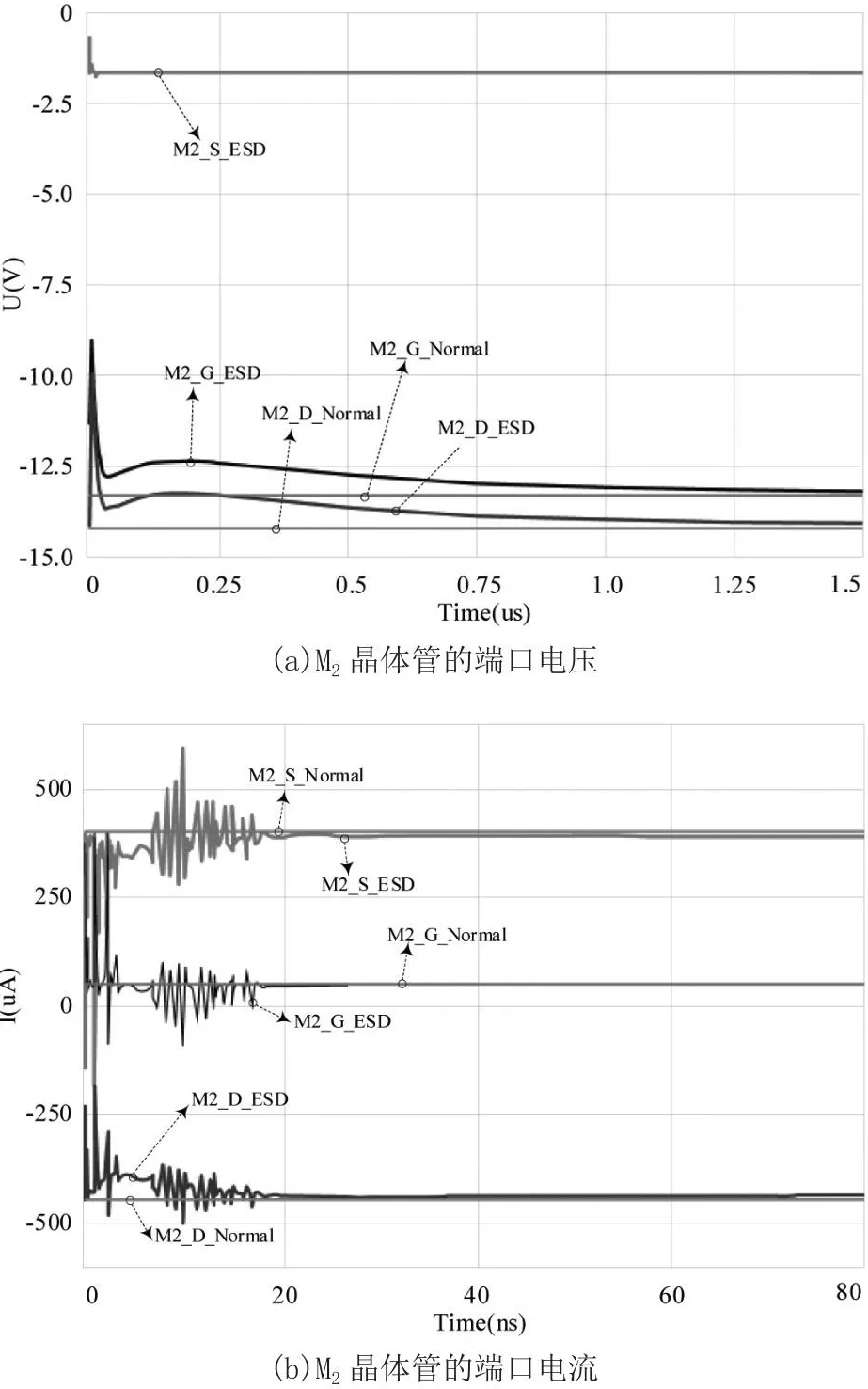

如图5所示,M2的源电压受ESD的影响较小,而栅极和漏极电压受到的影响较大,两者都与ESD脉冲耦合,最大值分别为-8.6 V和-10 V。M2的源电流变化最为剧烈,最小值为-197 μA,最大值为596 μA,严重偏离了398 μA的正常工作电流。虽然端口电压和电流在20 ns后恢复到正常工作状态,但是电压和电流的振幅变化很大,M2容易出现反向电压。

图5 M2晶体管的端口电压和电流特性

从图6可以看出,M3的源电压具有非常大的工作电压偏移量。ESD脉冲消失后,源电压从-835 mV的正常工作电压降至-12 V。此外,从图6(b)可以看出,M3的源漏电流偏离了正常工作电流,ESD消失后未能恢复正常。电压和电流的两个特性都表明,M3晶体管已经损坏。

图6 M3晶体管的端口电压和电流特性

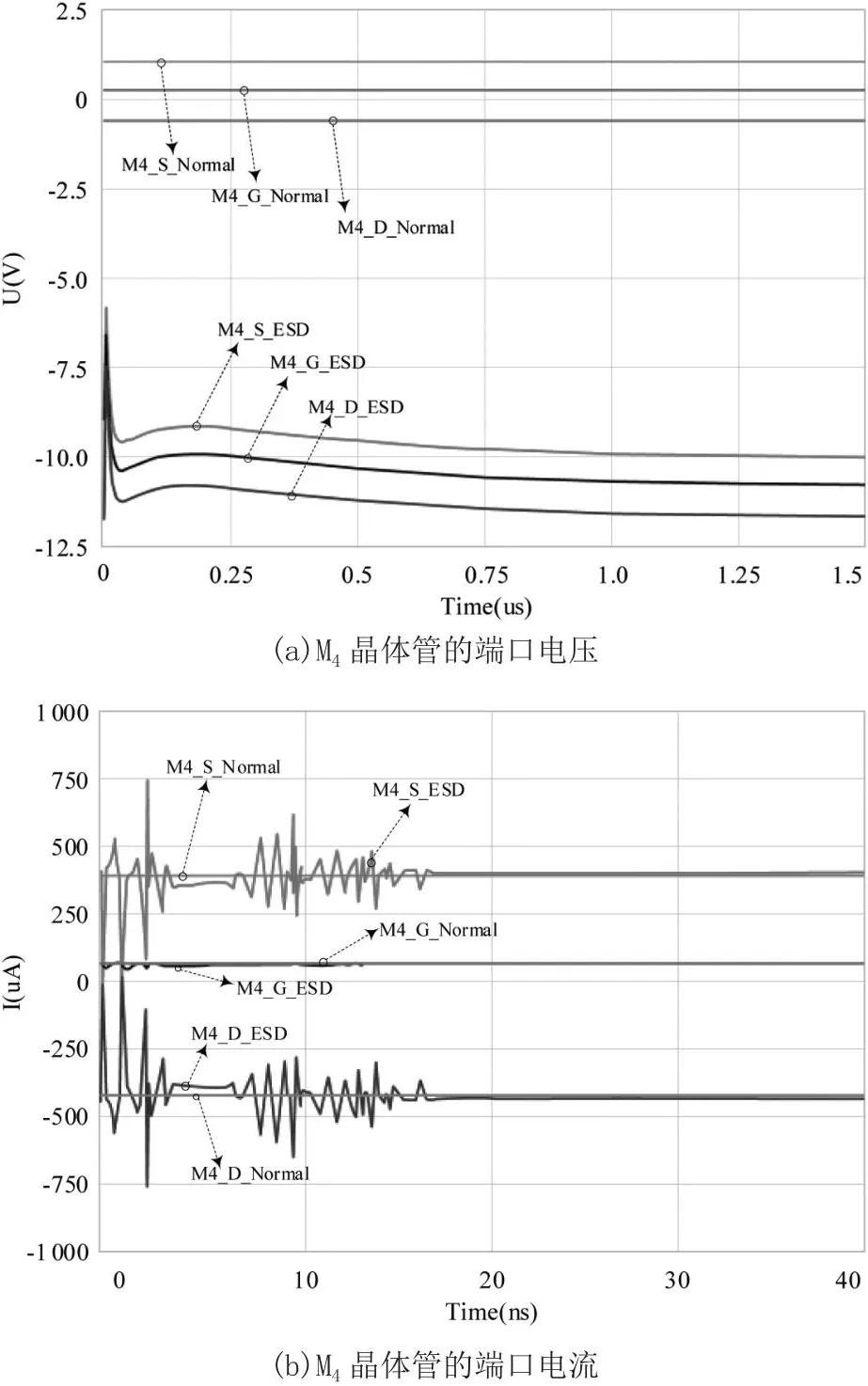

从图7可以看出,M4的源极、栅极和漏极电压都经历了相当大的工作电压偏移,在ESD脉冲消失后仍未恢复正常。此外,从图7(b)可以看出,M4的源漏电流与正常工作电流相差很大,但在ESD消失后恢复正常。电压特性结果表明M4晶体管已经损坏。

图7 M4晶体管的端口电压和电流特性

4 结论

本文提出了一种基于SPICE模型研究模拟运算放大器故障机制的方法。研究了ESD造成MOS晶体管工作电压偏移的理论,并影响集成电路的正常运行。UA741 ESD特性的仿真验证了内部MOS工作电压偏移是UA741故障的根本原因,并确定了故障晶体管位于放大器级M3和输出级M4。本文为精确定位集成电路的故障点提供了参考,并为有针对性的瞬态干扰抑制提供了理论基础。通过本文的研究,我们深入了解了ESD对运算放大器的影响及其故障机制,为进一步研究ESD抑制提供了有价值的参考。我们提出的一种基于SPICE模型的方法来研究运算放大器的故障机制,该方法可以帮助我们更准确地定位故障点,提高集成电路的可靠性。我们的研究不仅有助于提高智能电网电路和电力设备的安全性和稳定性,也对其他领域的电路和电子设备的可靠性提供了参考价值。在未来的研究中,我们将进一步探究ESD抑制的方法,并优化电路设计以提高抗ESD干扰的能力。