异质外延单晶金刚石及其相关电子器件的研究进展

陈根强,赵浠翔,于众成,李 政,魏 强,林 芳,王宏兴

(1.西安交通大学,电子物理与器件教育部重点实验室,西安 710049;2.西安交通大学电子与信息学部,宽禁带半导体与量子器件研究所,西安 710049)

0 引 言

宽禁带半导体材料和器件在信息、能源、交通、国防等领域有着诸多应用,已成为当前世界各国高技术竞争的关键领域之一,也是我国的高技术和战略性新兴产业。如表1所示,与GaN、SiC、Ga2O3等半导体材料相比,单晶金刚石具有大的禁带宽度(5.47 eV)、高的载流子迁移率[空穴(h)迁移率为3 800 cm2·V-1·s-1,电子(e)迁移率为4 500 cm2·V-1·s-1]、高的热导率,以及大的Baliga、Johnson和Keyes品质因子(figure of merit),非常适合制备大功率[1]、高频电子器件[2-4]。

表1 宽禁带半导体材料性质对比Table 1 Properties comparison of wide-band gap semiconductors

天然的金刚石极其稀少,且尺寸小,杂质多,一般仅用于珠宝首饰制作,基本不可能应用在电子器件领域。目前的单晶金刚石的制备方法主要有高温高压(high temperature high pressure, HTHP)法和化学气相沉积(chemical vapor deposition, CVD)法[5]。通过HTHP法制备出的单晶金刚石一般含有较多的杂质和缺陷,导致其无法应用在一些高新技术产业领域。相对地,CVD法是利用含碳的气体如甲烷、二氧化碳、乙醇等和氢气(H2)作为前驱体来合成金刚石。而如今的微波等离子体化学气相沉积(microwave plasma chemical vapor deposition, MPCVD)法具有生长速率快,制备出的金刚石杂质含量少等优点,成为了高质量单晶金刚石制备的主流方法。但目前可获得单晶金刚石晶种的尺寸较小,使得金刚石的发展和应用受到了极大的限制。然而,要广泛地用于电子器件的研制,制备大面积单晶金刚石至关重要。

从衬底选择上可以将MPCVD法制备大面积单晶金刚石分为同质外延和异质外延两种方法。同质外延是以单晶金刚石为衬底,通过三维生长技术[6]、马赛克拼接技术[7]来获得大面积单晶。然而,三维生长技术生长周期长,可选择晶种面积有限,成本高,难以获得较大尺寸的单晶金刚石。马赛克拼接技术则是选取多个晶面取向完全一致的单晶金刚石晶种并将其拼接在一起,利用金刚石在生长过程中会侧向延伸的特点进行大面积单晶金刚石的制备。目前利用马赛克拼接技术可获得尺寸为40 mm×60 mm的单晶金刚石衬底[7]。但是由于晶种尺寸的限制以及在拼接缝处难以抑制的缺陷,使得马赛克拼接技术在制备更大面积的高质量单晶金刚石方面难度较大。

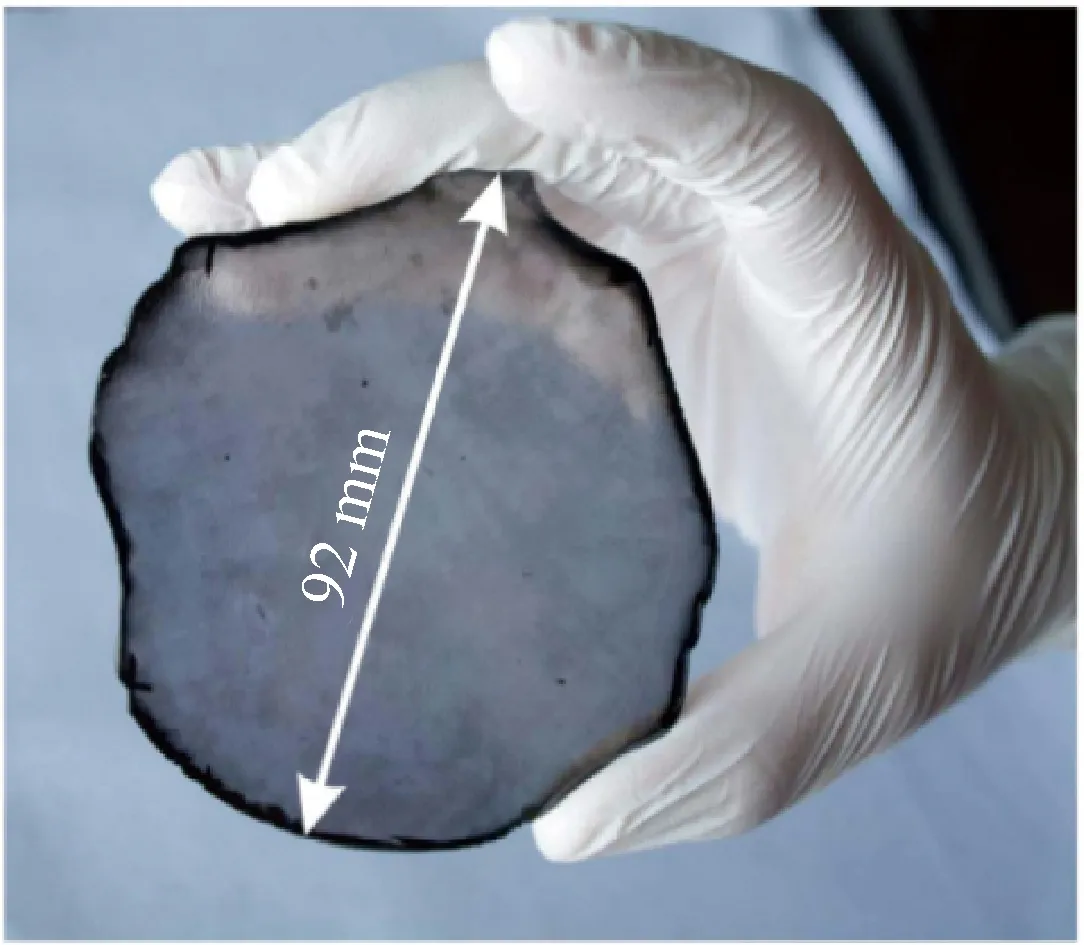

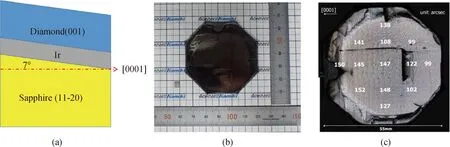

异质外延的外延材料与衬底材料不同。目前GaN的大尺寸单晶就是通过在一些低成本、大尺寸、高质量的衬底,如蓝宝石、Si等衬底上外延来获得,这大大地降低了GaN的生产成本,推动了其在电子器件领域的发展[8-9]。金刚石单晶异质外延技术历经多年发展,从起初的外延金刚石晶粒[10],到完整的异质外延单晶金刚石薄膜[11],直至现如今的近4英寸异质外延单晶金刚石衬底(见图1)[12],其晶体质量也在不断提升。而在异质外延单晶金刚石面积不断增大、质量不断提高的同时,基于异质外延单晶金刚石衬底的电子器件也在并行研究。这些成果都证明了异质外延的可行性,也加速了金刚石走向产业应用的步伐。

图1 当前最大尺寸的异质外延单晶金刚石衬底[12]Fig.1 The heteroepitaxial diamond substrate with maximum size to date[12]

因(100)面金刚石相比于其他晶面有着生长速率快、易加工研磨等优点而作为当前的主要研究对象,所以本文也着重介绍(100)面异质外延单晶金刚石。本文从金刚石异质外延的衬底选择、形核机理、最新研究进展等方面对异质外延单晶金刚石进行了介绍,也总结了异质外延单晶金刚石目前在电子器件领域的诸多进展,并在最后列举了目前金刚石研究所面临的几项挑战,对其发展前景进行了展望。

1 异质外延单晶金刚石

1.1 用于单晶金刚石异质外延生长的衬底选择

异质外延,即在非金刚石的单晶衬底上外延出单晶金刚石,所以首先要考虑的便是衬底的选择。考虑到MPCVD生长金刚石的腔体环境,所选择的衬底必须要满足以下条件:1)晶体质量高,具有相当高晶体质量的衬底是生长出高质量的单晶金刚石的必要条件;2)可以做到相当大的尺寸,异质外延的目的就是要获得大面积单晶金刚石;3)成本低,异质外延的另一目的就是为了降低金刚石生产成本;4)高熔点,金刚石生长温度基本都在800 ℃以上;5)与金刚石晶格失配小,这是外延高质量单晶的必要条件;6)热膨胀系数小,这是为了减小在高温下衬底和金刚石由于热膨胀所产生的应力;7)性质稳定,不与H、C等元素进行化学反应。在这些条件下,研究者们尝试在Si[13-14]、c-BN[15-16]、Pt[17]、Ni[18-19]、SiC[20-21]等不同的材料上进行金刚石的异质外延生长。实验结果发现,只有在Ir衬底上的金刚石薄膜具有与单晶类似的连续平滑形貌。Charlier等[22]经过模拟计算分析,认为原因一是Ir不和C发生化学反应,二是C原子在Ir中的溶析能对C的浓度十分敏感,当C原子浓度升高时,溶解在Ir中的C原子就会迅速析出,使衬底表面形貌快速变化,金刚石核在其表面旋转平移,形成一致取向。所以,直到目前,Ir都被认为是金刚石单晶异质外延的最优解。但由于金属Ir极其稀有,价格也十分昂贵,直接用Ir金属作为衬底进行外延生长需要很高的成本,所以会选择先在一些成本低、高熔点的单晶衬底上进行Ir薄膜的外延,然后再进行单晶金刚石的外延。目前所采用的复合衬底主要有Ir/MgO[23]、Ir/SrTiO3[24]、Ir/Al2O3[25]、Ir/Pd/Al2O3[26]。Ir薄膜可以通过脉冲激光沉积(pulsed laser deposition, PLD)[27]、磁控溅射[28-29]、电子束蒸发[30]、分子束外延[31]等方法外延生长在这些单晶衬底上。然而,MgO和SrTiO3与金刚石的热膨胀系数存在较大的差异,所以当达到适宜金刚石外延的温度时(大于900 ℃,图2中虚线所示),沉积在氧化物衬底上的金刚石薄膜内的应力就会高达-6~-10 GPa,如图2所示。此时金刚石薄膜在生长过程中就很容易碎裂或是从衬底上脱落下来[32]。Si和金刚石有着较为接近的热膨胀系数,故而在生长过程中只会产生很小的应力(-0.68 GPa),这比较利于获得较大面积和较厚的金刚石外延衬底[32]。然而,因为Ir和Si之间存在的化学反应,所以会在Ir和Si 衬底中间插入一层过渡层形成多层的衬底结构,如Ir/YSZ/Si[33]、Ir/SrTiO3/Si[34]。目前,Al2O3和Si衬底因为成本低、可获得大面积衬底、晶体质量高,以及与金刚石热失配相对较小的优点,成为了异质外延单晶金刚石的主流衬底。除此以外,研究者们也不断地在拓宽适合金刚石异质外延的衬底选择范围,如Ir/KTaO3[35]。

图2 不同衬底与沉积的金刚石之间的热应力-沉积温度变化关系[32]Fig.2 Comparison of the thermal stress versus deposition temperature for different substrates on which diamond is deposited[32]

1.2 金刚石形核及快速生长

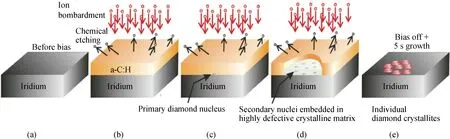

异质外延单晶金刚石通常包含两个阶段:先在Ir表面形成取向一致、排列整齐的岛状金刚石核;然后再进行快速生长,成为连续的单晶薄膜。为了获得高质量的单晶,就需要获得较高的形核密度。偏压增强形核(bias enhanced nucleation, BEN)被证明是一种获得较高形核密度的有效方法。其原理在于:1)给衬底加上负偏压后,增大等离子体球和衬底的接触面积,利于大面积的形核[36];2)离子在电场的作用下不断加速获得能量,从而提高形核密度和均匀性。BEN法的主要机理如图3所示。在BEN过程刚开始时,Ir表面首先生成一层非晶碳层(见图3(a)),在电场加速的作用下,被微波激发的碳离子源源不断地被注入到Ir的亚表面直至饱和,而当碳的浓度继续升高时,Ir亚表面的C原子就会析出形成初级金刚石核。初级金刚石核形成之后,通过C原子之间的相互作用力规范其周围的C原子,形成排列规则的金刚石核(见图3(c))。而在偏压关掉后以及金刚石快速生长过程开始的5~10 s 内,Ir表面的非晶碳便会在富氢的环境下被刻蚀掉。在形核过程中,金刚石成核密度随着甲烷浓度和偏压大小急剧变化,所以需要不断优化、精确形核条件,找到最佳条件窗口[37]。在金刚石的快速生长过程中,金刚石核变大并形成连续薄膜,且随着金刚石厚度的增加,其表面形貌、晶体质量都得到显著的提升[38]。

图3 金刚石BEN过程示意图[12]Fig.3 Schematic illustrating of diamond BEN process[12]

1.3 异质外延单晶金刚石晶体质量的改善

由于Ir和金刚石之间存在着较大的晶格失配(-7.1%),所以在金刚石异质外延生长过程中,Ir与金刚石界面会产生很多的位错,较高的位错密度极大地阻碍了异质外延单晶金刚石在电子领域内的应用。如何降低金刚石位错密度,成为了高质量异质外延单晶金刚石的一大挑战。

1.3.1 横向外延降低位错密度

横向外延(epitaxial lateral overgrowth, ELO)是一种有效降低晶体位错密度的方法。在金刚石横向生长过程中,位错被阻断,因为位错贯通方向和横向生长方向相垂直,位错无法在掩膜区向上延伸,从而提高了异质外延单晶金刚石的晶体质量。这种方法也常被用在GaN单晶异质外延上[39]。

1) BEN图形化衬底技术

在历经BEN工艺的衬底上,通过光刻、刻蚀、去胶工艺实现了Ir表面的金刚石核图形化,而后再通过ELO步骤获得异质外延单晶金刚石。

日本Atsuhito Sawabe团队利用图形化衬底技术在(001)方向的Ir/MgO衬底上进行单晶金刚石的外延,讨论了不同方向的条纹图案对金刚石横向生长过程的影响[40-41]。实验结果表明,条纹方向和生长条件都极大地影响着金刚石的ELO速率。考虑到位错是从Ir和金刚石界面产生的,所以选取一个有较高ELO速率的条纹方向和生长条件对获得高质量的外延金刚石极为重要。实验对比了横向生长区和成核区的拉曼光谱,横向生长区的拉曼峰半峰全宽仅为成核区的三分之一,证明了图形化衬底是获得高质量异质外延单晶金刚石的有效方法。2017年,该课题组进一步分析了条纹取向对位错传播的影响。实验结果表明:当条纹沿<100>方向时,位错主要会沿着(100)面传播,金刚石表面的刻蚀坑随机分布;而沿<110>方向的条纹在合并前,(111)晶面生长较快,所以成核区的位错将不沿<100>方向竖直向上延伸,而是会沿着(111)面倾斜传播。并且,部分位错会在生长过程中发生弯曲,并朝着<110>方向传播,刻蚀坑密度相对较小且主要集中在条纹合并处[42]。该实验表明,选取<110>方向的条纹图案及缩小成核区的面积可以进一步降低异质外延单晶金刚石的位错。此后,该团队继续利用网格状图案(grid-pattern)的方法,提高了金刚石横向生长的速率、扩大了ELO的生长区域,成功地将异质外延单晶金刚石的位错密度降低到了9×106cm-2,最小值达到了5×106cm-2[43]。通过对金刚石进行X射线衍射(XRD)表征,金刚石面内倾斜角和面外扭转角分别达到了0.064°和0.043°。此外,网格面积的大小对比实验结果表明,ELO面积越大,则金刚石的位错密度就越低。Golding等[44]利用金作为掩膜来实现图形化生长有效降低了金刚石薄膜的应力,并将位错密度降低至1.4×108cm-2。Mehmel等[45]利用激光技术在异质外延衬底形成孔洞的阵列,然后再进行二次生长,以此来降低异质外延单晶金刚石的位错密度。实验通过激光技术在原有的异质外延单晶金刚石衬底上制备出孔洞的阵列,并且通过调节甲烷浓度,使金刚石生长过程中横向的生长速率大于纵向的生长速率,从而在ELO区得到了位错密度仅为6×105cm-2的异质外延单晶金刚石。以上结果皆证明,图形化衬底技术可以有效地降低金刚石在异质外延生长过程中产生的位错,是获得高质量异质外延单晶金刚石的可靠手段。

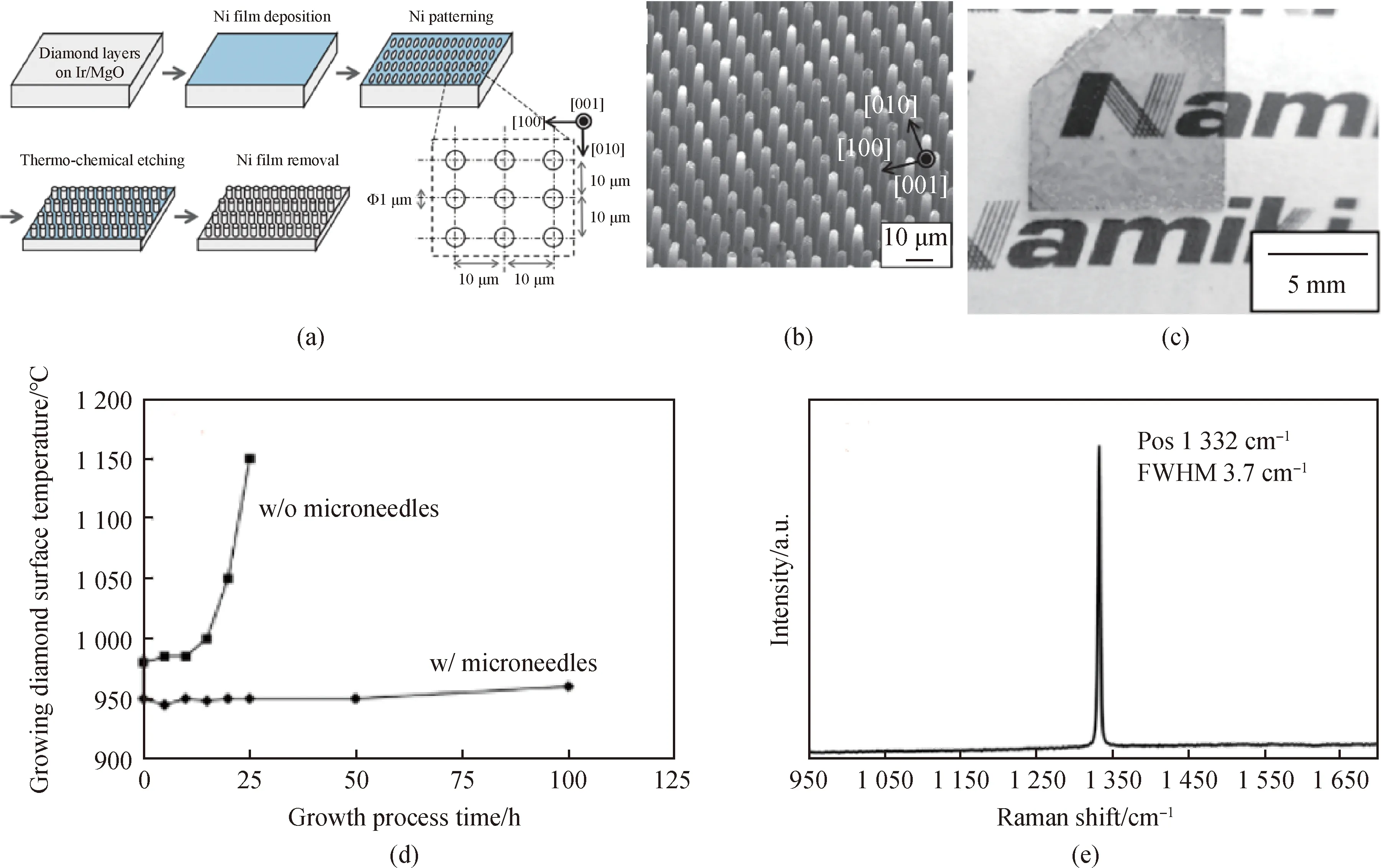

2) 金刚石微米针技术

Aida等在2016年提出了一种利用图形化与金刚石微米针来获得异质外延单晶金刚石自支撑衬底的方法[46]。其实验过程如图4(a)所示,先在BEN过程后的衬底上生长一层50 μm的金刚石薄膜,然后在衬底上通过光刻、镀膜形成带有小孔的Ni薄膜,然后将此衬底在H2氛围中进行高温退火。借助Ni在高温、还原性气氛下对金刚石的刻蚀作用[47],从而形成了金刚石微米针结构(见图4(b))。在进行100 h的快速生长后,由于氧化物衬底和金刚石的热膨胀系数不同,在关闭微波后,金刚石会自动与衬底剥离,从而得到自支撑金刚石衬底(见图4(c))。实验成功制备了尺寸为10 mm×10 mm×1 mm的单晶金刚石衬底,其拉曼半峰全宽为3.7 cm-1,晶体质量较好。Sawabe团队提出的该方法有以下优点:1)利用ELO提高了金刚石晶体质量;2)金刚石微米针可以有效地缓解金刚石和氧化物由于晶格失配所产生的应力,解决了快速生长过程中因衬底翘曲而散热不佳的问题;3)可以实现金刚石与衬底的自动剥离。此方法或可在所得金刚石衬底上进行多次迭代,不断提高金刚石晶体质量。

图4 (a)金刚石微米针制备工艺流程[46];(b)经Ni化学刻蚀后形成的金刚石微米针;(c)10 mm×10 mm×1 mm异质外延单晶金刚石衬底;(d)有、无微米针衬底在生长过程中的温度变化对比;(e)金刚石衬底的拉曼光谱图[46]Fig.4 (a) Schematic of microneedle/micropattern fabrication[46]; (b) diamond microneedles after Ni etching;(c) 10 mm×10 mm×1 mm heteroepitaxial diamond substrate; (d) surface temperature of growing diamond with and without microneedle; (e) Raman spectrum of diamond substrate[46]

相比氧化镁,蓝宝石具有更高的晶体质量、更低的成本、更大的晶圆尺寸、更小的热膨胀系数,以及更好的稳定性,更适合作为金刚石异质外延的衬底。2020年,Kasu等采用蓝宝石作为衬底,并结合了金刚石微米针技术,得到了1 英寸的自支撑高质量异质外延单晶金刚石(见图5),其位错密度为1.4×107cm-2[25]。通过XRD技术进行表征,金刚石衬底(004)面衍射峰的半峰全宽为113.4 arcsec, (311)面衍射峰的半峰全宽为234.0 arcsec。

图5 1英寸异质外延金刚石衬底[25]Fig.5 1 inch heteroepitaxial diamond substrate[25]

1.3.2 离轴生长和金属辅助终端技术

在金刚石外延生长中,采用离轴衬底可以促进表面台阶流动,进而有效地稳定生长表面,加快生长速率,以及抑制非外延晶粒生长[48-49]。2022年,Kasu团队在表面偏<001>方向7°的α-Al2O3衬底上进行金刚石的异质外延生长,其衬底结构如图6(a)所示。实验发现,金刚石在快速生长过程中呈台阶生长模式,其晶体内部的张应力被释放,改善了结晶质量,成功地制备了尺寸为2 英寸的单晶金刚石衬底(见图6(b))。图6(c)展示了该2 英寸单晶金刚石(004)面的XRD摇摆曲线半峰全宽全谱图,金刚石(004)和(311)面的XRD摇摆曲线的半峰全宽的最小值为98.35和175.3 arcsec,为目前所报道的最优值[50]。

图6 (a)离轴生长示意图;(b)2英寸异质外延单晶金刚石衬底;(c)2英寸单晶金刚石(004)面的XRD摇摆曲线半峰全宽全谱图[50]Fig.6 (a) Schematic of diamond growth on misoriented sapphire substrate; (b) 2 inch heteroepitaxial single-crystal diamond; (c) full width at half maximum mapping of the (004) X-ray rocking curve of the diamond substrate[50]

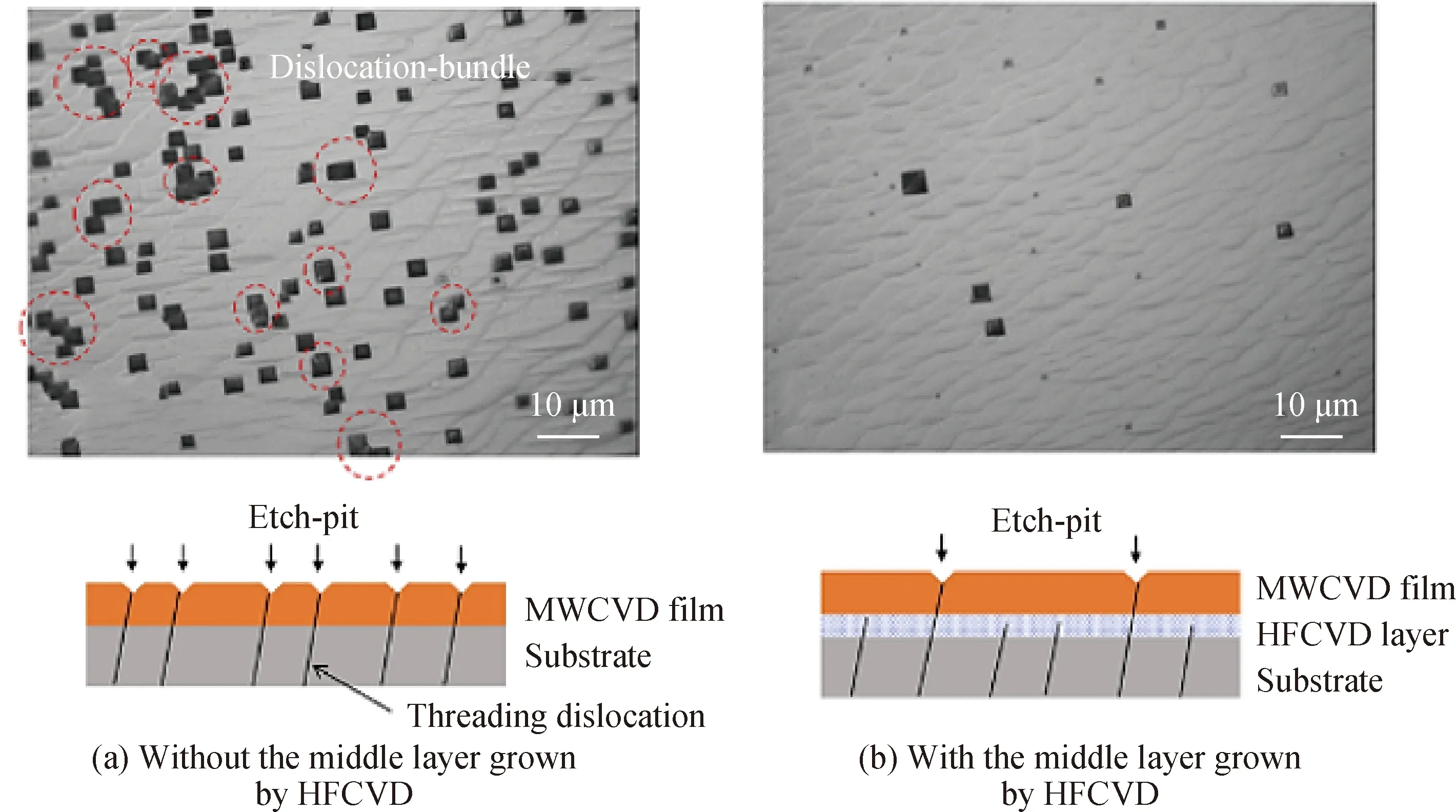

Yoshitake等在金刚石的外延生长过程中发现,先通过热丝化学气相沉积(hot filament chemical vapor deposition, HFCVD)生长一层缓冲层,然后再利用MPCVD进行金刚石外延可以有效地将金刚石的位错密度降低两个数量级[51]。这是因为HFCVD生长的金刚石层中含有大量的钨原子(浓度为1019cm-3),而钨可以有效地抑制从衬底衍生而来的位错,此技术称为金属辅助终端(metal-assisted termination, MAT)。如图7所示,加入含有金属W的缓冲层后,金刚石表面刻蚀坑数量明显减少,意味着位错密度大幅降低。他们将此技术运用到异质外延单晶衬底上,提高了金刚石的质量并改善了其面内均匀性[52]。

图7 经H2/O2等离子体处理后的MPCVD异质外延金刚石表面SEM照片[51]Fig.7 SEM images of MPCVD hetero-epitaxial diamond after H2/O2 plasma treatment[51]

2 基于异质外延单晶金刚石衬底的功率电子器件

2.1 场效应晶体管

金属-氧化物-半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor, MOSFET)因其开关速度快、输入阻抗高、功耗低、易集成等特点,广泛应用于功率开关、电能转换以及逻辑运算等领域。金刚石凭借其出色的性质,有望制备超大功率、超高频的MOSFET,且因为其超高的热导率,可以大幅简化其散热系统,降低成本。

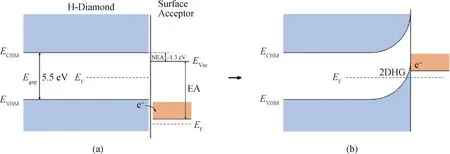

金刚石的n型掺杂技术面临着施主激活能高的问题,其技术还在探索中[53],而目前的金刚石基MOSFET主要是利用氢终端作为导电沟道来制备。氢终端金刚石暴露在空气[54]、二氧化氮[55]、臭氧[56],或是和一些过渡属氧化物如V2O5[57]、MoO3[58]等接触时,表面电子将会转移到表面吸附物中,从而引起表面能带上弯,进而在表面形成一层二维空穴气(2DHG)。该2DHG的空穴浓度达1012~1014cm-2, 迁移率为50~200 cm2/(V·s)[59],其导电机理如图8所示。本文所介绍的MOSFET皆是在(001)方向的异质外延单晶金刚石衬底上所制备的。

图8 氢终端金刚石表面形成二维空穴气的能带示意图[59]Fig.8 Energy diagram of the two-dimension hole gas formation on hydrogen-terminated diamond surface[59]

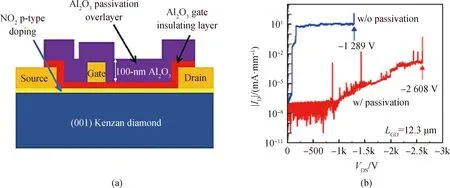

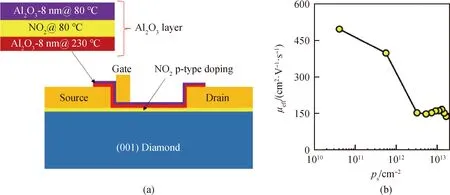

2020年,Kasu等[60]首次在大小为8 mm×8 mm×0.5 mm的异质外延单晶金刚石衬底上制备了MOSFET。异质外延单晶金刚石衬底(004)面XRD摇摆曲线的半峰全宽为254 arcsec。实验通过利用NO2增加了氢终端金刚石表面的空穴载流子浓度,并利用Al2O3作为钝化层和介质层。器件的最大漏极电流密度可达-776 mA/mm,击穿电压可达-618 V,比导通电阻为2.63 mΩ·cm2,其巴利加优值(BFOM)为145 MW·cm-2。2021年,Kasu等[61]制备了以Al2O3为介质层的MOSFET,并在器件表面再沉积一层100 nm厚的Al2O3来进行钝化。器件结构如图9所示。其最大源漏电流为-288 mA/mm。实验证明,100 nm Al2O3钝化层有效地抑制了器件的漏电,关态下实现了-2 608 V的击穿电压[61],击穿电场为2 MV·cm-1,这与目前SiC、GaN基MOSFET相当。

图9 100 nm Al2O3覆盖层的MOSFET结构截面示意图(a)和关态下的|ID|-VDS(b)[61]Fig.9 Schematic of cross-section of MOSFET with 100 nm Al2O3 overlayer (a) and the off-state |ID|-VDS characteristic (b)[61]

2022年,西安交通大学王宏兴团队在蓝宝石衬底上成功制备了尺寸为26 mm×26 mm×1 mm的异质外延单晶金刚石衬底,其(004)面XRD摇摆曲线的半峰全宽为209.52 arcsec。实验采用原子层沉积技术,用先低温(90 ℃)来防止氢终端氧化、后高温(250 ℃)来提高氧化铝质量的方法,制备了Al2O3介质层。所制备的场效应晶体管的最大源漏电流为-172 mA/mm。研究了在氮气氛围下,低温退火对器件性能的影响[62]。同年,Kasu等利用化学机械抛光(chemical mechanical polishing, CMP)技术对异质外延单晶金刚石衬底进行抛光来提高表面平整度和降低缺陷。在经过200 h的CMP处理后,金刚石表面粗糙度为0.04 nm,氢终端表面方块电阻大小为3.55 kΩ/sq,结果如图10(a)所示。实验中制备了以Al2O3为介质层的MOSFET,该器件最大漏极电流密度可达-0.68 A/mm(见图10(b)),最大有效迁移率为205 cm2/(V·s)(见图10(c)),比导通电阻为7.54 mΩ·cm2。器件在关态下的击穿电压达到-2 568 V,其击穿电场达2.3 MV/cm,该值接近GaN和SiC的理论临界电场。该器件的BFOM为874.6 MW·cm-2,是目前见诸报道的最高值[63],证明了金刚石在电力电子器件领域的强大潜力。

同年,该研究团队制备了“调制掺杂”金刚石MOSFET。如图11 所示,通过在8 nm 的Al2O3栅极介质层上方进行二氧化氮掺杂,将NO2和氢终端沟道进行分离,提高了空穴的迁移率[64]。其器件的最大有效迁移率为496 cm2/(V·s),击穿电压达到了-3 326 V,最大漏极电流密度为-0.42 A/mm, BFOM为820.6 MW/cm2,该研究证明了异质外延单晶金刚石有望运用于射频功率器件。2022年,该研究团队在(004)面XRD半峰全宽为98.34 arcsec的高质量异质外延金刚石衬底上制备了金刚石MOSFET,其击穿电压高达-3 659 V,是目前见诸报道的金刚石MOSFET最高值[65]。这些以异质外延单晶金刚石为衬底的MOSFET所展现出的优异性能证明了异质外延单晶金刚石在电力电子、射频功率器件领域的巨大潜力。

图11 (a)MOSFET横截面结构示意图;(b)调制掺杂的MOSFET有效迁移率随载流子浓度的变化[64]Fig.11 (a) Schematic of cross-section of MOSFET; (b) carrier density-dependent μeff of the modulation-doped MOSFET[64]

2.2 二极管

2.2.1 金刚石p-i-n二极管

2014年,Takeuchi团队在2 mm×2 mm×0.1 mm的(001)异质外延金刚石衬底上制备了金刚石准垂直p-i-n二极管[66]。如图12所示,p-i-n二极管的电流-电压特性表现出良好的整流特性。增大正向电流导致缺陷发光的积分强度呈亚线性增加,而自由激子发光的积分强度呈超线性增加。这一显著的趋势与在传统的HTHP合成金刚石衬底上用同质外延生长薄膜制备的p-i-n二极管所观察到的趋势相同。预示着异质外延单晶金刚石衬底在未来金刚石基电子器件中的潜力。

图12 (a)p-i-n器件结构以及测试原理图;(b)二极管正向导通特性[66]Fig.12 (a) Schematic of p-i-n diode including the electrode set up and circuit; (b) forward I-V characteristic of diode[66]

2.2.2 肖特基势垒二极管

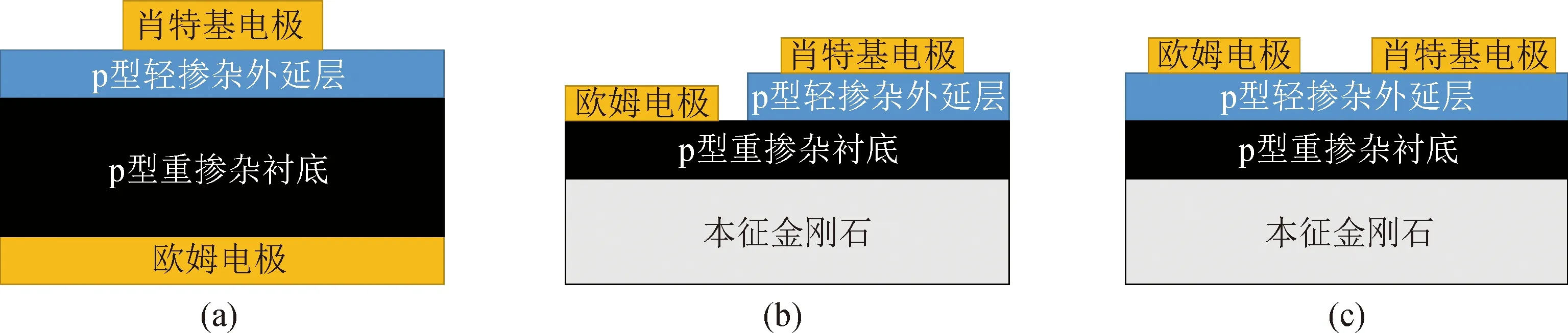

肖特基势垒二极管也可称为肖特基二极管,是一种利用金属-半导体整流接触实现的二极管;相比pn结二极管,肖特基二极管具有导通压降低、频率响应快的优点。由于金刚石的n型掺杂技术还尚未成熟,所以目前的金刚石基肖特基二极管主要通过p型金刚石和金属形成肖特基结实现。从结构上可分为垂直型、准垂直型和横向型,其结构如图13所示。然而,由于异质外延金刚石衬底中硼含量较少,所以目前大部分基于异质外延金刚石衬底的肖特基二极管主要为横向和准垂直型结构。

图13 (a)垂直型肖特基二极管;(b)准垂直型肖特基二极管;(c)横向型肖特基二极管Fig.13 (a) Vertical type SBDs; (b) pseudo-vertical type SBDs; (c) lateral type SBDs

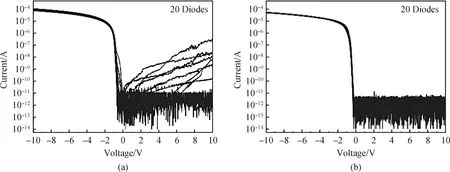

2015年,Yamasaki的研究团队在硅基异质外延金刚石衬底上制备了横向肖特基势垒二极管,采用Pt肖特基金属和硼掺杂的p型金刚石作为肖特基接触,表现出良好的电流-电压(I-V)特性。在±4 V下整流比大于1012,理想因子为1.2,击穿电场高达~1 MV·cm-1,大于硅的材料极限(~0.3 MV·cm-1)[67]。2020年,Arnault等[68]在Ir/STO/Si (001)衬底上进行金刚石的异质外延生长,并在抛光的173 μm厚的异质外延薄膜上制备了横向肖特基二极管。I-V特性表明工作二极管的成品率为92%,接近同质外延薄膜二极管的成品率。理想因子为1.85±0.2,势垒高度为(1.45±0.05) eV。2021年,Sittimart等[52]通过插入含有金属钨的缓冲层以抑制缺陷。在边长为5 mm的异质外延晶体上,制备了准垂直肖特基势垒二极管。插入缓冲层后,面内均匀性得到改善,所有肖特基二极管均表现出优异的整流效果,漏电流得到抑制,如图14所示。在±8 V电压下,整流比超过8个数量级。该器件击穿电压为375 V,平均击穿场强为1.7 MV·cm-1,证明了异质外延衬底是大面积低成本金刚石电子学的一个有前途的替代方案。

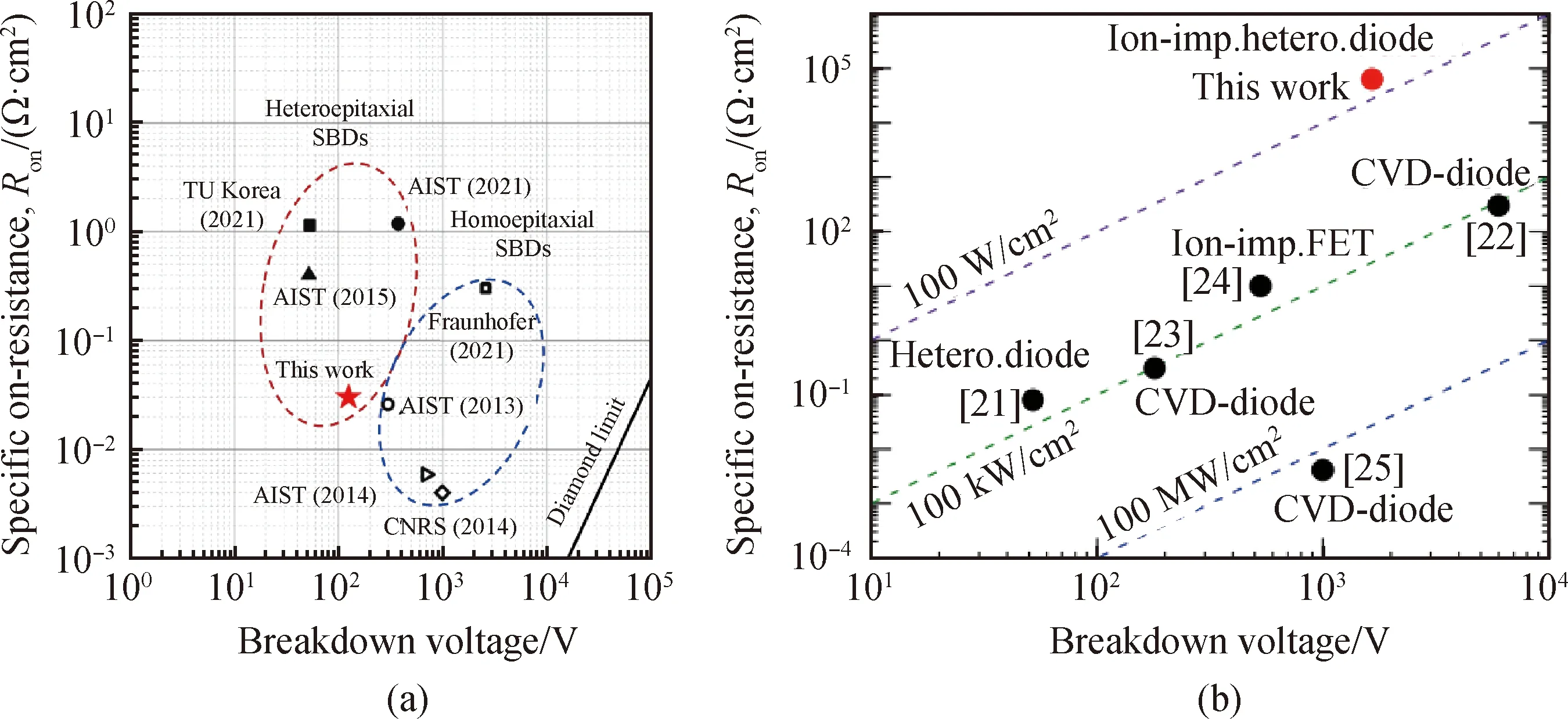

图14 没有(a)和有(b)缓冲层的20个肖特基二极管在室温下的I-V特性[52]Fig.14 Room temperature I-V characteristics of 20 SBDs without (a) and with (b) buffer layer[52]

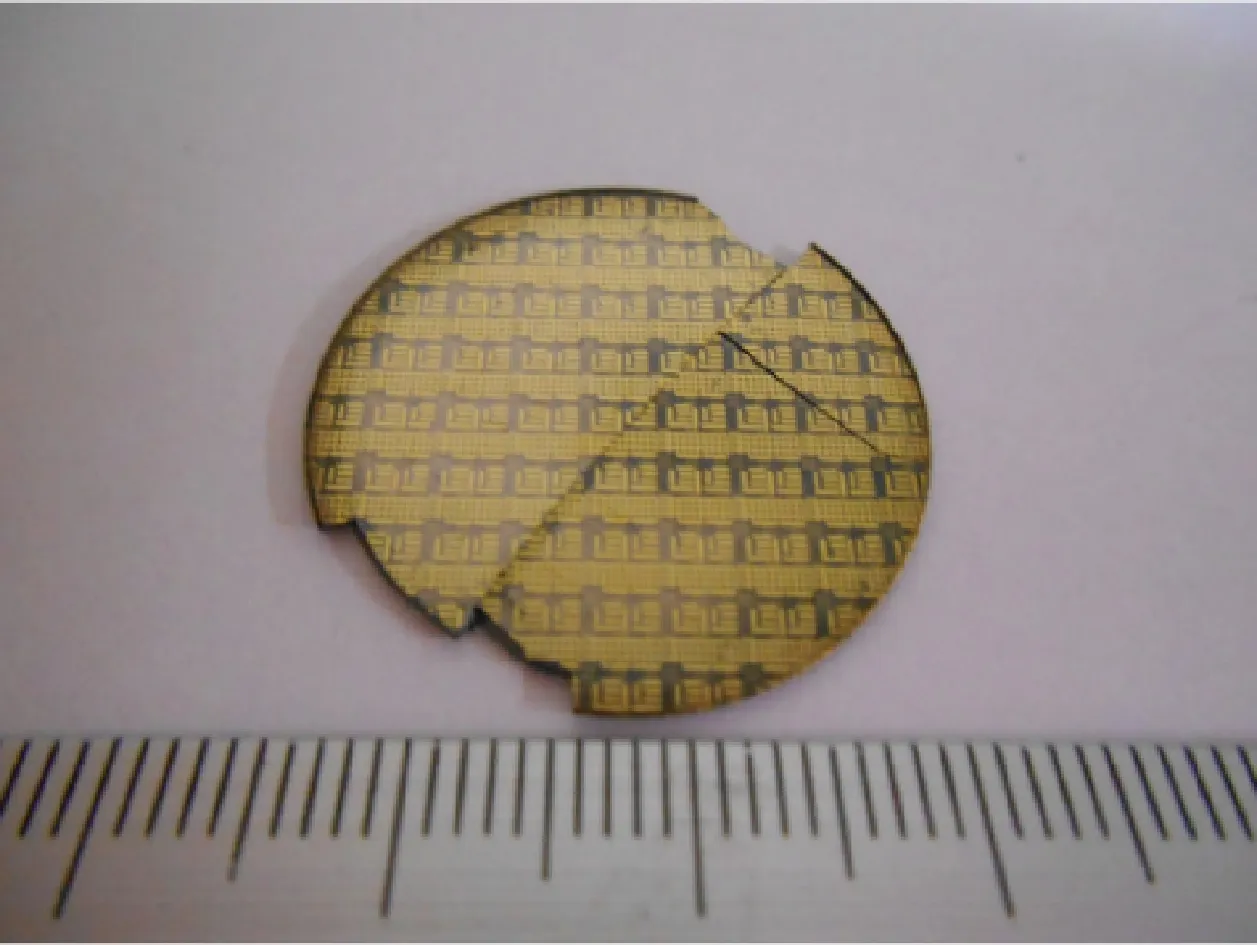

同年,Nam研究团队利用MPCVD技术在蓝宝石基自支撑异质外延金刚石上成功制备了肖特基二极管,并对不同生长速率下的肖特基二极管结构特性进行了表征。在低生长速率的器件上观察到了肖特基二极管良好的整流特性。理想因子为1.4,最大击穿场强约为1.1 MV·cm-1[69]。2022年,Weippert研究团队在Ir/YSZ/Si(001)衬底上,通过异质外延生长单晶金刚石,并制备了准垂直型肖特基二极管[70]。该二极管由不同厚度的p-掺硼金刚石层(1015~1016cm-3)上的Ti/Pt/Au接触和准本征金刚石起始衬底上底层p+层(1019~1020cm-3)上的欧姆接触组成。而正向电流表现出低电压的分流电导,并且在较高电压下,热电子发射行为与p-层膜厚有系统的依赖关系。对于肖特基势垒,观察到与理想因子n的系统性关联,“理想”n=1时肖特基势垒为1.43 eV。最佳二极管的击穿场强达到1.5 MV·cm-1。2023年,Nam研究团队利用离轴生长方法提高了异质外延(001)金刚石的晶体质量,并在衬底上制备了准垂直肖特基二极管。该器件在电压为±6 V时,整流比达到~108,电压为-5 V时的特征导通电阻为30 mΩ·cm2。其最大反向击穿电压为124 V,击穿场强为2.1 MV·cm-1[71]。同年,Kasu研究团队在异质外延金刚石衬底上生长了300 nm的外延层,并利用离子注入技术进行硼掺杂,制备了横向金刚石肖特基势垒二极管。该器件在电压为±15 V时,整流比为3.6×105,拥有-1 651 V的高反向击穿电压,平均击穿场强为0.46 MV·cm[72]。图15对比了近年来所报道的金刚石肖特基二极管的电学性能。横坐标为击穿电压,纵坐标为比导通电阻。从图中可以看出,基于异质外延单晶金刚石衬底的肖特基二极管的性能总体上是不如同质外延金刚石衬底的,这主要是因为目前的异质外延单晶金刚石衬底的晶体质量难以达到同质外延的水平。所以,进一步提升异质外延单晶金刚石晶体质量是提升器件性能的关键。

图15 金刚石肖特基二极管性能对比图[71-72]Fig.15 Performance comparison of diamond Schottky barrier diodes[71-72]

3 结语与展望

金刚石异质外延已发展30年有余,而基于Ir衬底的大面积、高质量的异质外延单晶金刚石已取得较大进展。本文主要从关于异质外延单晶金刚石及其电子器件两个方面对异质外延单晶金刚石的发展进行了阐述。发展至今,异质外延单晶金刚石衬底最大尺寸已近4 英寸,其晶体质量在不断攀升新高度,基于异质外延单晶金刚石的电子器件也展现出了非常优异的性能。这些喜人的成果证明了金刚石在电子领域内的巨大潜力,加快了金刚石走向实际应用的步伐,也坚定了金刚石领域研究人员的信心。虽然在异质外延单晶金刚石衬底上取得了诸如以上的喜人成果,但关于单晶金刚石异质外延的如下问题还有待解决:

1)金刚石与Ir的晶格失配。即便目前Ir是进行单晶金刚石外延的最有效材料,但其与金刚石的晶格失配率高达-7.1%,这导致金刚石与Ir界面会产生较多的位错。虽然经过了不断地探索,但目前异质外延单晶金刚石的位错密度相比同质外延依然很高,如何进一步提升异质外延单晶金刚石晶体质量,是加快其应用的关键一步。

2)异质外延单晶金刚石的掺杂技术。通过掺杂来实现电导调制是半导体走向应用的必经之路。同质外延单晶金刚石的掺杂技术已发展多年,并取得了一定的突破,但基于异质外延金刚石的掺杂的报道却很少。

3)虽然金刚石功率器件展现出了十分优异的性能,但却没有完全发挥出其材料的优越性,所以还需进一步优化器件结构和提高其晶体质量以提升电子器件性能。