基于FPGA 的数字滤波器设计

周 钧 樊 闯

(中车大连电力牵引研发中心有限公司,辽宁大连 116000)

0.引言

随着国内需求和科技发展,轨道交通进入了高铁时代,目前列车与基站之间无线通信需要靠无线基站通过载波进行通讯,一般采用特定的频段(2.4GHz)。载波在传输的过程中容易受到干扰,比如噪声干扰。为了实现通信需求,可在接收端设置数字滤波器,是一种可从受环境噪声干扰的测试信号中分离出特定载波频率信号的滤波器,可提取以参考频率为中心的指定频带内的信号,有效滤除所有其他频率分量(噪声信号),完成载波数据的通信信号通信,进而实现更好的无线网络通信[1]。

1.设计原理

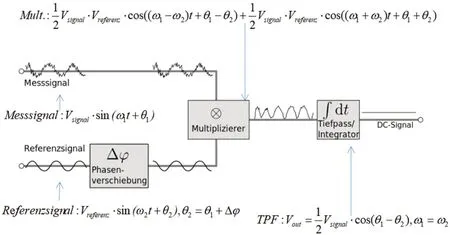

本文设计的数字滤波器基于“通信信号是时间上相干的,而噪声信号在时间上是不相干”的原理设计。已知通信信号的频率,可生成具相同频率的参考信号。将参考信号与测试信号(包含通信信号与噪声信号)相乘,可将测试信号中的通信信号和噪声信号相互分离,然后借助积分器消除噪声来实现功能[2],如图1 所示。

图1 数字滤波设计原理

将测试信号(messsignal)与参考信号(referencesignal)进行相乘后,再积分运算,去除时间无关的干扰信号,获得带正弦与余弦的表达式:

同理,同样的模块,获得带正弦的表达式:

通过三角函数定理:

实现通信信号未知参数A(振幅)的计算,完成提取以参考频率为中心的指定频带内的信号,有效滤除所有其他频率分量,实现数字锁相滤波。

2.开发环境概述

本文中环境由FPGA 开发板、示波器和信号发生器组成。Spartan 3E:XC35C500 芯片满足需要的LUT 资源和I/O 资源,含一个LTC 1407A 模数转换器和一个LCD 显示器。示波器Tektronix TPS 2024:带宽为200MHz,最高取样速率:2.0GS/s,具有4 个通道。信号发生器HM-8030:频率50MHz 至10MHz,具备高纯度和幅度稳定性。

3.基于FPGA 的数字滤波器设计

3.1 设计框架

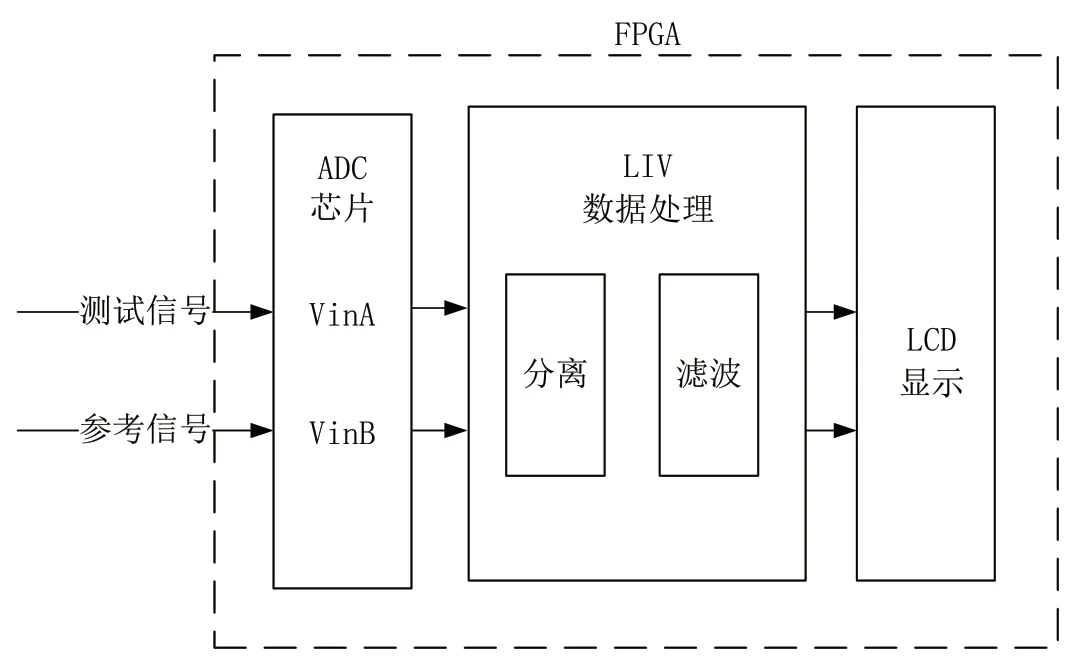

FPGA 设计框架如图2 所示。

图2 FPGA设计框架

3.2 信号处理流程

如图2 所示,测试信号(messsignal:VinA)和参考信号(referencesignal:VinB)被ADC 芯片采集转化,这部分由ADC 芯片完成;接下来,转化的数据进入数据处理模块(LIV)进行信号分离滤波,分离信号三角函数计算,积分滤波和其他处理;之后将处理完成的结果发送到LCD 控制模块,最终在屏幕上进行结果打印[3]。

3.3 设计实现

本文设计根据在噪声环境下的数字滤波需求,结合开发板资源,设定适当的采样频率范围和输入波形,通过由顶层到底层的设计思维,进行FPGA 的代码编写进行代码设计。

(1)根据滤波技术要求,确定滤波器类型、算法、系统精度误差、采样频率、输入数据长度和输出数据显示方式;(2)根据确定的技术参数设计顶层架构和顶层逻辑结构;(3)在顶层架构里定义和描述全局代码结构,各子模块之间的关系。信号输入和屏幕输出参数同样在顶层定义;(4)顶层模块之下,由模数转换模块,信号处理模块,滤波模块和LCD 显示模块这些二级模块组成;(5)各二级模块根据功能划分,将各自功能用VHDL 进行编码设计。二级模块经过仿真实现,在顶层模块进行结合,实现一整套系统功能。

3.3.1 模数转换设计

ADC 芯片将采集的模拟信号离散化为单个离散采样值。再将采样值转为数字值,根据板卡搭载的ADC 芯片LTC 1407A,模拟信号被转换为14 位的数字信号[4]。

3.3.2 信号分离设计

(1)参考信号作为已知的信号,进行三角分解,分解成sin 向量和cos 向量;(2)将模数转换后的测试信号和分解后的参考信号相乘,获得第一混合信号,并分离第一混合信号中的噪声;(3)根据已知的参考信号对第一混合信号进行计算,获得没有噪声的通信信号的sin 向量和cos 向量,即通信信号的sin 向量和cos 向量;(4)根据通信信号的sin 向量和cos 向量,计算测试信号不含噪声的振幅、测试信号不含噪声的初相。

3.3.3 滤波设计

本文中的低通滤波器为有限冲击响应滤波器(FIR),积分运算通过该低通滤波器进行实现,经过低通滤波器后,噪声信号将被过滤掉,通信信号将被保留并输出。

3.4 simulation 仿真

本文设计需要实现模数转换,所以simulation 仿真内容只能实现到静态时序分析上,通过testbench 产生数字激励并通过ISE14.7 自带的仿真软件进行仿真。

3.5 硬件协同仿真

硬件协同仿真即半实物仿真,本文设计中将编码完成的“.bit”工程文件下载到开发板中进行仿真。本文用信号发生器生成两路模拟信号,A 路测试信号,B 路参考信号,A 路上加载干扰信号(噪声信号)。两路输出信号链接至ADC 芯片上,信号通过ADC 芯片后离散为数字信号,进入系统进行分离、滤波,最终的结果将显示在LCD 屏幕上。

4.测试验证

验证数字滤波器除噪功能,测试是唯一的标准,因为simulation 仿真产生的模拟信号可以非常接近,但是始终无法完全代替真实的模拟信号。本文设计测试时,对不同的频率和振幅进行了测试,并对实验结果进行描述。

4.1 测试

通过采样和逻辑运算后,在LCD 屏幕上将打印3 个信息:S:带正弦(sin)的表达式,C:带余弦(cos)的表达式和A:振幅(amplitude)。如图3 所示,测试1通信信号振幅为1V(峰-峰值2V)。FPGA 处理后的数据比较精确地将振幅锁定在1V(正负3.5%);同理,测试2 通信信号振幅为0.72V(峰-峰值1.44V)。处理后的数据的振幅锁定在0.72V(正负1%)。

图3 测试验证

4.2 测试列表

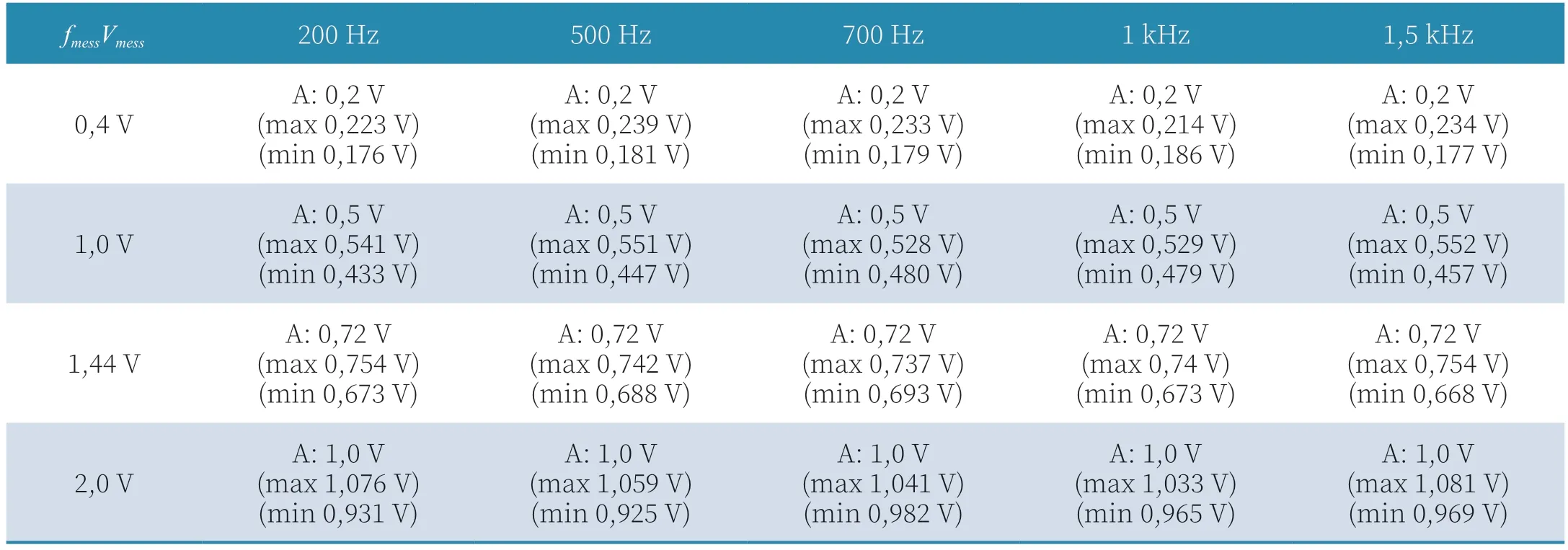

将不同频率和振幅的测试数据进行汇总,得到的汇总表格如表1 所示。

表1 测试数据汇总

可以发现FPGA 处理后的数据比较精确和稳定,误差范围可控。证明了在噪声环境中通过噪声信号非时间相干特性原理设计的数字滤波器,可以较好地获取通信信号。

5.结语

本文介绍了基于FPGA 的数字滤波器的原理,系统结构,以及核心算法模块结构。在VHDL 语言环境下创建系统仿真模型,并在实验室环境中通过在FPGA 硬件板卡上进行硬件协同仿真测试。硬件协同仿真测试结果表明,该数字滤波器的性能满足从复杂环境中过滤干扰信号的滤波设计技术要求。在信号处理单元中,通常需要利用滤波器对电网电压信号进行采样滤波,采用上述模型进行数字波器设计,可以实现良好的消除噪声特性。