一种频率注入型的快速起振晶体振荡器

蒋徐前,陈磊,张鸣,贾晓哲

(上海电力大学 电子与信息工程学院,上海,201306)

0 引言

随着物联网的飞速发展,便携式设备、传感器节点等被广泛应用于工农业、交通物流、生物制药等诸多生产与生活领域中。由于这些电子系统大多采用电池供电,为了提高芯片的续航时间,减少系统的功耗,一种常见的做法是周期性的切换高低功耗的工作模式,并且系统在大多数时间是处于低功耗模式,当需要进行数据传输与接收时才会唤醒设备。这对集成电路设计的功耗与唤醒时间提出了更高的要求。

在芯片中,作为基准频率源的时钟产生电路,这类电路我们称之为振荡电路。其中,石英晶体振荡电路是利用晶体的压电效应以产生机械共振,因其具有极高的频率稳定度而被广泛用于频率精度要求高的场景中。然而传统的石英晶体振荡器由于其高品质因子,在没有辅助启动电路的帮助下,常常需要几毫秒才可以输出稳定的频率。而芯片内其余模块,例如PLL、BG、LDO 等,其启动时间往往在10μs 左右,因此晶体振荡器的启动时间决定了整个芯片的启动时间以及启动过程中消耗的能量[1]。

本文设计了一种频率注入型的快速起振的皮尔斯晶体振荡器,由逻辑控制电路、频率注入电路、主振荡电路以及输出检测电路构成。并且该电路的时序控制由内部环路自生成,无需额外的寄存器时序控制信号。由于其起振速度快,适用于低功耗及快速响应的电子系统。

1 石英晶体模型及启动时间分析

■1.1 石英晶体模型

石英晶体的等效模型及其电抗随频率变化的曲线如图1所示:低频时,晶体呈现为容性;随着频率的增加,晶体逐渐接近串联谐振点fs,此时晶体的等效串联阻抗达到最小值;当频率增加到串联谐振工作点fs以上时,晶体呈现为感性,并且随着频率的增加,晶体逐渐趋近并联谐振工作点fp,此时晶体相当于一个LC 并联电路,等效阻抗达到最大;随着频率继续增大,晶体在此呈现出容性。

图1 石英晶体等效模型及电抗频率曲线

石英晶体由于其高品质因数,其串联谐振频率fs与并联谐振频率fp十分接近,其表达式如式(1)和式(2)所示。

■1.2 振荡器电路的起振条件

任何一个振荡电路模块,其模型都可以用标准反馈系统等效,其包括增益放大单元和反馈单元,反馈网络模型如图2所示,该反馈网络的闭环反馈环路系统的传递函数如式(3)所示。

图2 闭环反馈系统模型

图3 快速起振晶体振荡器系统框图

石英晶体振荡器要求系统为增益大于1的正反馈环路,需要满足(1)环路增益| Av ( jw ) * β( jw)|≥ 1;(2)相位ϕ(Av(jw) ) +ϕ(β(jw) ) = 2nπ(其中n 为整数)。石英晶体振荡器工作时会经历自激放大和平衡状态两个过程[2]:

(1)自激放大

环路中的反相放大器会对环路中的噪声进行放大,而高品质因数的晶体会对这些噪声进行选频,由此晶体环路产生了自激。这些自激的信号会通过增益模块不断循环放大,振荡信号的摆幅也被逐渐放大,随后产生电路需求的振荡信号。

(2)平衡状态

在自激的过冲中,增益模块会对摆幅不断地进行放大,并且晶体会对放大的信号选频,所以特定频率的信号会不断的放大。随后,当输入端信号的幅度达到一个临界值时,放大模块会进入线性区,环路增益会变为1,此时幅度不再增长,整个电路转而进入平衡状态,振荡器表现为稳幅振荡的工作状态。

■1.3 振荡器电路的起振时间

忽略非线性因素带来的影响,晶体振荡器启动时间表达为式(4)所示[3]:

其中CT为振荡电路总并联电容大小;τ= 1/α,为输出电压指数率增长的时间常数;i(0)为晶体的RLC 串联支路的初始电流。

2 快速启动电路设计

■2.1 系统框图及分析

该方案通过逻辑控制模块进行加速使能与稳定使能的切换:

(1)加速使能时,由RO 构成的频率注入模块对晶体注入能量,该频率与晶体的本征频率相近,因此晶体内部RLC 串联的等效电路的电流摆幅会迅速增加,由此帮助晶体振荡器迅速起振[4]。

(2)本设计在注入时间达到2μs 时,通过逻辑控制模块断开频率注入模块的加速使能,开启皮尔斯振荡器模块的稳定振荡使能,由于晶体的RLC 串联支路在加速起振阶段已经具备一个初始的较大电流值[5],因此皮尔斯振荡器的输出端的振荡电压信号会迅速产生。该低摆幅的振荡信号会被中频放大器检测到并且通过大增益的两级放大器放大,迅速产生晶体本征频率的方波信号。

■2.2 皮尔斯振荡电路

图4为皮尔斯振荡电路,其中IB为基准电流,M9与M8、M10共 同 组 成 简 单MOS 电 流 镜,M2、M3与M4、M5共同构成低压的共源共栅电流镜,该结构的高输出阻抗更贴近理想电流源,可以为核心放大管M1提供更为稳定的电流,M6、M7栅漏短接构成二极管连接型MOS,其为低压结构共源共栅电流镜提供栅极偏置电压;Cc、Rc、M2A、M1A、M2B、M1B共同构成中频段的放大器可以有效地检测到并放大低摆幅的振荡信号,Cc用于隔离M1漏端的电压直流信号,Rc、M2A、M1A重新建立输出电压的直流工作点,M2B、M1B在快启时导通,增加输出幅度。晶体XTAL 以及负载电容C1、C2均设置在芯片外部,由管脚X1、X2 接入芯片,电容C1、C2 与石英晶体XTAL 构成的选频网络可以对环路中特定频率信号进行选频进而保证输出频率的稳定度; 反馈电阻Rf用于建立并保持M1 管的栅漏电压,使两端电压的直流值相等。

图4 皮尔斯振荡电路原理图

■2.3 频率注入模块与时序逻辑

2.3.1 频率注入模块

频率注入是通过一个环形振荡器输出与晶体本征频率相近的时钟信号,该环形振荡器结构如图5所示。

图5 环形振荡器

图5为5 级反相延时单元组成的环形振荡器,其单个延时单元可以产生Td的延时,其时钟输出周期为TRO=5*Td,输出频率为TRO=1/TRO=1/(5*Td),因此若要产生16MHz的时钟频率,可以计算出单个的延时单元需要产生125ns的延时。

2.3.2 频率注入时序

图6为本设计的工作时序图,EN 信号为整个系统的使能信号;RO的时钟信号作为频率注入的基准源,其为晶体注入本征频率相近的振荡信号;EN_CFI 为注入使能,用于控制RO的注入,其注入一段时间后关闭,以减少能耗;IM 和XO 分别为晶体运动支路电流以及晶体的振荡信号;EN_OUT 用于控制晶体的时钟输出。本文设计的快速启动晶体振荡器的启动时间为tstart=tCFI+tcnt,其中tCFI为频率注入所用时间,tcnt为计数时间。

图6 频率注入型晶体振荡器的工作时序图

3 电路仿真验证

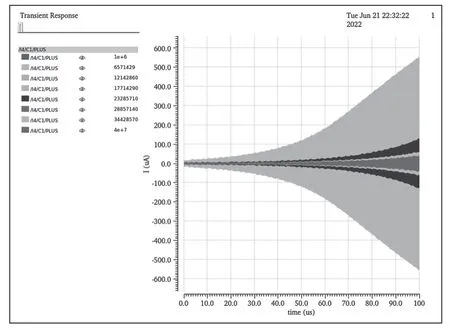

本设计的后仿真验证结果如下,图7 为基于频率注入的快速起振晶体振荡器版图;图8 为不同频率注入时,晶体RLC 支路电流IM的增长速率;图9~图11 分别为tt、ss、ff 工艺下起振时间随着温度以及电源电压变化的情况;表1 为本文快速起振振荡器的技术指标。

图7 基于频率注入的快速起振晶体振荡器版图

图8 不同频率注入时,晶体RLC 支路电流IM的增长速率

图9 tt 工艺下的起振时间

图10 ss 工艺下的起振时间

图11 ff 工艺下的起振时间

图8为不同频率方波注入时晶体的RLC 支路的电流幅度增长的情况,前文已经介绍,晶体振荡器的起振速度与RLC 支路的初始运动电流大小呈现出正相关性。观察图8可知,注入的频率与晶体的本征频率越接近,其运动支路的电流幅度增长得越迅速。

图9~图11展示了在不同工艺下的该频率注入型的快速起振晶振的起振时间随着温度以及电源电压的波动情况,本设计在PVT 下总体在7.2μs 内均能完成起振。

表 1 本文快速起振振荡器的技术指标

4 总结

该方案通过一次频率注入的设计思路,以RO的振荡信号对晶体进行注入从而晶体内部RLC 支路电流摆幅迅速增加。随后通过逻辑控制单元对工作模式进行切换,当注入时间达到设定的阈值后,逻辑控制单元关闭注入加速使能,皮尔斯振荡器开始工作,由于电流具有较大初始值,起振速度十分快;输出级利用中频放大器对小摆幅振荡信号检测并放大,产生50%占空比的方波振荡信号。本设计最终在40nm 工艺下,-40℃~120℃的温度范围内,1.2V 工作电压下,tt、ss、ff、sf、fs 各个工艺下,均可以在7.2μs 内完成起振。