基于SOC 技术的微机原理实验课程教学改革探索*

贵州师范学院物理与电子科学学院 邓睿 余宏 莫章洁 岳天天 王丹钰

微机原理与接口技术是计算机及电子信息类相关专业的一门专业基础课程,其理论课的教学过程中主要侧重于讲解微机系统的体系结构、各计算机组成模块的工作原理,包含处理器的架构、总线以及通信外设接口等概念及原理。理论教学环节能够提高学生对微机和接口的原理性把握,做到“知其所以然”,但是做好教学的前提是要进行验证,或者说在“知其所以然”之前要能够“知其然”,那么实验教学环节就显得尤为重要[1]。

1 微机原理实验教学现状

微机原理与接口技术这门课程概念抽象、实践性很强,上机实验和课程设计是两个重要的教学环节[2]。作为传统课程实验所使用的实验箱,芯片已经固定,线路也已经规划好,所以实验箱的功能受到极大的限制,实验内容也比较固定,造成实验项目和更新都受到一定限制[3]。针对目前该课实验教学是以固定单片机硬件为核心教学,而无法灵活与理论无缝地衔接问题,提出一种基于SOC 技术的实验教学方法,且以ARM 公司开源的Cortex-M3 为软核处理器为基础,采用Verilog HDL 语言灵活构建嵌入式SOC 实验开发平台,提高了学生地兴趣和实验的灵活性。

因此,为了更好地将微机原理的理论与实践深度融合,提出基于以ARM 公司开源地Cortex-M3 为处理器软核,构建SOC 系统架构,采用EDA 开发工具和FPGA硬件分别进行软硬件平台的开发,从而达到对微机原理实验课程教学改革进行探索。

2 基于SOC 技术的实验教学改革

SOC 是一种用于嵌入式开发的片上系统技术,以Verilog HDL 硬件描述语言将软核处理器(Cortex-M3)、存储器、总线和外设接口模块集成在一起,完成微型单片机系统的构建,且基于FPGA 芯片作为硬件验证的载体。此FPGA平台具有设计灵活、可裁剪、可扩充,且软件硬平台可编程的特点,对微机原理的实践具有改革性的意义。

2.1 基于SOC 技术实验平台系统架构

系统采用ARM 公司开源的Cortex-M3 为软核处理器,此软核是以Verilog HDL 硬件描述语言实现,因此,具有操作灵活性和集成灵活性,且可观测到处理器内部的结构。构建以ARM 处理器为核心的SOC 系统(如图1所示),根据微机原理的体系架构理论,最小系统应包含RAM 存 储器、ROM 存储 器、AHB 和APB 总 线 系统以及其他外设模块(如表1 所示),设计均采用硬件描述语言Verilog 实现,可采用Quartus 和Modelsim 软件实现软硬件的协同仿真,对系统架构和外设接口进行仿真验证。

图1 基于SOC 技术的微机原理最小系统架构Fig.1 The minimum system architecture of the microcomputer base on SOC

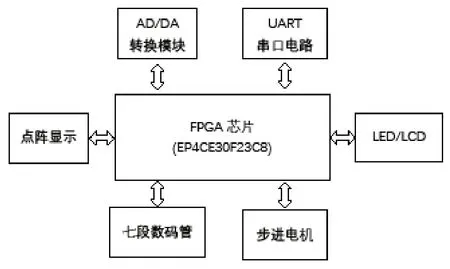

辅之以FPGA 硬件平台,采用Altera 公司的FPGA芯片Cyclone IV 系列EP4CE30F23C7 为核心来构建实验硬件平台(如图2 所示),且将表1 中的外设模块对应的外围硬件电路(含LED 灯、LCD 显示器、数码管显示、点阵显示及步进电机等)集成至硬件平台,以便于对SOC 微机系统进行硬件功能验证。

图2 基于FPGA 芯片的SOC 系统硬件实验平台Fig.2 Hardware of the SOC base on FPGA chip

表1 各外设模块及其相应功能Tab.1 Function of the peripheral module

2.2 基于Cortex-M3 的微机最小系统实现

Cortex-M3 是一个32 位处理器内核,内部的数据路径、寄存器以及存储器接口均是。M3 采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访问并行不悖。数据访问不再占用指令总线,从而提升了性能。因此,其内部含有多条总线接口,每条都针对不同的应用场合优化过,并且可以并行工作。此SOC 技术平台,采 用ARM Design Start 系 列 的Eval 版Cortex-M3 软 核作为内核CPU 处理器。从M3 软核源代码的模块顶层接口可以看出,其主要功能划分为系统控制信号(时钟复位和大小端)、指令总线信号(数据、地址和控制线)、数据总线信号、系统总线信号、中断信号源、JTAG 接口和HTM 系统状态跟踪信号。

从地址线可以看出,存储器映射CM3 寻址空间为4GB,根据微机系统的理论原理,需要对存储空间进行划分和映射,以便于处理器对系统内部的各模块进行寻址访问。在此嵌入式SOC 系统中,可以根据不同的需求和应用自定义存储空间,具有灵活性和便利性,且对理论教学的知识进行很好的实践。本系统中采用Verilog语言实现译码器对地址总线进行译码选择不同地址段的空间操作,其代码如下所示,hsel 为地址片选信号,HADDR 为系统地址总线:

微机系统采用的是AHB 总线系统,通过AHB 总线的地址对存储空间进行译码,从译码逻辑中可以看出,存储空间主要分为ROM、RAM、APB 外设和高速GPIO 模块,其中APB 外设的寻址需要在AHB-APB 桥的基地下重新划分。例如:ROM 地址为0x0000_0000--0x000F-FFFF用于存储代码,RAM 地址为0x2000_0000--0x200F-FFFF用于存储临时变量,AHB-APB 桥地址为0x5000_0000--0x5000-FFFF 用于连接APB 总线的转换逻辑。

2.3 基于SOC 技术平台的教学案例

基于技术平台的教学实践过程主要分为3 个部分:微机系统的电路设计实现、C 语言软件编程及协同仿真和FPGA 硬件平台实现。

微机原理最小系统的硬件电路实现是采用硬件描述语言(简称Verilog)设计在EDA 工具Quartus 开发实现,所设计的整个嵌入式微机系统的运行是根据C 语言编程的程序执行,在此过程中,需要利用Quartus 平台实现软硬件协同仿真。然后,将实现的系统硬件电路在FPGA 平台进行固化,从而形成系统。以SPI 模块接口集成为例进行教学案例讲解。

2.3.1 微机系统的电路设计实现

此内容是在前期采用Verilog 语言设计实现的含有处理器Cortex_M3、程序存储器ROM、随机存储器RAM和AHB 总线系统的最小微机系统基础上,将SPI 接口的逻辑模块集成到系统,目的是为了使学生熟悉微机原理总线系统的概念。如图3 所示为具体的实现逻辑,进而可采用Quartus 平台实现硬件逻辑图。

图3 SPI 模块集成至微机总线逻辑设计Fig.3 Design of the SPI integrated in system

2.3.2 软硬件协同仿真

在将SPI 模块集成到微机的总线系统后,需要通过C语言编写驱动软件,利用处理器系统对SPI 模块的功能性进行验证。C 语言程序生成的hex 文件是存放在ROM 中,上电复位之后处理器通过ROM 的读取进行指令的执行。在 Quartus 开发平台中,可以通过Modelsim 仿真器对系统进行软硬件协同仿真,观测微机系统处理器的执行状况及SPI 驱动的结果。如图4 所示为SPI 仿真的时序以及系统AHB 总线的运行图,展示了系统总线信号与SPI接口输出信号的变化执行情况。

图4 软硬件协同仿真系统验证执行情况Fig.4 The co-simulation of the system verification in hardware and software

2.3.3 FPGA 硬件实现流程

FPGA 内部含有大量的数字逻辑资源(门电路、触发器和存储器等),但是彼此之间没有连接关系,称为可编程逻辑器件,可灵活多次编程地实现数字逻辑系统电路。本平台采用了Altera 公司地EP4CE30F23C8 芯片,在完成了微机SOC 系统的电路设计实现和仿真验证后,需要将所设计的系统与实际的硬件电路板连接,需要根据FPGA 电路板的板级原理图与所设计的微机系统进行管脚分配,从而完成从软件到硬件的实现过程。

3 总结

本文通过Cortex-M3 处理器的Verilog HDL 软核,使用EDA 软件Quartus 平台和硬件FPGA 电路板,运用SOC 技术实现了微机系统的最小系统架构设计、电路的软连接设计、Modelsim 仿真验证以及硬件验证,弥补了当前微机原理实验的不足和弱点,由于其灵活性方便学生在实验失败时进行深度调试,提高实验的积极性与创新的意义。当然,此教学方式对课程的延续性有一定的要求,需要开设前导课程硬件描述语言Verilog HDL,但是此教学改革模式与微机原理理论吻合度很高,也具有深远研究的意义。