基于虚拟时反测向系统的FPGA课程教学研究与实践

于智欣

摘要:FPGA设计课程内容复杂且应用灵活,传统的授课方法使得课程内容变得抽象,不易被学生理解。因此,结合当下最热门的电子侦察领域,利用一种虚拟时反测向新技术,结合FPGA设计实现一种新的测向系统。该系统的设计采用Xilinx公司FPGA开发板,通过信号的传输、控制、处理以及存储等技术手段,比较全面地学习和探索了FPGA设计的基础功能。这样不仅能够提高学生的学习兴趣,同时锻炼了学生的动手能力,更好地提升了学生对于该课程知识和技术的掌握。

关键词:FPGA;虚拟时反;测向系统;教学研究与实践

一、前言

FPGA是指现场可编程门阵列(Field Programmable Gate Array,FPGA),其优势能够解决定制电路的不足以及克服原有可编程器件门电路数有限的缺点[1]。目前主要以Xilinx和Altera两家公司的开发板作为主流,它们各自有配套的软件,其中分别以为Vivado和QuartusII使用最为广泛,采用的编程语言以VHDL以及Verilog为主,同时配合C语言进行控制。通过FPGA可以进行多通道的设计,这种设计是基于FPGA设计最大的优势,利用有限资源快速实现所需功能。FPGA设计作为一门实用性强的课程,通过传统的授课方式进行讲解不利于学生的理解,应该搭配前沿技术的系统设计,在实现系统功能的过程中逐步掌握该门课程的核心知识,快速完成本门课程的学习[1]。

时间反转技术具有自适应聚焦特性,可以考虑将其应用于电磁信号测向领域中,这样做能够提高在复杂电磁环境下的测向性能。2004年G.Lerosey等人第一次成功地将时间反转技术应用到了电磁实验中。将时间反转技术引入到辐射源目标探测领域中,通过对其原理的分析可知该技术具有良好的抗干扰性,适用于复杂的电磁环境。同时还对时间反转理论的具体算法进行了分析和比较,发现其计算简单、易于硬件工程实现的优势[2]。

本文以提高系统运算速度、实现测向的实时性为基本要求,利用现有的技术提出一种基于虚拟时反被动DOA估计算法的FPGA并行实现方案,通过该方案的设计与仿真实现,增强学生的主观能动性,进一步提高该课程的教学质量。首先给出硬件设计方案的原理,然后介绍该算法的硬件并行实现模块的IP核,最后通过Xilinx公司的Virtex-7信号处理板完成实验设计与验证[3]。

二、测向系统的FPGA设计方案

通过天线阵接收一段时长的待测信号,然后利用一个测向系统对信号进行处理,该系统由A/D采集模块、双倍速率(Double Data Rate3,DDR3)数据传递模块、虚拟时反被动测向并行算法的FPGA实现模块以及上位机中能量最大值搜索模块组成。首先使用AD采集卡采集一段待测的盲信号,通过DMA方式存入DDR3中待用,将与之对应的时延补偿点以及下变频数据由上位机计算完成后,通过PCIE总线协议(Peripheral Component Interconnect Express,PCIE)利用XDMA核将其存入DDR3对应地址中,以上数据都需要存在DDR3的固定地址。通过寻址方式将DDR3的数据利用DMA写入虚拟时反被动测向的FPGA实现模块,进行时延补偿,使信号波形对齐,把运算结果再通过DMA方式存入DDR3固定地址下,最后通过PCIE上传至上位机,进行能量最大值搜索,找到的最大能量值所对应的位置即为信源所在方向。数据的采集与传输采用文献中的设计方案,本章重点介绍该系统中虚拟时反被动测向并行算法的FPGA实现模块的设计[4]。

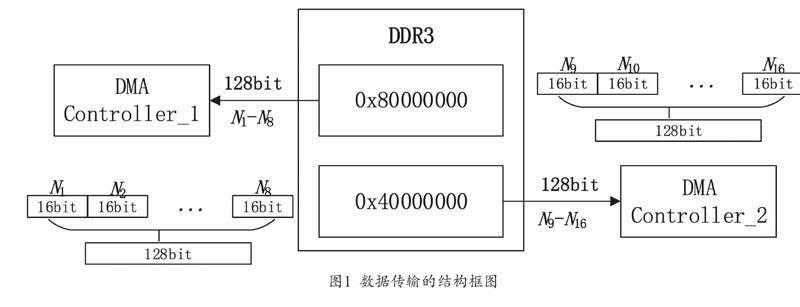

(一)双通道数据传输原理

为了实现数据高速移动,且保证数据流不被阻塞,本文提出了一种基于FPGA的双通道设计方案。两个通道的数据移动分别由直接存储器访问(Direct Memory Access,DMA)控制器实现。在设计中,需要知道数据的基地地址和DDR3的数据量。这种设计不受天线阵阵型的限制,本章以16阵元的阵列进行设计。两个通道待测信号分别存储在DDR3的指定区域,数据的基址为0x80000000段和0x40000000段。每个地址单元存储128bit数据,128bit数据代表8个16bit信号。为了更直观地展示上述过程,给出了数据传输的结构框图,如图1所示。图中N1-N8和N9-N16分别表示天线阵16个阵元接收到的数据。设天线阵有16个阵元,可将该阵列接收的信号分为两组,即2个8元天线阵进行计算,整个设计分为两个相同的通道。这两个通道同时处理8个阵元接收的信号,数据移动方式和信号处理方式相同,但数据存储的DDR3地址区域不同。由于两条通道的设计原理是相同的[5],为简便起见,下面将以一个通道(即8阵元的天线阵)为例进行描述。

(二)搜索域并行处理原理

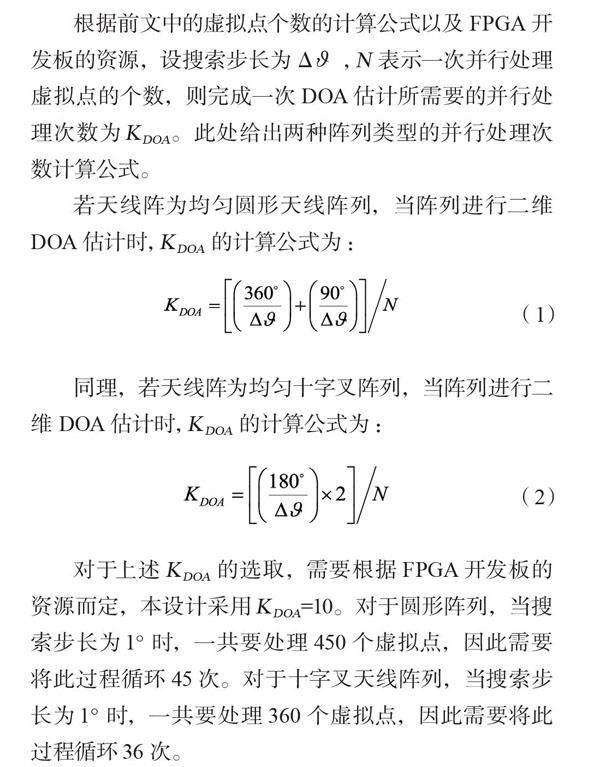

根据前文中的虚拟点个数的计算公式以及FPGA开发板的资源,设搜索步长为Δ? ,N表示一次并行处理虚拟点的个数,则完成一次DOA估计所需要的并行处理次数为KDOA。此处给出两种阵列类型的并行处理次数计算公式。

若天线阵为均匀圆形天线阵列,当阵列进行二维DOA估计时,KDOA的计算公式为:

同理,若天线阵为均匀十字叉阵列,当阵列进行二维DOA估计时,KDOA的计算公式为:

对于上述KDOA的选取,需要根据FPGA开发板的资源而定,本设计采用KDOA=10。对于圆形阵列,当搜索步长为1°时,一共要处理450个虚拟点,因此需要将此过程循环45次。对于十字叉天线阵列,当搜索步长为1°时,一共要处理360个虚拟点,因此需要将此过程循环36次。

(三)硬件设计原理

测向系统的整体框图如图2所示,本文将待测的信号存入计算机中,并利用计算机计算时延补偿点以及下变频数据,以上数据都通过PCIE方式写入DDR3的固定地址中。通过DMA方式将DDR3的数据传输至FPGA中,并利用寻址方式分别写入Memory_delay和Memory_data1~ Memory_dataN模块中。Memory_delay中保存时延补偿点,Memory_data1~ Memory_dataN分别保存天线阵1~N阵元的数据。下一步将DDR3中下变频的数据利用DMA传输方式传出,并与已保存的Memory_data1~ Memory_dataN中的数据做乘法运算,将结果经过低通滤波器(LPF)进行滤波,得到下变频后的信号。然后将该信号输入到循环并行处理模块,该模块中SP表示全部扫描点数,Q表示第几次循环,其中Q=1,2,…,SP/M。M表示循环一次能够处理的扫描点,M的选择主要与信号处理板的资源有关,并且最好选择能够被SP整除的值。令每个扫描点处理模块都有N路数据,利用控制数据存储模块的读使能将扫描点处的多路信号对齐并输出,读使能信号是由Memory_delay中的时延补偿点通过Delay Control module将时延点转换为读使能信号Rd_enN_M。将第M个模块输出的N路数据SP_dataN_M通过加法器组求和并求其能量值。由于资源有限,因此在硬件设计中扫描点能量值运算使用求信号和的绝对值来替代求信号和的平方。将最终求得的扫描点能量值E1~EM都保存在FIFO_energy中,当所有扫描点的能量值全部计算完成后,控制FIFO_energy的读使能,将数据通过DMA的方式传输到DDR3中,最后通过PCIE的方式上传至计算机中进行最大能量值搜索。

三、实验分析

一次并行处理的测试点越多,测向实时性越好,但是还要考虑硬件资源的问题,在设计与调试过程中,根据经验,不应占用全部资源,否则会使测向结果不稳定。

本设计中的算法由Verilog编程语言设计并将其封装成Custom IP核,如图3(a)所示,将Custom IP核与DMA控制器、MicroBlaze核和DDR3控制器相连。然后我们利用Vivado软件的Synthesis and Development以及Generate Bitstream完成系统设计。综合将高级抽象电路描述转换为低级描述,实现用于系统布局和布线。在上述两个进程中未报告任何错误时,通过Generate Bitstream函数生成Bitstream文件。最后将生成的比特流文件通过平台电缆USB下载到FPGA板上,利用MicroBlaze核,通过SDK平台植入C代码指令控制整个测向系统,测试结果在上位机显示。假设天线阵列是一个16阵元均匀分布的圆阵,系统时钟为200MHz,信号类型为BPSK调制信号。本设计并行处理一次的测试点为10个,则经过布局布线生成比特流后,能够得到FPGA信号处理板资源利用率如图3(b)所示,该占用比例不影响测向结果[6]。

以对称的去中心阵元十字叉天线阵列为例,根据该设计给出16阵元的去中心十字叉天线阵列,需要改变一次测向循环的次数,且预存的数据也按照十字叉天线阵列设计。利用vivado软件自带的仿真功能将测试结果进行了记录,并通过软件给出了误差曲线。假设测试点选取的是 ,则测向结果如图4所示。

四、结语

本文设计一种并行结构实现算法的硬件实现方案,通过Vivado软件利用Verilog编程语言将该设计封装成一个IP核,通过SDK平台与C语言指令来控制数据搬移等功能。最终采用Xilinx公司的FPGA信号处理板完成该设计的验证,实验结果表明,该算法在保证较高的测向精度的同时能够完成系统的实时测向。通过实践周的方式在两个班级中进行授课,通过课堂表现以及作业和考核的成绩显示,本次改革从根本上解决了学生对FPGA技术入门难的问题,也提高了教师的教学和科研能力。

参考文献

[1]杨一峰.硬件辅助验证产品解读之FPGA开发板vs原型验证系统[J].中国集成电路,2022,31(7):27-30+47.

[2]刘博,范玉进,张建军.基于FPGA的多通道可编程DDC算法研究与实现[J].消费电子,2021(8):21-22.

[3]赵英潇,苏阳.基于FPGA的多通道雷达数据回放系统设计[J].电子科技,2023,36(2):1-6+21.

[4]翁天恒,袁永春,周榕,等.基于FPGA的DDR4多通道控制器设计[J].电子测量技术,2022,45(12):148-155.

[5]Jing LY,Zhang NM,He CB,et al.OTFS underwater acoustic communications based on passive time reversal[J].Applied Acoustics,2022,185:108386.

[6]刘海涵,吕卫祥.基于时间反转变换的动目标相参积累算法[J].现代防御技术,2022,50(2):67-75.

基金项目:1.贵州省教育厅高等学校科学研究项目“基于虚拟时反法的5G精确定位关键技术研究”(黔教技〔2022〕263号);2.贵州省教育厅自然科学研究项目(黔教技〔2022〕029号、黔教合KY字[2021]022)