一种数字波束合成处理架构及其子阵设计

李 杰,李 翔,侯京辰

(成都振芯科技股份有限公司,四川 成都 610000)

0 引 言

基于数字波束合成(DBF)技术的数字相控阵具有灵活多变的波束控制及调度功能,易于实现收/发并行多波束,支持自适应数字波束形成(ABDF)功能。与传统模拟相控阵相比,数字相控阵在多目标并行跟踪、抗干扰能力、瞬时动态范围、杂波抑制等方面具有明显优势[1-3],可用于雷达[4-6]、电子对抗[7-9]、卫通测控[10-11]等领域,应用前景广泛。

DBF处理架构是数字相控阵系统的核心技术之一,直接影响数字相控阵系统的成本、尺寸、功耗、功能性能、技术先进性、可重构特性等指标。常见的DBF处理架构采取电传输及多级合成的分布式处理方案,技术成熟,但是系统体积大,难以满足收发通道与数字处理分开的技术发展趋势。本文以某数字相控阵项目的DBF处理架构为研究对象,考虑技术先进性以及较高的尺寸限制,并着眼于未来技术发展趋势,提出了一种基于光传输的集中式DBF处理架构,并完成对其可重构处理子阵的详细设计、样机制造及试验验证。

1 数字波束合成处理架构设计

根据某项目需求,针对数字波束合成处理架构问题,提出2种解决方案:(1)电传输及分布式处理架构;(2)光传输及集中式处理架构。下面研究分析2种处理架构的详细方案及其优缺点,在此基础上确定该项目的数字波束合成处理架构。

1.1 电传输及分布式处理架构

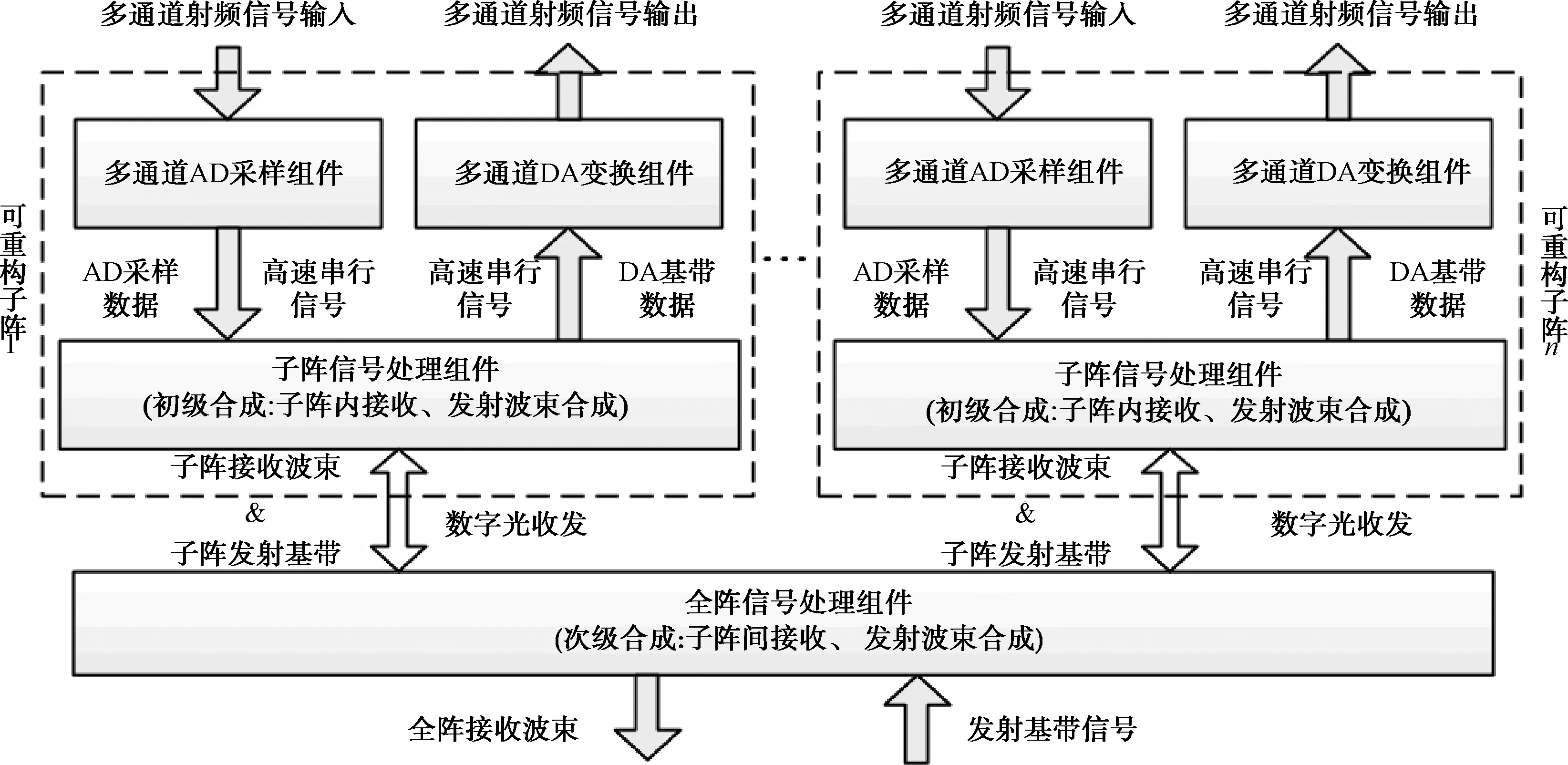

电传输及分布式数字波束合成处理架构如图1所示,其主要特点为:

图1 电传输及分布式数字波束合成处理架构

(1)在结构尺寸满足要求的情况下,信号处理组件位于各个可重构子阵内部,系统整体结构更加紧凑,但是单个可重构子阵的尺寸增加,对系统尺寸的要求更高,是一种较为传统的处理架构方案;

(2)采用分布式数字波束合成处理架构,各个可重构子阵独立完成初级波束合成,再由全阵信号处理组件完成全阵波束合成;

(3)各个可重构子阵对外输出波束合成数据,合成波束个数远小于通道个数,数字光收、发组件的成本更低;

(4)单个可重构子阵结构紧凑,信号处理组件、模数转换(ADC)采样组件和数模转换(DAC)组件同在一个子阵内部,距离近,大规模通道数据的高速传输可采用电传输方案,成本低;

(5)通过子阵重构,可实现任意规模阵列的扩展。

1.2 光传输及集中式处理架构

光传输及集中式数字波束合成处理架构如图2所示,其主要特点为:

图2 光传输及集中式数字波束合成处理架构

(1)信号处理组件独立于各个可重构子阵,可重构子阵的结构更加紧凑;

(2)数据采集和数据处理相互独立,子阵波束合成处理和全阵波束合成处理集中在具有超大规模计算能力的全阵信号处理组件中完成;

(3)集中式处理架构是一种较为先进的处理架构,符合数字阵列的发展趋势,如智能蒙皮、模数/数模(AD/DA)转换前移、超高速光传输、集中式信号处理等;

(4)信号处理组件独立于各个可重构子阵,信号处理组件与ADC采样组件、DAC变换组件的距离较远,为提高传输可靠性,需采用光传输方案,成本较高;

(5)通过子阵重构,可实现任意规模阵列的扩展。

1.3 对比分析及结论

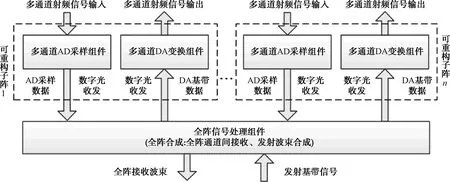

根据分布式处理架构方案及集中式处理架构方案的特点,2种方案对比分析结果如表1所示。

根据表1 的分析结果可知,光传输及集中式处理架构比电传输及分布式处理架构在技术先进性、技术发展趋势契合度、尺寸规模等方面具有明显优势,但是光传输及集中式处理架构的技术实现难度及成本较高。

表1 数字波束合成处理架构方案对比分析结果

光传输及集中式处理架构的技术实现难度和成本主要受限于高速、高容量数字收发光模块。根据前期技术调研,国内部分厂家可研制满足技术要求的收发光模块。随着技术的发展,数字收发光模块的技术稳定性和成本将逐渐改善,可进一步降低光传输及集中式处理架构的技术实现难度和成本。

综合以上分析,考虑项目的技术先进性以及较高的尺寸限制,并着眼于未来技术发展趋势,拟采用光传输及集中式数字波束合成处理架构方案。

2 可重构处理子阵设计

2.1 功能视图

根据图2可知,基于子阵重构方法,可实现阵列通道数目的任意扩展,可重构子阵是阵列的最小功能颗粒,其功能视图如图3所示。可重构子阵主要完成接收采样、发射数模变换、数字光发射、数字光接收、多接收通道同步、多发射通道同步及状态监控等功能。

图3 可重构处理子阵功能视图

2.2 硬件架构

可重构子阵的硬件组成如图4所示,包括4个ADC采样组件、4个DAC变换组件、1个信号转接组件以及1个模拟光接收组件,核心元器件或者模块包括64路ADC、64路DAC、数字光收发组件、模拟光收发组件、时钟分发模块、现场可编程门阵列(FPGA)配置芯片等。

图4 可重构处理子阵硬件架构

2.3 总线关系及互联逻辑

可重构处理子阵总线关系及互联逻辑如图5所示,外部交互接口包括64路射频信号输入、64路射频信号输出、多路数字光输入及输出、系统同步SYNC信号模光接口、系统参考时钟SYSCLK模拟光接口、供电及系统控制调试接口,其中:

图5 可重构处理子阵总线关系及互联逻辑

(1)64路射频信号输入由ADC采样组件完成采集,通过数字光发送模块送入阵列的信号处理组件完成波束合成;

(2)DAC变换组件的数字光接收模块接收来自信号处理组件的数字基带数据,并由DAC芯片完成64路射频信号输出;

(3)系统同步SYNC信号、系统参考时钟SYSCLK信号由模拟光组件完成接收,并进行光电转换;

(4)信号处理组件通过控制调试接口实现对可重构子阵的配置和控制;

(5)信号转接组件接收模拟光组件的同步SYNC信号及系统参考时钟SYSCLK信号,产生ADC组件、DAC组件所需的同步信号和时钟信号。

2.4 功能软件架构

阵列系统的软件架构组成如图6所示,主要包括接口通信、芯片配置、系统控制以及波束合成等功能。其中:

图6 可重构处理子阵功能软件架构

(1)信号处理模块的FPGA1驻留接口通信程序、系统控制程序、波束合成程序以及芯片配置程序,用于完成上位机通信、系统控制、发射/接收波束合成以及信号处理模块芯片的基础配置;FPGA2、FPGA3、FPGA4驻留接口通信程序和波束合成程序,用于完成各自FPGA的对外通信交互及发射/接收波束合成;

(2)可重构子阵的信号转接组件、ADC采样组件、DAC变换组件驻留接口通信程序和芯片配置程序,用于完成各组件上FPGA_A7的对外通信交互及芯片的基础配置。

3 试验分析

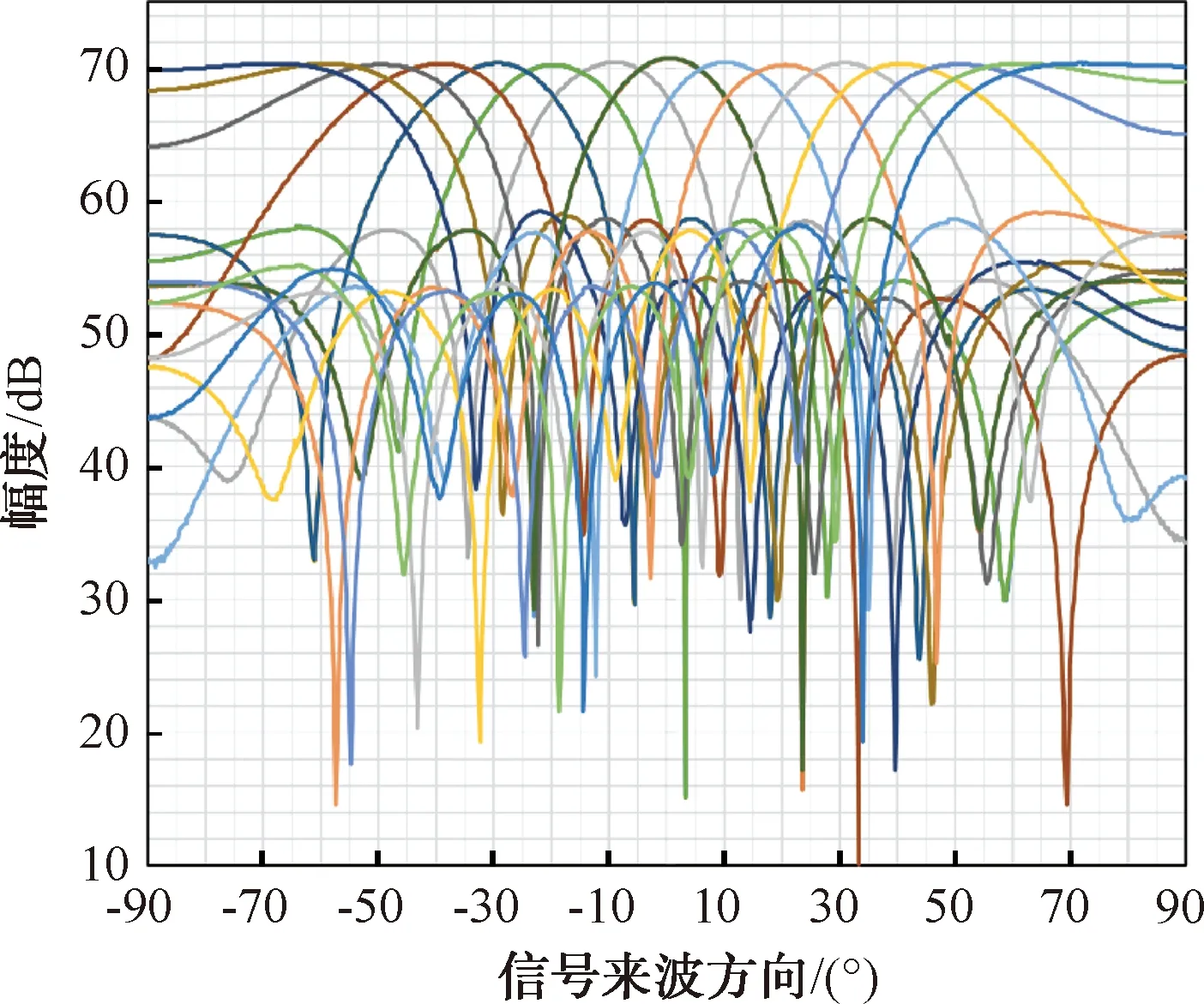

根据前述分析,设计制造的可重构处理子阵实物如图7所示,与信号处理子阵配合,可同时完成64(8×8)通道接收、发射数字波束合成。为测试波束合成结果,搭建如图8所示的波束方向图扫描测试系统。

图7 可重构处理子阵实物

图8 可重构处理子阵波束方向图扫描试验框图

测试流程说明如下:

(1)外置信号产生设备,按照时序要求,生成可重构子阵所需的SYNC信号和SYSCLK信号,电光转换后,发送给可重构子阵;

(2)可重构子阵的DAC输出接入可重构子阵的ADC输入;

(3)获取通道间的幅相不一致性,并进行通道校准;

(4)信号处理组件集成发射数字波束合成功能和接收数字波束合成功能,通过发射波束合成功能模拟不同来波方向对应的时差和相位差,并通过可重构子阵的DAC输出满足通道间时差和相位差要求的射频信号;

(5)可重构子阵的ADC采集DAC输出的模拟不同来波方向的射频信号,信号处理组件的接收波束合成功能完成接收波束合成,并提取波束幅度;

(6)发射波束合成功能完成全空域模拟来波方向扫描,通过接收波束合成,即可形成全空域的波束方向图。

按照上述流程,仅考虑一维8通道数字波束合成,采集完成的波束方向图如图9所示。其中,波束指向从左到右依次为-70°~70°,按照10°步进。根据图9可知,各个合成波束的指向正确,主副瓣比符合理论分析结果,设计的可重构子阵可用于任意规模数字阵列的扩展重构。

图9 可重构处理子阵波束方向图扫描结果

4 结束语

针对某数字阵列项目需求,考虑项目的技术先进性以及较高的尺寸限制,并着眼于未来技术发展趋势,设计了一种光传输及集中式数字波束合成处理架构,并对该处理架构的可重构处理子阵进行了详细设计。基于该处理架构以及可重构处理子阵,可实现任意规模数字阵列的扩展。为验证处理架构、可重构处理子阵设计结果的正确性,搭建试验系统,获取了可重构处理子阵实物的数字波束合成方向图。测试结果表明,可重构处理子阵合成波束的指向正确,主副瓣比符合理论分析结果,可用于任意规模数字阵列的扩展重构。