多重场限环型终端结构的优化设计*

卓宁泽,赖信彰,于世珩

(江苏长晶科技股份有限公司,南京 210000)

1 引言

功率半导体器件作为电力控制的核心电力电子器件,广泛应用于电能的变换和控制[1]。近年来,随着5G 通讯的发展,新能源汽车、高速列车、光伏、风电、手机、电脑、电视机、空调等各个领域对于功率半导体器件的需求量大大增加。金属氧化物半导体场效应晶体管(MOSFET)[2-4]作为一种重要的功率半导体器件,通过电压控制其栅极,既能完成器件导通,又可以实现关断,具有高输入阻抗和低导通损耗的优点,广泛应用于开关电源、电机控制、移动通讯等领域。沟槽MOSFET 是一种新型垂直结构的MOSFET 器件,其在传统平面MOSFET 结构基础上发展而来,沟槽MOSFET 由于将沟槽深入硅体内,在设计上可以并联更多的元胞,从而降低导通电阻,实现更大的导通电流和更宽的开关速度[5-7]。中高压沟槽MOSFET 器件的终端结构与衬底漏端电压差很大,容易导致表面电场集中,从而引起MOS 器件终端位置的击穿,因此为了保证器件可以在中高压条件下正常使用,需要对终端结构进行优化设计,以降低表面电场强度,提高器件的整体耐压水平[8-10]。赵磊等[11]设计了一种横向变掺杂结构终端,长度为118 μm 时,击穿电压达700 V;刘岳巍等[12]设计了一种具有分组缓变间距场限环结终端结构的碳化硅功率MOSFET,此结构有效调制并优化了结终端区域的表面电场强度分布,并基于可靠性评估了终端结构的稳健性和可行性。何进等[13]采用与平面结物理机理最接近的圆柱坐标对称解进行分析,提出了平面结场限环结构的电压分布和边界峰值电场的解析理论。本文设计开发了一种硅基MOSFET 用多重场限环型终端结构,研究了体区注入剂量、场限环宽度和主结宽度对终端击穿电压的影响,并对微观物理图像进行了描述。

2 多重场限环型终端结构模型

本文设计的多重场限环型MOSFET 终端结构如图1 所示,其特点是多重场限环的实现不需要额外增加一层光罩,仅在器件体区光罩中增加对应的终端区域开窗,即可与体区注入同步实现终端场限环的形成,简化了流程,降低了制备成本。

图1 多重场限环型MOSFET 终端结构

结合图1 给出相关参数值:外延层阻值1.55 mΩ、厚度8.7 μm,沟槽宽度0.45 μm、深度1.3 μm,源极接触孔宽度0.45 μm、深度0.4 μm,栅氧化层厚度0.08 μm,隔离氧化层厚度0.5 μm,源极金属层厚度4 μm,体区注入剂量1.1×1013~1.7×1013cm-3,源区注入剂量4.5×1015cm-3,主结宽度(Wmj)5~11 μm,场限环宽度(Wring)1~2.5 μm。

3 分析与讨论

3.1 体区注入剂量

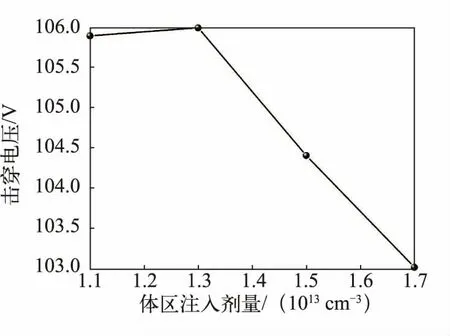

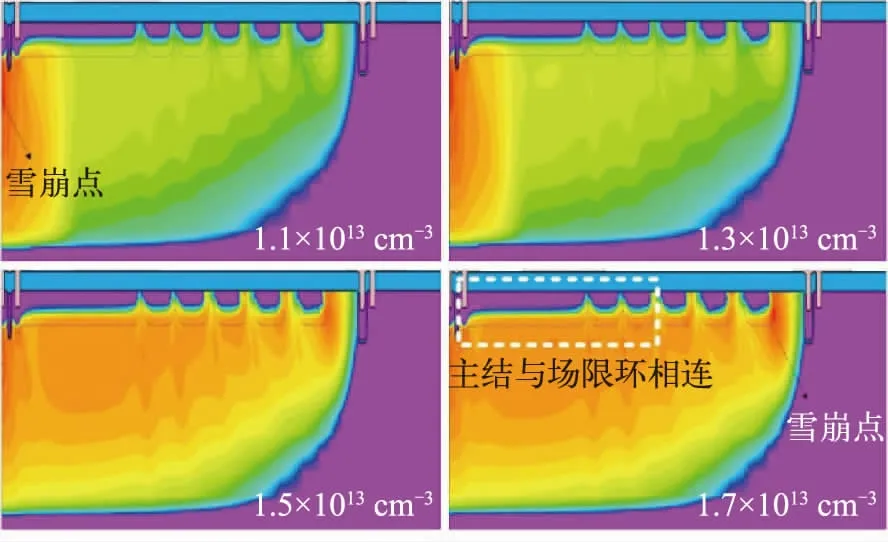

不同体区注入剂量(1.1×1013cm-3、1.3×1013cm-3、1.5×1013cm-3、1.7×1013cm-3)下的击穿电压如图2 所示,可以看出,随着剂量的增加,击穿电压表现出先升高后降低的趋势,在1.3×1013cm-3剂量时具有最大值(106 V)。不同注入剂量时碰撞电离分布和PN 结分布如图3 所示,可以看出,随着剂量的增加,由于注入-退火过程中的侧扩,主结与场限环间距逐渐减小,在1.7×1013cm-3时主结与其相邻的两个环相通,这种现象会引起场限环分压降低,导致击穿电压降低;同时,最大碰撞电离的位置点从元胞区向终端发生了移动,这种偏移会导致产品可靠性降低。综合以上分析,选择1.3×1013cm-3为注入剂量最优值。

图2 不同注入剂量下的击穿电压

图3 不同注入剂量时的碰撞电离分布和PN 结分布

3.2 场限环宽度

不同场限环宽度(1 μm、1.5 μm、2 μm、2.5 μm)时击穿电压和电势如图4 所示,图中X 为终端结构尺寸,击穿电压表现为先升高后降低的趋势,宽度为1.5 μm和2 μm 时具有最大值(106 V),其主要原因是在场限环宽度较小时,耐压主要由主结承担,随着宽度的增加,场限环分压后对应击穿电压升高,当宽度继续增加后,主结与场限环会相互穿通变成一个环,从而降低了承压的能力,从电势曲线也可以看出,在2.5 μm宽度时,存在场限环相连分压降低的现象。对应的电场分布如图5 所示,可以看出,随着宽度的变化,电场峰值位置会移动,在宽度为1.5 μm 时,各电场峰值相差不大,不存在特别高的设计弱点,因此选择1.5 μm作为场限环宽度最优值。

图4 不同场限环宽度时的击穿电压和电势

图5 不同场限环宽度时的电场分布

3.3 主结宽度

不同主结宽度(5 μm、7 μm、9 μm、11 μm)时的击穿电压和电势如图6 所示,可以看出,随着主结宽度的增加,击穿电压逐渐升高,其原因是在主结宽度较小时,耗尽区连续性较差,仅有主结进行承压,场限环没有起到明显的分压环作用,即此时的场限环对于主结形成的耗尽区曲率半径没有起到调节优化作用,雪崩击穿发生在主结边缘处;随着主结宽度的增加,其耗尽区与场限环能够形成连续分布,场限环的分压能力得到实现(从电势分布可以看出,随着主结宽度的增加,主结分压得到优化),耗尽区曲率半径增加,球面结影响降低,缓解了电场在耗尽区拐角处的集中,从而提高了击穿电压值。对应电场分布曲线如图7 所示,可以看到,主结宽度为5~7 μm 时电场峰值在主结处。碰撞电离分布和PN 结分布如图8 所示,可以看出,主结宽度较小时,雪崩击穿点在主结附近,宽度增加到11 μm 时,击穿点移动至元胞区,同时主结曲率得到了优化,因此选择11 μm 作为主结宽度最优值。综合以上研究,获得了多重场限环型终端最优结构和工艺参数:体区注入剂量为1.3×1013cm-3,场限环宽度为1.5 μm,主结宽度为11 μm,对应击穿电压为106 V。

图6 不同主结宽度时的击穿电压和电势

图7 不同主结宽度时的电场分布

图8 不同主结宽度时碰撞电离分布和PN 结分布

3.4 试验验证

终端版图设计如图9 所示,包含沟槽层、P 注入层、金属层、金属接触层等,根据实际流片工艺获得器件的击穿电压为105.6 V,良率为98.65%,说明了此次仿真设计的准确性,器件的转移特性和输出特性曲线如图10、11 所示。根据图10 可知,对应器件的阈值电压为2.72 V@250 μA。当栅源电压小于2.72 V 时,未形成导电沟道,器件无电流流过;当栅源电压大于2.72 V 时,体区能带反型形成导电沟道,并且随着栅源电压的增大,电流逐渐增大;当栅源电压增大到一定程度时,电流的增大趋势变缓,由于载流子速度饱和,器件进入准饱和区,电流随栅源电压的增加几乎保持不变。从图11 中可以看出,随着栅源电压的增加,曲线斜率升高,根据欧姆定律,器件的导通电阻下降,这是因为栅源电压增大,对应反型电荷数目增加,导电沟道开启得更彻底,因此对应器件的导通电阻更低。

图9 终端版图设计

图10 硅基MOSFET 转移特性

图11 硅基MOSFET 输出特性

4 结论

本文基于仿真工具对多重场限环型终端结构进行设计和研究,重点研究了体区注入剂量、场限环宽度、主结宽度对击穿电压的影响,并对其机理进行了分析,同时应用仿真工具对器件内部物理场的变化进行了描述。通过优化研究,获得了器件结构和工艺参数,体区注入剂量为1.3×1013cm-3,场限环宽度为1.5 μm,主结宽度为11 μm,对应击穿电压为106 V。试验开版流片器件的击穿电压为105.6 V,良率达到98.65%。以上说明了基于仿真工具研究多重场限环型终端结构的优势,其不仅可以提高设计速度,同时利用仿真工具对微观物理图像的描绘可以使器件性能调控机制更加清晰。