硅基光子集成芯片光纤陀螺

毛玉政,何 建,谢良平,万 洵,崔志超,李艾伦

(1.中国航空工业集团公司 西安飞行自动控制研究所,西安 710065;2.陆军装备部驻株洲地区航空军事代表室,株洲 412000)

基于光纤陀螺(Fiber Optical Gyroscope,FOG)的惯性传感器作为航空、航海以及陆地导航系统的关键组件,广泛应用于军事领域,其精度和可靠性直接影响武器平台的作战效能。未来小体积、低成本、中低精度的光纤陀螺在军用领域包括战术导弹制导、姿态控制、稳瞄、弹药制导化等,以及民用航空、自动驾驶、智能机器人等领域市场需求巨大。但目前传统光纤陀螺的核心器件均为分立封装,尺寸较大,装配工序多且耗时长,需要较多人力参与,生产规模及产能小,制造成本高,同时产品性能的一致性和长期可靠性也存在缺陷,这些不足已成为限制光纤陀螺大规模推广应用的瓶颈。因此,进一步降低光纤陀螺的生产成本,减小体积并大幅提高出货量,刻不容缓。

光纤陀螺根据控制方式的不同,可分为开环光纤陀螺和闭环光纤陀螺,其主要区别是闭环光纤陀螺采用高速调制的集成光学调制器(Y 波导)引入非互易相移,以补偿旋转引起的Sagnac 相移,实现闭环反馈;而开环光纤陀螺采用低调制频率的压电陶瓷(PZT)作为调制器件,施加偏置相位以增大工作响应灵敏度。近年来,随着集成光学设计、微纳加工水平的不断提高,利用光子集成芯片代替传统光纤分立器件以实现小体积、低成本、可大规模批量生产的光纤陀螺技术,引起了广泛关注。其中硅基光子芯片因其与集成电路的CMOS 工艺兼容,工艺相对成熟,易于实现规模化量产,且具备最终实现陀螺有源器件与无源器件单片混合集成的潜力,逐渐成为光子集成芯片光纤陀螺的主流方案。目前国内外许多单位包括:美国加州大学(UCSB)[1-3]、加州理工大学[4]、KVH 公司[5]、Honeywell 公司[6],英国Bookham 公司[7],国内航天33 所[8-10]等均在集成化光纤陀螺方面开展了相关研究,且大多基于闭环架构。其中,UCSB 的Tran 课题组在美国DARPA 支持下设计了用于FOG 的光子芯片,4.5 mm2的硅基芯片上集成了光源、探测器、调制器、3 dB 耦合器,并进行了陀螺验证,精度数百度/时;2020年KVH 公司发布一款基于开环架构的光子集成芯片惯性测量单元P-1775,其在光学芯片上集成了2 个耦合器和1 个起偏器,精度比MEMS 陀螺高十几倍以上,却拥有与MEMS 陀螺可比拟的成本优势,后续针对不同的应用需求,相继发布了P-1725,P-1755等不同精度的光子集成芯片IMU,相应产品已经应用于运载火箭、无人机、无人驾驶等领域,这也是目前国内外公开报道的唯一成熟应用的光子集成芯片光纤陀螺。

总体来看,由于高调制速率、大带宽、高线性度的片上调制方案尚不成熟,目前受关注较多的片上薄膜铌酸锂电光调制器在低损耗设计与批产工艺等方面仍需进一步研究[11],因此基于闭环架构的单片集成光纤陀螺尚处于原理样机研究阶段,而基于开环架构的无源器件芯片集成的光纤陀螺在国外已实现了产品级的应用。而国内集成光学微纳加工产业尚未形成规模,同时受限于工艺精度水平,相关研究几乎为空白。研究团队在长期从事传统开环光纤陀螺设计、光纤器件制作、陀螺控制算法研究的基础上,开展了光子集成芯片光纤陀螺研究。本论文基于国内微纳加工水平现状,提出了一种工艺精度要求相对较低的硅基光子集成芯片光纤陀螺设计方案,并进行芯片工艺冗余设计,可实现光子芯片的完全自主可控;完成了硅基光子集成芯片的加工、耦合测试,并与超细径保偏光纤阵列快速封装,实现了光子集成芯片光纤陀螺原理样机。

1 陀螺光路方案设计

传统开环光纤陀螺的光路结构如图1所示,主要由超辐射发光二极管(SLD)、耦合器1、起偏器、耦合器2、光纤环、压电陶瓷(PZT)调制器等几部分构成。SLD 光源发出的光包含两种不同偏振模式TE0 与TM0,经耦合器1 分束,一部分光进入光纤死端被吸收耗散,另一部分光进入起偏器,由于起偏器的偏振模式选择,变成线偏振光继续传输;经耦合2 分成两束光进入光纤环,分别沿顺时针和逆时针方向传播,且满足相干条件;当光纤环绕其中心轴旋转时,产生Sagnac 效应,从而回到耦合器2 的干涉光强发生变化,PZT 调制器对顺、逆两束光施加一非互易相位偏置,使得光纤陀螺相位检测灵敏度最大;干涉光信号经耦合器2、起偏器、耦合器1 进入探测器,检测旋转引起的光强变化,通过陀螺检测电路解调得到旋转角速率信息。

图1 开环光纤陀螺光路结构Fig.1 Scheme layout of the open-loop FOG

光子集成芯片光纤陀螺主要是基于传统陀螺光路结构,利用平面光波导器件代替陀螺中的分立光纤器件,减少光纤器件互连,实现功能器件的片上集成,从而减小光路尺寸;借助光刻工艺,在单片晶圆上可一次加工成百上千颗光子芯片,器件一致性大幅提升,具有极大的规模生产效应,颠覆传统光纤陀螺制造模式;且光刻工艺中成本较高的光刻掩膜可重复多次使用,有效降低成本。

开环光纤陀螺光路中的功能器件可分为无源器件和有源器件两大类,其中无源器件包括耦合器1、偏振器、耦合器2 等;有源器件包括光源、探测器及调制器。无源器件多采用硅、二氧化硅等高透明材料,减小光与物质相互作用,降低损耗;有源器件需要光与物质强相互作用,多选用III-V 族化合物半导体、某些晶体等。因此两类功能器件需要不同的材料和结构来实现,目前有源器件与无源器件的单片异质混合集成尚不成熟。为了快速推进光子集成芯片光纤陀螺的工程化,本文采用一种目前相对较为容易实现的集成方案,其光路结构如图2所示。

图2 光子集成芯片光纤陀螺光路结构Fig.2 Scheme layout of the photonics integrated chip based FOG

光子集成芯片主要实现耦合器1、耦合器2、起偏器、模式转换器、光纤—波导低损耗端面耦合结构及片上杂散光吸收结构等多个无源器件的片上集成;调制器目前尚无成熟且低成本的片上解决方案,故仍采用PZT 结构;芯片波导与光纤环、SLD 及探测器通过一个四通道的超细径保偏光纤阵列实现快速耦合;为了减少熔点降低损耗,光纤阵列尾纤与SLD、探测器直接耦合,光纤环与阵列3、4 通道尾纤保偏熔接。

2 光子集成芯片设计、加工及测试

光子集成芯片是该光纤陀螺的核心部件,直接影响陀螺性能指标。常见的用于无源芯片设计材料主要有三种:绝缘体上硅(SOI)、硅基二氧化硅(SOS)及硅基氮化硅。传统开环光纤陀螺采用光源是中心波长为850 nm 的宽谱SLD 光源,SOI 波导的芯层为硅材料,硅吸收光子的截至波长为1100 nm,在850 nm波段是不透明的;SOS 波导芯层为重掺杂的二氧化硅,包层为二氧化硅,芯层—包层的折射率差小,导致器件尺寸较大,且很难实现特殊功能设计;而硅基氮化硅波导透明窗口可覆盖850 nm~1550 nm 整个波段,且波导传输损耗可以做到极低,因此采用硅基氮化硅波导结构来实现光子芯片设计。

利用硅基光波导结构进行了核心功能器件设计,主要包括四个关键难点:

(1)低损耗、均匀分束比的片上耦合器;

(2)低损耗、超高消光比片上偏振器;

(3)低损耗端面耦合结构;

(4)片上杂散光隔离抑制。

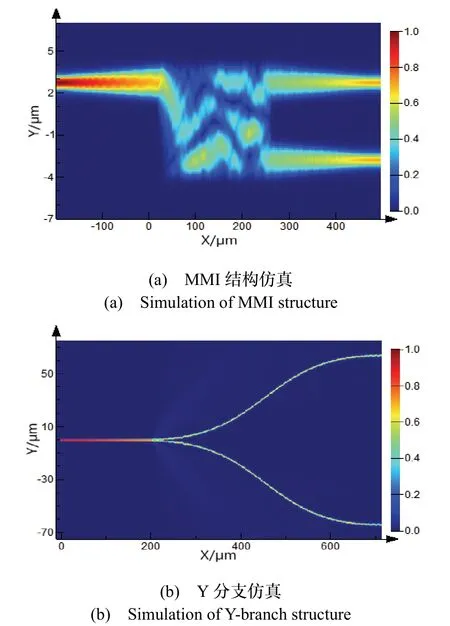

分别利用多模干涉(MMI)结构、Y 分支来实现3 dB 耦合器1、2,并结合工艺精度进行结构优化设计,增大加工误差容限,且耦合器输出两臂的间距与保偏光纤阵列通道间距相同;设计大宽高比硅基光波导,利用波导的结构双折射特性,实现高偏振消光比;针对波导与光纤折射率及模场不匹配导致的较大直接耦合损耗,设计优化倒锥结构以实现波导端面与光纤模场匹配,提高耦合效率。利用 Lumerical FDTD Solutions、Mode Solutions 软件进行建模仿真、参数优化设计。优化设计的MMI 结构、Y 分支仿真结果如图3所示,表明两种耦合器均可实现几近完美1:1的分束比,损耗<0.1 dB;通过优化设计倒锥结构,仿真可得到>88%的波导—光纤耦合效率;高消光比、低附加损耗的偏振器的设计是光子集成芯片实现的难点,经过多种方案探索,仿真实现了片上>60 dB 的消光比,附加损耗<0.2 dB。

图3 两种耦合器结构仿真Fig.3 Simulation of two coupler structures

利用国内某Foundry 厂248 nm 的深紫外(DUV)光刻工艺进行光子集成芯片加工,主要的工艺步骤是:在硅晶圆上利用等离子体增强型化学气相沉积(PECVD)生长二氧化硅下包层;为了提高波导芯层的生长质量,降低传输损耗,利用低压化学气相沉积(LPCVD)生长均匀致密的SiN 膜层;加工掩膜,利用光刻、刻蚀工艺形成波导结构,最后再生长上包层。芯片加工完成后,依次进行晶圆划片、芯片端面研磨处理,利用5 nm 超高精度六维耦合系统测试器件性能,如图4所示,分别与光纤及光纤阵列耦合测试。在显微镜下观察Y 分支、MMI 耦合器结构如图5所示,测试得到Y 分支耦合器:插入损耗0.43 dB,分光比优于48%:52%;MMI 耦合器:插入损耗0.40 dB,分光比优于47%:53%。通过优化设计端面倒锥结构,测试波导—光纤耦合损耗1.8 dB(耦合效率约66%)。

图4 光子集成芯片测试Fig.4 Experimental setups of the photonics integrated chip

图5 显微镜下两种耦合器结构Fig.5 Two coupler structures observed by microscope

相比波导与光纤的直接耦合,效率有大幅提升,但与仿真结果对比有较大差距,可能的原因是芯片加工工艺精度不足,而倒锥波导的尺寸较小,引起了较大的传输损耗。测试得到偏振器的消光比为31.3 dB,附加损耗<0.4 dB。光子集成芯片的核心功能器件性能基本达到应用需求,单颗光子芯片尺寸约4 mm×3 mm。

3 陀螺样机实现

为了实现芯片快速耦合封装,设计并加工了四通道60 μm/100 μm 超细径保偏光纤阵列,通道间距250 μm,如图6所示。其可实现四条波导与光纤的一次对接耦合,提高生产效率。光纤阵列的通道间距及保偏光纤对轴精度要求较高,以减小耦合损耗及退偏影响。测试加工的保偏光纤阵列消光比>25 dB,通道间距误差 ± 200 nm。

图6 四通道超细径保偏光纤阵列Fig.6 Four-channel ultra-fine polarization maintaining fiber array

对光子芯片与光纤阵列端面进行倾斜研磨,以降低端面反射对芯片性能影响。利用六维高精度调节台完成光子芯片与超细径保偏光纤阵列的耦合与紫外固化封装,封装后的光子芯片如图7(a)所示。为了快速验证光子芯片性能及直观地对比光子集成芯片光纤陀螺性能,利用封装的光子芯片对某型号传统光纤陀螺的光路器件进行了替换,而敏感光纤环、控制电路、结构均未改变。基于团队自研的超细径保偏光纤熔接机,实现60 μm 光纤阵列尾纤与40 μm 光纤环(长度约250 m)的保偏熔接,如图7(b)所示,陀螺,完成陀螺光路装配。进行陀螺控制电路调试、结构装配,搭建光子集成芯片光纤陀螺原理样机,如图8所示。

图7 光子芯片封装及陀螺光路熔接Fig.7 The photonic chip package and the gyro optical system fusion

图8 光子集成芯片光纤陀螺样机Fig.8 Photonics integrated chip based FOG prototype

4 样机测试分析

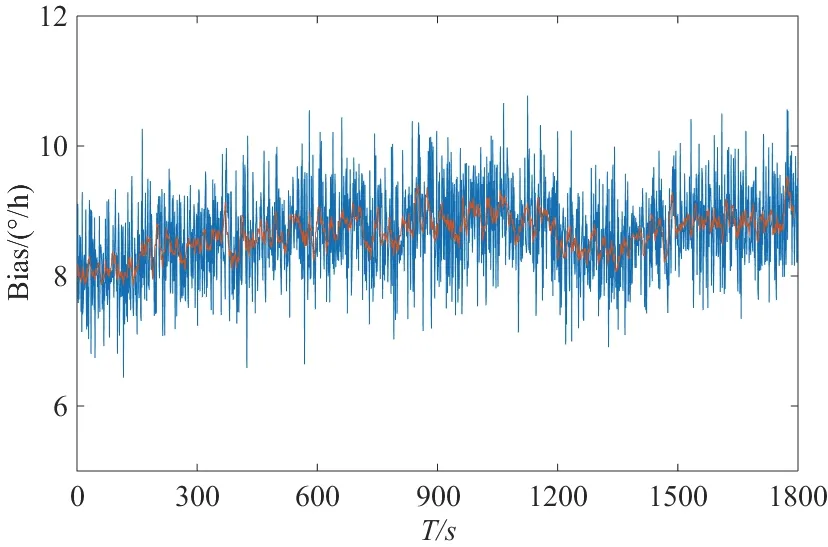

为了直观比较陀螺性能,分别对相同结构的光子集成芯片光纤陀螺与传统光纤陀螺的常温静态性能进行测试。测试过程中保持环境温度25℃,陀螺输出采样间隔1 s,数据采集时长1800 s。两个陀螺的常温零偏性能测试结果分别如图9 和图10所示,图中蓝线为陀螺原始零偏输出,红线为10 s 平滑处理结果。从图中可以看出,光子集成芯片光纤陀螺的漂移较小,测得相关陀螺参数及指标如表1所示。

图9 光子集成芯片光纤陀螺零偏测试Fig.9 The bias of the photonics integrated chip based FOG

图10 同结构传统光纤陀螺零偏测试Fig.10 The bias of the traditional FOG with same structure

通过计算,光子集成芯片光纤陀螺零偏稳定性0.2 °/h(10 s),而该相同结构的全光纤器件光纤陀螺的零偏稳定性0.3 °/h(10 s),陀螺零偏性能有一定提高,这与光子芯片对器件性能提升有关。设计的片上耦合器、偏振器,相比于传统拉锥器件,分束比更加均匀、消光比也有了提高,能够更好地抑制偏振误差及噪声。且与传统封装的拉锥耦合器与偏振器相比,利用光子芯片可将器件尺寸由约21mm ×16 mm减小至7 mm ×4mm,器件面积变为原来的十二分之一,这对进一步减小整个陀螺尺寸具有十分重要的意义。但是与传统光纤陀螺相比,光子集成芯片光纤陀螺的工作电流较大,这主要是因为陀螺采用功率反馈控制,工作中保持探测光功率不变,由于芯片波导与光纤的耦合损耗、光纤阵列尾纤与光纤环之间异径保偏光纤熔接损耗较大,导致陀螺光路损耗增大,SLD 的驱动电流变大,长期可能会影响光源寿命。这需要进一步优化光子芯片设计及耦合工艺,减小端面耦合损耗;选用同种芯径光纤绕环及加工保偏光纤阵列,或采取直接耦合方式减少熔点,以降低熔接损耗。

综上所述,利用硅基光子集成芯片实现了全部无源器件的片上集成,成功实现了陀螺样机,性能较好。但当前芯片性能还需进一步优化,同时芯片集成的器件相对较少,下一步将不断提高光子芯片集成度。随着微纳光学加工水平的不断提高及有源/无源器件异质混合集成技术的发展,未来有望实现功能器件单片集成,进一步减小光纤陀螺体积与成本,从而大规模批量生产。

5 结论

光纤陀螺的光路小型化、芯片集成化是发展的必然趋势。基于国内微纳工艺现状,本文提出了一种工艺精度要求相对较低较、易于快速工程化的硅基光子集成芯片光纤陀螺设计方案。基于开环光纤陀螺架构,实现了光纤陀螺无源器件的片上集成,并利用超细径保偏光纤阵列进行芯片与陀螺光路系统的快速耦合封装,搭建了光子集成芯片光纤陀螺样机,常温零偏稳定性可达到0.2 °/h,性能优于相同结构的传统全光纤器件光纤陀螺,相关研究可为未来实现全片上集成的光学陀螺奠定基础。