GaN基互补型逻辑电路的研究进展及挑战*

张彤,刘树强,何亮,成绍恒,李柳暗,敖金平

(1.枣庄学院人工智能学院,山东 枣庄 277160;2.工业和信息化部电子第五研究所,广州 510610;3.吉林大学超硬材料国家重点实验室,长春 130012;4.江南大学物联网工程学院,江苏 无锡 214122)

1 引言

功率电子器件(又称为电力电子器件)在发电、输电、变电、配电及用电过程中都发挥着重要的作用,目前约80%的电能经过功率电子电路进行转换或回收。功率电子电路的功率密度通常由无源组件(如电感和电容)的大小决定,通过增加开关频率可以大幅减少无源组件的储能需求而提升功率密度。当前主流的硅基功率器件最高电能转换效率约为90%、工作频率为MHz量级,且已经接近其材料理论极限。氮化镓(GaN)材料理论上能提供更高的开关频率和更高的电能转换效率,在保持合理开关损耗的同时可提升功率密度和瞬态性能,因此被越来越多地应用于面向快速充电、数据中心及激光雷达的高性能、紧凑型电源模块中[1]。功率电子电路例如功率变换器除了功率器件模块以外,通常还有栅驱动电路、保护电路、脉冲宽度调制信号发生器及反馈控制回路等外围子模块[2]。现有的混合集成方案中,GaN功率器件与其他外围电路之间的焊线和引线会引入寄生电感,在高频率开关过程中会导致开关损耗、振铃和可靠性问题。为了充分发挥GaN功率器件的潜能,将功率开关器件和控制器、驱动等外围电路进行全GaN单片集成是降低寄生参数的有效手段,也是GaN功率集成电路的重要发展方向。本文介绍了GaN基n沟道与p沟道增强型器件的发展历程以及互补型逻辑电路的研究进展,对GaN互补型逻辑电路面临的挑战进行了综述,并提出了潜在的解决方案。

2 互补型逻辑电路及其研究意义

传统的硅基功率电子电路中栅驱动的逻辑功能是通过互补金属-氧化物-半导体(CMOS)逻辑电路实现的,如图1(a)所示。CMOS逻辑电路由物理特性互补的p沟道MOS场效应晶体管(pMOS)和n沟道MOS场效应晶体管(nMOS)组成[3]。晶体管的互补特性造就了CMOS逻辑电路优异的性能:(1)用于多级电路的轨到轨输出电压(输入、输出电压匹配度高);(2)约为电源电压VDD(通常为5 V)一半的逻辑转换电压;(3)抑制静态功耗;(4)“低”和“高”逻辑都有足够的噪声容限。为了实现以上逻辑功能,pMOS和nMOS都需要实现增强型工作模式,阈值电压VTH接近逻辑转换电压,在整个栅极输入电压范围(0~VDD)内要有较低的栅极泄漏电流。对GaN基功率器件而言,Si衬底上AlGaN/GaN异质结结构可以具备大尺寸晶圆能力,且能够利用成熟的CMOS工艺产线[4]。目前,AlGaN/GaN基n沟道增强型器件电学性能及可靠性获得了明显的提升,但在互补型逻辑电路方面的发展严重滞后。

图1 逻辑电路的输出电压及准静态电流特性[3]

3 n沟道增强型器件及其单片集成电路发展现状

3.1 n沟道增强型器件制备技术

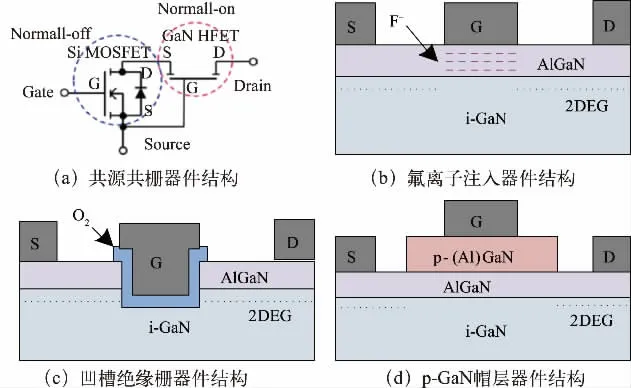

AlGaN/GaN异质结构中较强的压电极化和自发极化效应,导致异质界面存在高浓度的二维电子气(2DEG)。进而,器件在栅极零偏压或者悬空时无法耗尽2DEG沟道而处于导通状态(耗尽型器件)。为了满足功率器件失效安全及CMOS逻辑电路的需求,通常需要实现增强型工作。对于GaN材料而言,一般思路是保留接入区高导通能力的2DEG,耗尽或截断栅极下方的2DEG,以实现器件在零偏压下处于关断状态。目前业界普遍采用的增强型器件方案有4种,分别为:有共源共栅级联结构,如图2(a)所示;氟离子(F-)注入器件结构,如图2(b)所示;凹槽绝缘栅结构(MOSFET),如图2(c)所示;p-GaN帽层结构,如图2(d)所示。级联方案是将增强型硅基绝缘栅器件和耗尽型AlGaN/GaN异质结场效应晶体管(HFET)器件通过共源共栅的方法形成双芯片混合管[5]。这种结构能充分利用硅基MOS结构实现小的栅泄漏电流和更高的VTH,且与传统硅基驱动电路匹配。然而,键合金属线会引入寄生电感,削弱GaN器件的高频工作能力,而硅器件的引入会降低其高温工作能力。F-注入法利用F-的强负电性耗尽沟道中的2DEG,从而实现常关型器件[6],且F-注入会抬高AlGaN势垒层的能带并降低栅极漏电流,但离子注入会对器件有源区的晶格造成损伤,注入深度和浓度的均匀性很难保障。此外,该方案获得的VTH相对较小。绝缘栅结构通常利用等离子体完全刻蚀掉栅极下方的AlGaN势垒层,形成凹槽来耗尽2DEG,结合绝缘介质层形成MOSFET,以获得高的VTH、高栅电压摆幅和低栅极泄露电流[7],但是刻蚀表面的晶格损伤和介质层界面缺陷会导致稳定性问题。近年来,业界开发了高温刻蚀、湿法刻蚀及选择区域外延生长等新型低损伤方案以形成凹槽结构[8-10]。p-GaN帽层利用栅极下方的p-GaN层形成的空间电荷区提升沟道处的能带[11],从而耗尽沟道中的2DEG,实现常关型工作。该方法具有结构简单、VTH均匀性好、输出电流密度大的优点,但是其VTH不高(约1.5 V),栅极泄露电流在p-n结正向导通后明显增大。

图2 实现n沟道增强型GaN器件的技术方案

3.2 基于n沟道增强型器件的单片集成工艺平台

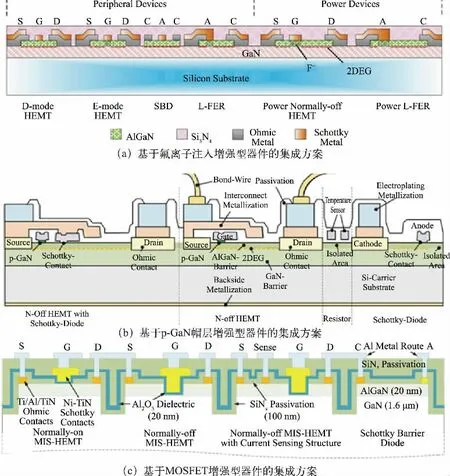

目前已有较多利用耗尽型GaN HFET实现集成栅驱动GaN半桥功率变换器的相关报道,然而由于器件VTH为负值、栅压摆幅小,需要额外电压源来提供负栅驱动偏压,导致功率变换器设计较为复杂。随着增强型器件制备技术的发展,采用增强型器件简化GaN集成电路的设计和工艺复杂度逐渐成为主流。2005年,香港科技大学基于氟离子注入方案实现了增强型GaN功率电子器件并进一步实现了GaN智能功率集成平台[12],集成方案如图3(a)所示。通过增强型与耗尽型HFET器件的直接耦合,晶体管逻辑(DCFL)实现了数字逻辑电路、反相器、环形振荡器等多种电路结构,集成方案如图1(b)所示。在此基础上,该团队于2009年实现了GaN基比较器和基准电压源等电路。2018年,德国夫琅和费应用固体物理研究所提出了一种基于p-GaN帽层增强型器件的全GaN单片集成工艺平台,集成方案如图3(b)所示。该工艺平台不仅实现了功率二极管、常关型晶体管以及集成续流二极管的功率晶体管,还设计了可用于集成的电流和温度传感器[13],进而设计了工作频率高达3 MHz的400 V转200 V全GaN降压功率IC。香港科技大学同样基于p-GaN帽层异质结构实现了功率晶体管、DCFL及电容、电阻等外围功能电路[14]。电子科技大学基于凹槽绝缘栅器件实现了功率器件、逻辑电路单元以及嵌入式电流传感器结构,进而实现了具有多种功能的全GaN智能功率变换器[15],集成方案如图3(c)所示。可以看到由于p沟道GaN器件的发展相对滞后,现有的GaN驱动芯片部分的逻辑功能是基于n沟道的耗尽型与增强型的DCFL。与CMOS结构相比,DCFL电路具有较大的驱动损耗且输出的低电平需要考虑上下管导通电阻的比值,这些缺点限制了系统效率的提升。因此,发展高性能GaN基互补型逻辑电路是实现GaN功率单片集成电路的核心基础及迫切需求。

图3 n沟道器件实现的GaN单片集成电路示意图[12-13,15]

4 p沟道增强型器件及互补型逻辑电路

4.1 二维空穴气及p沟道增强型器件

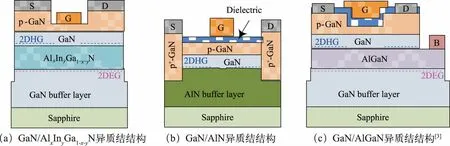

相比于n沟道增强型器件,实现高性能GaN基p沟道增强型器件面临较大的挑战。一方面,由于GaN材料本身高浓度的n型背景掺杂、高的Mg掺杂激活能(110~190 MeV)及自补偿作用,Mg掺杂的激活效率仅为1%左右。因此,p-GaN层的空穴浓度上限为1018cm-3、空穴迁移率约为10 cm2·V-1·s-1。另一方面,器件制备需要刻蚀凹槽并沉积介质层形成MOS结构,刻蚀损伤导致的界面会引起沟道载流子的散射而进一步降低沟道迁移率。一种潜在的解决方案是利用异质结构的极化效应诱导产生类似于2DEG的高浓度、高迁移率、无温度依赖性的二维空穴气(2DHG)沟道。从2000年SHUR等人基于GaN/AlGaN异质结首次实现2DHG沟道以来[16],业界相继在GaN/AlInGaN、InGaN/GaN、GaN/AlN等异质结结构中确认了2DHG沟道的存在[17-18]。2021年康奈尔大学基于GaN/AlN结构获得了浓度为2.2×1013cm-2及当前最高迁移率(280 cm2·V-1·s-1@10 K)的2DHG[19]。与此同时,国内外研究团队也相继报道了基于2DHG实现的GaN p沟道增强型器件。2013年,HAHN等人通过调整GaN/AlxInyGa1-x-yN中AlxInyGa1-x-yN背势垒层的Al和In的组分,有效调节了界面的2DHG浓度及p沟道器件的VTH,结合凹槽栅极结构及优化的背势垒层组分最终实现了增强型p沟道器件,异质结结构如图4(a)所示,亚阈值摆幅为60 mV/dec[20]。2013年,美国康奈尔大学团队通过在AlN衬底上外延生长5 nm的超薄GaN层实现了p沟道增强型器件,异质结结构如图4(b)所示;同时,引入了Al2O3作为栅介质层,有效降低了栅极泄漏电流[21]。2018年,NAKAJIMA等人在GaN/AlGaN异质结实现了p沟道增强型器件,结构如图4(c)所示,此外通过与p沟道晶体管下方的2DEG沟道形成欧姆接触引入一个额外的基极,通过该基极可以调节2DHG的电势,实现VTH的调控[17]。

图4 实现p型二维空穴气沟道的外延结构

4.2 GaN基互补型逻辑电路研究进展

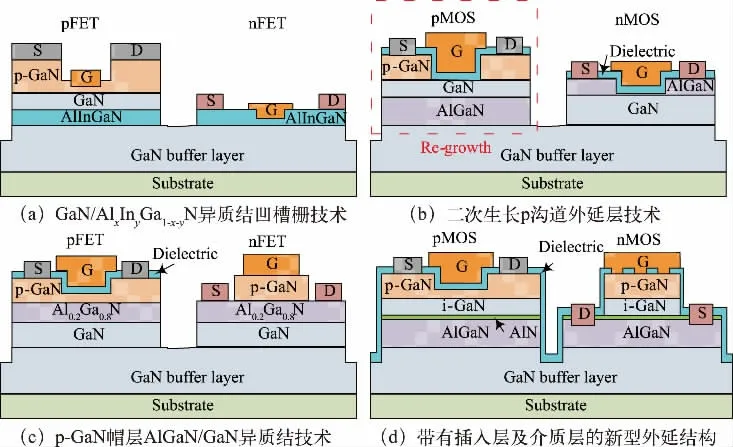

2014年,HAHN等人在蓝宝石衬底上的GaN/AlInGaN/GaN双异质结构中首次展示了具有n/p沟道增强型晶体管的集成技术并制备了互补型反相器[22],其结构如图5(a)所示。该结构在上层GaN/AlInGaN界面形成2DHG沟道且在下层AlInGaN/GaN界面形成2DEG沟道。空穴的浓度和迁移率分别为1.0×1013cm-2和19 cm2·V-1·s-1,而电子浓度和迁移率分别为1.6×1013cm-2和650 cm2·V-1·s-1。2016年,美国HRL实验室基于二次生长技术首次实现了VTH分别为-1.5 V及+0.5 V的凹槽栅增强型pMOS和nMOS器件,并在此基础上实现了GaN CMOS逻辑电路[23],其结构如图5(b)所示。该器件采用原位生长的AlN/SiN(10 nm/10 nm)作为n和p沟道器件的栅介质层。n和p沟道器件的沟道迁移率分别为300 cm2·V-1·s-1和20 cm2·V-1·s-1。CMOS反相器动态测试结果表明,器件电压转换过程中下降和抬升时间分别为90 ns和670 ns。该器件结构最接近传统的CMOS器件,但二次外延生长对表面处理的要求很高且会增加成本。2020年,美国麻省理工学院和香港科技大学相继基于p-GaN帽层的AlGaN/GaN结构实现了凹槽栅增强型pMOS器件[24],其结构如图5(c)所示,并在2021年进一步实现了n沟道和p沟道增强型器件的类CMOS互补型逻辑电路[25]。中国大陆高校及研究院所在该方面的研究较少,西安电子科技大学在2021年基于p-GaN帽层的AlGaN/GaN结构开展了相关工作[26]。从外延结构看,p-GaN帽层AlGaN/GaN异质结结构是同时制备n和p沟道增强型器件的最佳平台。然而,现有n和p沟道增强型器件的VTH相对较低且输出电流能力匹配程度较低。

图5 GaN基互补型逻辑电路的实现方案[3]

5 基于p-GaN/AlGaN/GaN的互补型逻辑电路面临的挑战

5.1 n沟道增强型器件高阈值电压及稳定性的挑战

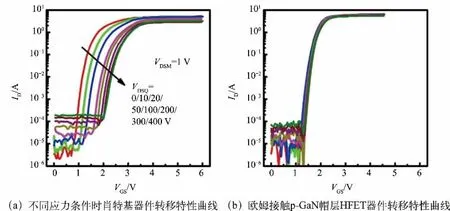

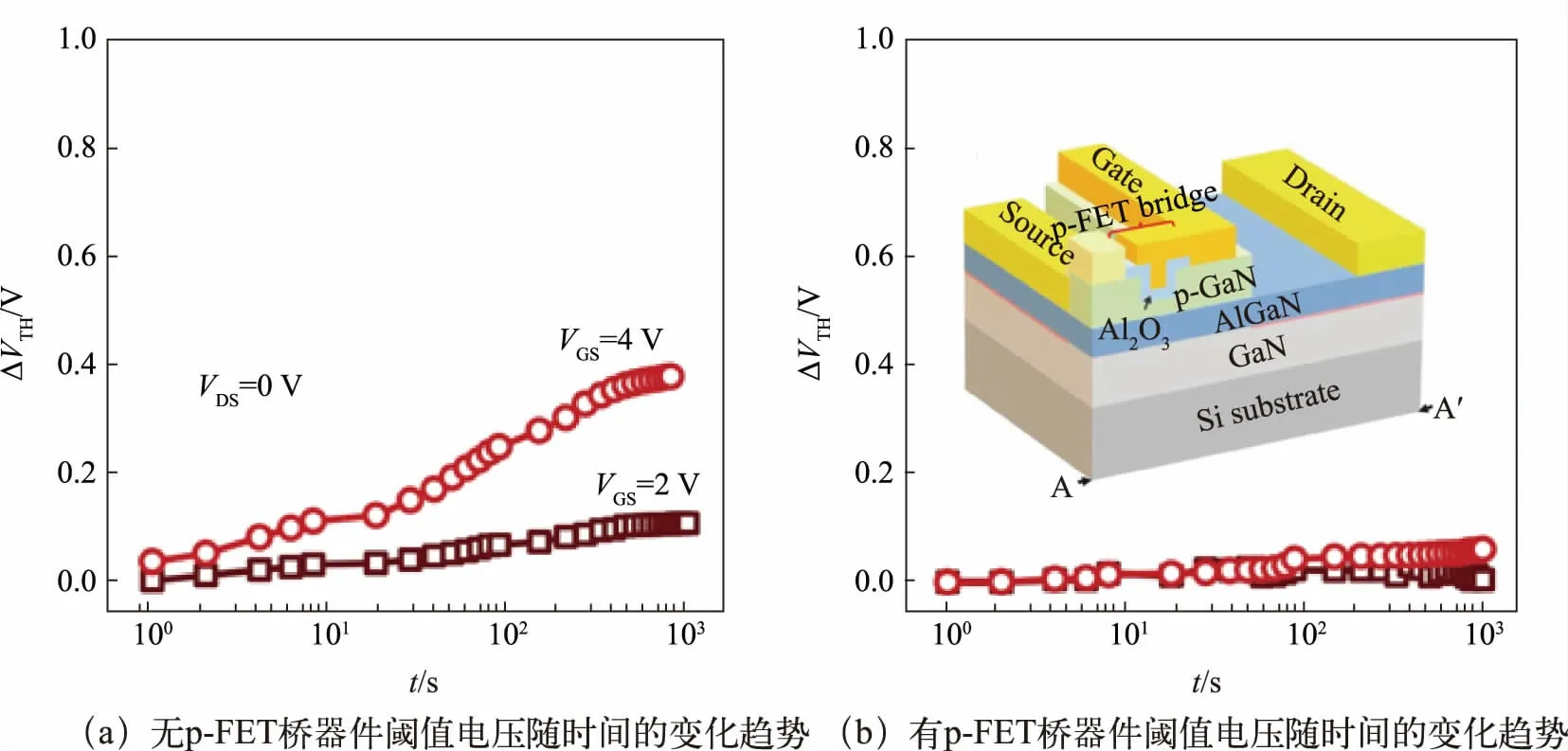

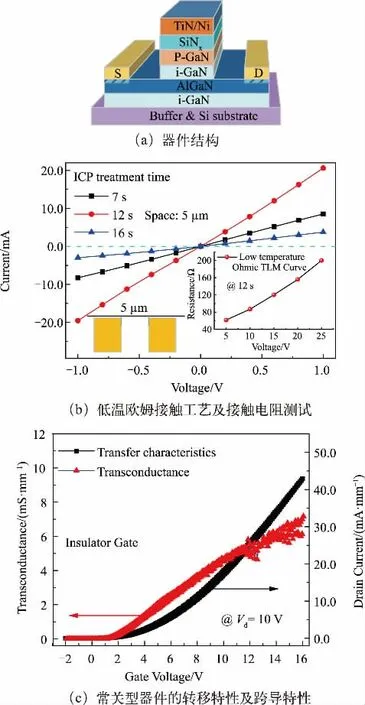

采用p-GaN帽层耗尽2DEG沟道实现n沟道增强型器件已经得到了较多的研究,但器件的VTH通常低于+2 V,而且所允许的栅电压摆幅较低(0~8 V)。因此,同时获得高VTH、低栅极漏电及优良稳定性的栅极结构是n型沟道器件面临的重要挑战[27]。为了提升VTH、减少栅极泄漏电流及增大栅压摆幅,可以将栅极金属和p-GaN之间形成肖特基接触或者在p-GaN上方生长薄层n-GaN以形成pn结[28]。但是,这两种方案在正向栅极偏置时会在p-GaN中形成耗尽区,导致p-GaN层夹在栅极和沟道层之间,与任何端子没有直接的电连接而处于浮空状态[29]。由于缺乏与任何电极的自由载流子交换,p-GaN层在栅极偏压及开关操作期间产生的感应电荷缺少放电通道而导致VTH偏移,如图6(a)所示。通过将p-GaN与栅极金属实现欧姆型接触可以实现非常稳定的VTH[30],如图6(b)所示。然而,相对较小的VTH及较大的开态栅极泄露电流使栅极驱动电路的设计更为复杂。2021年,南方科技大学在传统的肖特基型p-GaN器件的栅极和源极之间连接一个耗尽型工作的p-FET桥结构,通过p-FET的凹槽深度调整VTH并将p-GaN层与源极连接而实现稳定的VTH,p-FET桥结构对器件阈值电压稳定性的影响如图7所示[31]。因此,获得高稳定性、高性能n沟道增强型器件的重要发展思路是设计新型器件结构并在保证高阈值电压的同时提供电学连接通道。2010年,日本赤崎勇和天野浩团队提出通过引入MOS栅极结构可以实现p-GaN帽层n沟道增强型器件的阈值电压调控。PU等人前期基于低温欧姆接触方案实现了栅极自对准的MOS p-GaN栅极结构,有效降低了栅极漏电、提升了VTH[32],先栅工艺MOS p-GaN HFET器件及其电学性能如图8所示。然而介质层的引入会导致栅极对沟道的调制能力下降,一种潜在方案是在利用介质层形成p沟道增强型器件的同时将其延伸至n沟道器件形成局部MOS结构,如图5(d)所示,利用MOS结构部分提升器件VTH、抑制栅极漏电,同时欧姆接触部分可以实现良好的沟道控制能力和p-GaN层的电学连接。

图6 不同电极接触类型的n沟道增强型器件稳定性[30]

图7 p-FET桥结构对器件阈值电压稳定性的影响[31]

图8 先栅工艺MOS p-GaN HFET器件及其电学性能

5.2 与n沟道器件集成匹配的高性能p沟道增强型器件制备技术

p沟道增强型器件面临的主要挑战是其输出电流密度约为n沟道增强型器件的1/100,导致在GaN基CMOS制备中面临较严重的性能不匹配问题。一方面,现有的2DHG的迁移率仍远低于理论预测值;另一方面,与p-GaN线性良好、接触电阻低的欧姆接触仍然难以实现。

利用异质结构极化效应形成高浓度2DHG的报道已经有不少,且获得了p沟道增强型器件。一方面,通常选取两种晶体结构、能带结构及组分差异较大的材料形成异质结以提升空穴浓度,但是生长界面的缺陷、合金散射及材料自身的体缺陷等均会降低空穴的沟道迁移率;另一方面,需要对上层p-GaN进行凹槽刻蚀,降低栅极与沟道的距离以实现高阈值电压。然而刻蚀损伤(氮空位、表面粗糙化等)及MOS结构界面态同样会对沟道中的空穴产生散射作用。在降低刻蚀损伤对沟道迁移率的影响方面,美国麻省理工学院在p-GaN帽层和AlGaN/GaN之间插入一层本征的GaN,分离了2DHG沟道和MOS界面。香港科技大学结合氧等离子处理耗尽凹槽底部p-GaN表面的空穴,提升了器件阈值电压并降低了刻蚀对沟道的散射作用。然而GaN基p沟道增强型器件的沟道迁移率远低于理论值,因此需要深入探究2DHG的输运机制及凹槽栅MOS界面处的材料性质对沟道性能的影响机理。同时,现有报道中实现CMOS逻辑的外延结构与获得高空穴迁移率的外延结构相对独立,如何实现两种外延结构的有效兼容是提升p沟道器件迁移率的另一个重要课题。图5(d)中示出的一种潜在方案为在p-GaN与AlGaN之间引入i-GaN/AlN复合插入层,AlN和GaN之间相对明显的压电极化和能带差异提升了2DHG浓度及沟道的空间局限性,同时AlN和GaN导带之间相对较大的能带带阶能有效提升沟道迁移率。该插入层同样有益于n沟道增强型器件的制备和性能提升,一方面可以有效抑制p-GaN高温生长过程中Mg向AlGaN/GaN界面的扩散,提升2DEG浓度及沟道迁移率;另一方面,AlN层也可以结合F基刻蚀气体成为接入区p-GaN刻蚀工艺的自停止层,有利于实现低损伤、高精度的p-GaN刻蚀。

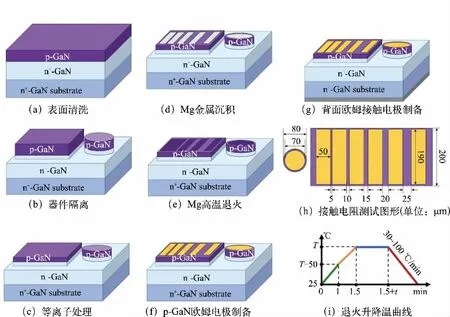

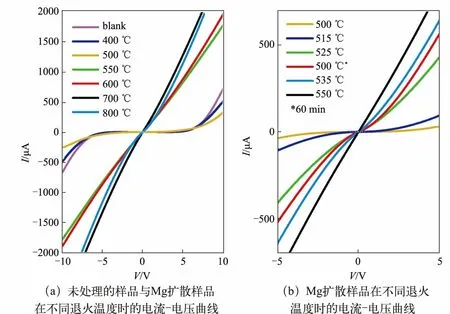

在改善p-GaN欧姆接触方面,已经有许多方法来恢复蚀刻引起的表面损伤,包括湿法蚀刻、热退火及等离子体与湿法蚀刻相结合等。实验结果表明,单独的湿法蚀刻通常无法完全去除刻蚀引起的表面损伤,需要高温热退火工艺进行辅助。2019年,苏州纳米技术与纳米仿生研究所孙钱团队结合四甲基氢氧化铵湿法刻蚀与原位热处理实现了良好的欧姆接触[33]。2022年,WANG等人通过在p-GaN表面低温度(550℃)、短时间(10 min)预扩散金属Mg,与热氧化的Ni/Au电极形成了良好的欧姆接触[34],其工艺流程及特性曲线分别如图9、10所示。同时,实验结果表明该方案同样适用于存在等离子体蚀刻损伤层的p-GaN表面。然而,目前p-GaN的欧姆电极仍然主要是通过热氧化Ni/Au形成的,Au与传统的硅基CMOS工艺并不兼容。前期文献报道中利用重掺杂形成简并n-GaN层可以增大禁带宽度并与AlGaN层形成良好的欧姆接触。德岛大学通过优化磁控溅射条件实现了空穴浓度在1016~1020cm-3可调的NiO材料[35],进而发现NiO与p型硼掺杂金刚石(禁带宽度约为5.5 eV)界面较低的价带带阶有助于实现良好的欧姆接触[36]。该工作被北京邮电大学借鉴用于制备InP/InGaAs光电探测器中p型层的欧姆接触[37]。以上工作表明,选择一种与p-GaN价带能级匹配的简并p型氧化物作为金属与p-GaN界面的过渡层有利于实现良好的欧姆接触。

图9 基于Mg扩散提高p-GaN欧姆接触性能的工艺流程[34]

图10 后退火条件对欧姆接触特性的影响[34]

6 结束语

文章对当前GaN功率互补型逻辑电路发展趋势及面临的技术难题进行了讨论与总结,由分析可知,p-GaN帽层AlGaN/GaN异质结结构是实现互补型逻辑电路的最佳平台。目前,在n型沟道增强晶体管的综合性能提升方面仍然面临诸多关键难题,而在p沟道增强晶体管器件方面无论是对其物理机制还是电学性能提升的研究都处于起步阶段,因此需要以业界需求为导向,从材料参数、器件结构设计及工作机理解释等方面分别对n型沟道和p型沟道GaN增强型器件开展系统研究,为GaN基互补型逻辑电路性能提升提供理论依据,为高性能GaN功率集成电路的设计及稳定性分析提供原理支撑。