碲化铋基热电薄膜与器件研究进展

胡少雄,周 曼,任超杰,张博涵,祝 薇,,赵未昀,邓 元,

(1.北京航空航天大学材料科学与工程学院,北京 100191) (2.北京航空航天大学杭州创新研究院 浙江省智能传感材料与芯片集成技术重点实验室,浙江 杭州 310051)(3.北京航空航天大学 前沿科学技术创新研究院,北京 100191)

1 前 言

在物联网、大数据、可穿戴设备等领域蓬勃发展的今天,尽管各类电子元器件的功耗在不断降低,但由于其数量庞大且仍处于爆发式增长阶段,因而需要消耗大量的人力成本通过更换电池的方式为这些低功耗电子元器件进行供能。与此同时,微电子技术的快速发展使得各类电子元器件的性能和集成度在不断提高,发热量也在不断增大,因此小空间的快速散热问题成为制约其发展的关键瓶颈。热电器件是一种以热电材料为核心的能源转换器件,它既可以基于塞贝克(Seebeck)效应将器件两端的温差转换为电能用于发电,又可以基于帕尔贴(Peltier)效应通过外加电场将器件一端的热能转移至另一端从而实现快速制冷与控温。热电器件具有体积小、全固态、寿命长、免维护、无污染等优点,被认为是物联网传感节点、可穿戴设备实现自供电的解决方案之一,同时也是小空间快速制冷的有效方式,受到了国内外研究人员的广泛关注。

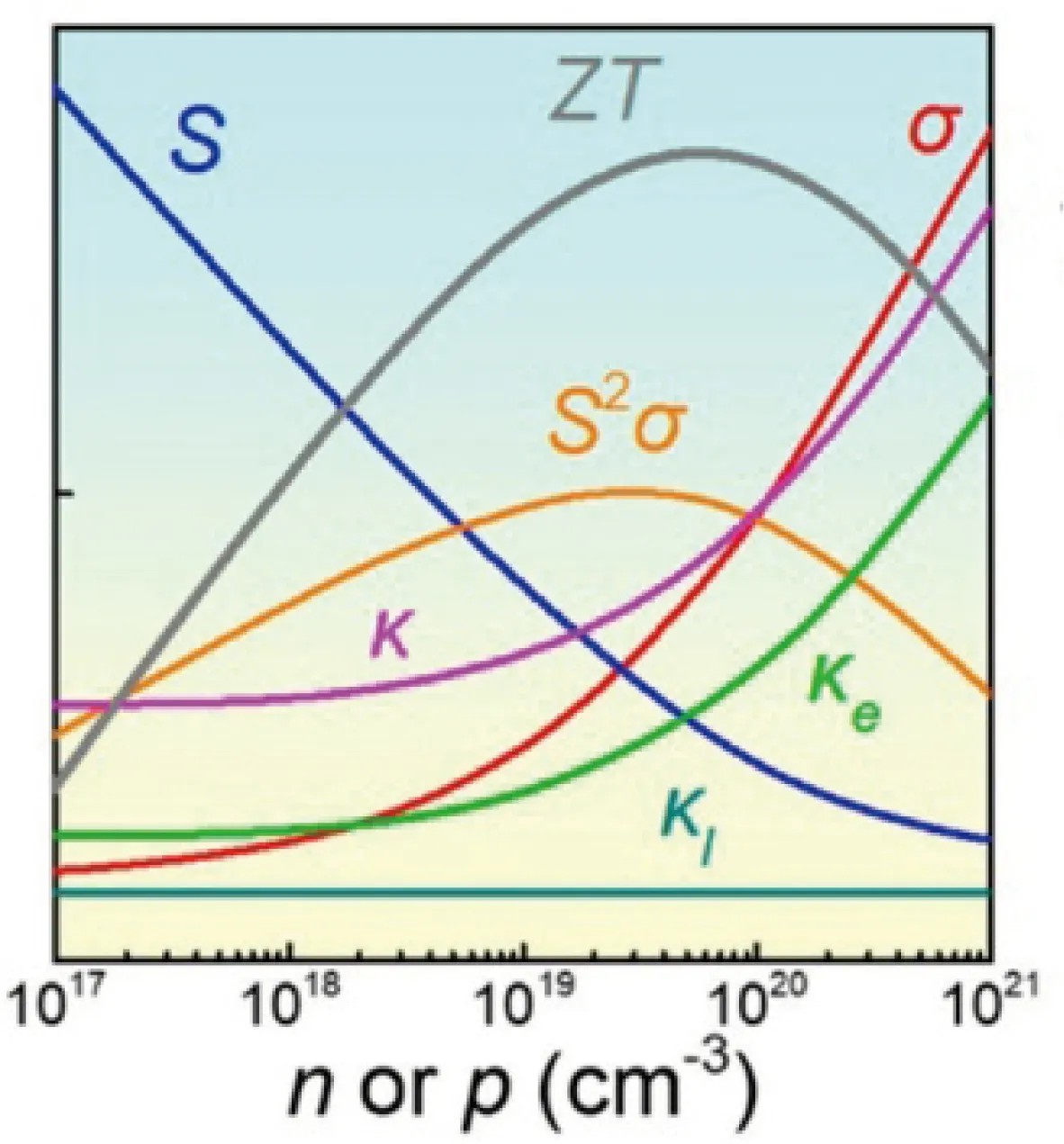

热电材料的性能可以用一个无量纲的物理量——热电优值(zT值)来评价,zT值可用式zT=S2σT/κ表示,其中S为材料的Seebeck系数,σ为电导率,κ为热导率,T为绝对温度。从zT值的表达式可以看出,要想提高材料的热电性能,可以分别通过提高材料的Seebeck系数和电导率,或降低热导率来实现,但上述3个物理量相互耦合,如图1所示,无法独立调控[1]。因此,尽管早在19世纪初,德国科学家Seebeck、法国科学家Peltier和英国科学家Thomson就先后发现了以他们名字命名的3大热电物理效应,且在至今200多年的热电发展历程中也先后涌现出Bi2Te3[2]、PbTe[3]、方钴矿[4]、half-Heusler合金[5]等优秀的热电材料体系和有效的热电性能优化策略[6-8],但在当前室温条件下商用热电材料的zT值普遍仍在1.0左右,较低的转换效率使得热电技术的应用场景十分受限。根据计算,要想使热电器件的转换效率接近传统发电机,热电材料的zT值需达到3.0以上,才有望在实际场景中进行大规模应用。

图1 电导率σ、Seebeck系数S、功率因子S2σ、热导率κ、电子热导率κe、晶格热导率κl和热电优值zT等参数之间的关系[1]Fig.1 The relationship between electrical conductivity σ, Seebeck coefficient S, power factor S2σ, thermal conductivity κ, electron thermal conductivity κe, lattice thermal conductivity κl and thermoelectric figure of merit zT[1]

1993年,Hicks和Dresselhaus[9, 10]通过计算发现将材料进行低维化,特别是制备成量子井超晶格结构,可大幅提高热电材料的zT值。随后,Venkatasubramanian等[11]制备的纳米结构Bi2Te3/Sb2Te3超晶格薄膜在300 K时zT值达到了2.4,这有力证明了热电材料薄膜化是一种有效提升热电材料性能的方法。一方面,相比于传统块体热电材料,热电薄膜材料的纳米结构含有更多的晶界,这些界面缺陷能够选择性地散射波长与之相当的声子,因此可有效降低材料的晶格热导率,提高材料的热电性能。另一方面,热电材料薄膜化能够产生量子限制效应,使得电子在被压缩维度的运动受到限制[12],在费米能级附近,与Seebeck系数呈正相关的电子态密度会增大,使得热电薄膜材料的Seebeck系数相比块体材料显著增大。此外,基于热电薄膜材料制备的微型热电器件具有体积小、制冷密度高等优势,可以实现高密度阵列集成,因此十分契合物联网、可穿戴设备、微电子芯片领域对微能源供应和小空间快速制冷的迫切需求,也更符合未来电子信息领域高性能、微型化、低功耗的发展趋势。

Bi2Te3基热电材料是当前室温条件下性能最好的热电材料,也是目前商业化应用最成功的热电材料。本文以Bi2Te3基热电薄膜材料与器件为核心,对热电薄膜的制备方法与性能优化,热电薄膜器件的设计制备与界面优化以及热电薄膜器件在微发电和快速制冷领域的应用等几个方面进行了介绍。

2 Bi2Te3基热电薄膜的制备及性能优化

常用的Bi2Te3基热电薄膜材料制备方法主要可以分为物理气相沉积(physical vapor deposition,PVD)和化学气相沉积(chemical vapor deposition,CVD)两类。其中,PVD是指在高真空条件下,通过物理方法使固态的原材料转变为气态后沉积在基底上成膜,最常用的PVD制备方法主要有磁控溅射(magnetron sputtering,MS)法、真空蒸发(vacuum evaporation,VE)法、分子束外延(molecular beam epitaxy,MBE)法、脉冲激光沉积(pulsed laser deposition,PLD)法等。CVD则是指利用含有成膜元素的气态或蒸汽态物质,在衬底表面通过化学反应生成薄膜的制备方法,常用的有常压化学气相沉积(atmospheric pressure chemical vapor deposition,APCVD)、低压化学气相沉积(low pressure chemical vapor deposition,LPCVD)等。本节将主要对上述制备方法的成膜原理、代表性研究成果以及不同制备方法的优缺点进行介绍。

2.1 磁控溅射法

MS是指电子在电场的作用下,与腔体中的气氛原子发生碰撞,使气氛原子电离后加速撞击靶材发生溅射,并最终在基底表面沉积成膜。MS适用于金属、金属氧化物、半导体等绝大多数材料体系,是目前最常用的薄膜制备手段之一。

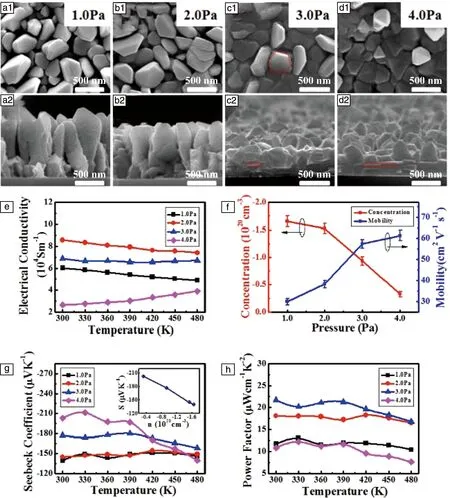

在MS制备热电薄膜的过程中,溅射功率、溅射气压和基底温度等参数会直接影响薄膜的微观结构,进而影响薄膜材料的热电性能,因此通常会通过调控溅射参数来优化薄膜的热电性能。例如,Kong等[13]使用MS在聚酰亚胺衬底上制备Bi2Te3热电薄膜,在其它参数保持不变的情况下,通过调控溅射气压,薄膜从(015)取向的柱状生长逐渐转变为(001)取向的层状生长,同时材料的晶粒减小,晶界随之增多,材料的热电性能得到大幅提升,最终制备出的层状Bi2Te3薄膜室温条件下最高功率因子可达21.7 μW·cm-1·K-2,如图2所示。Tan等[14]采用MS工艺在SiO2衬底上制备了纳米柱状的Bi0.5Sb1.5Te3热电薄膜,并系统地研究了沉积温度对薄膜微观结构及热电性能的影响。研究发现,随着沉积温度的升高,薄膜在生长过程中会产生明显的织构效应,从而显著提高载流子迁移率和电导率,此外合适的沉积温度可以诱导Bi/Sb和Te之间的反位掺杂,释放更多的自由电子,并中和空穴载流子,引起载流子浓度降低,使载流子浓度更接近最优值,2种因素的共同作用使得热电材料的性能大幅提高,最终制备出的Bi0.5Sb1.5Te3薄膜在室温条件下功率因子高达45.3 μW·cm-1·K-2。除了通过调控微观形貌来优化薄膜热电性能外,通过多靶共溅射的方式调控成分也是MS优化薄膜热电性能的常用方式。例如,Shang等[15]采用MS工艺系统研究了Te含量和沉积温度对薄膜微观结构和热电性能的影响。随着沉积温度的升高,Bi2Te3薄膜的结晶度提高,晶粒尺寸增大,但较高的沉积温度会使Te元素蒸发,造成Bi2Te3组成偏差,使晶体结构存在缺陷和错位。通过双靶共溅射的方式补充Te含量会对晶粒生长取向有较大影响,使薄膜从不规则的六边形晶粒转变为片层状晶粒,同时影响其载流子浓度和迁移率。最终,在相同的沉积温度下通过共溅射补充Te含量制备出的Bi2Te3薄膜的Seebeck系数和功率因子均高于仅通过单靶溅射制备的Bi2Te3薄膜。由于MS制备热电薄膜时沉积温度一般较低,会导致薄膜缺陷多、结晶性差,影响材料的热电性能,因此通常需要通过退火等手段进行优化。例如,Cao等[16]针对n型Bi2Te3薄膜材料随温度变化稳定性差的问题,采用MS通过调控沉积温度和沉积气压,制备出不同择优取向的Bi2Se0.5Te2.5薄膜。进一步经过退火处理后,薄膜变得更加致密,结晶性更好,从而在更大的使用温度范围内具有更好的稳定性。

图2 采用磁控溅射法在不同溅射气压下制备的Bi2Te3薄膜微观结构与热电性能[13]:(a~d)Bi2Te3薄膜表面与截面SEM照片,(e~h)Bi2Te3薄膜热电性能Fig.2 Microstructure and thermoelectric properties of Bi2Te3 thin films deposited at diverse pressures by magnetion sputtering method[13]: (a~d) surface and cross-sectional SEM images of Bi2Te3 thin films, (e~h) thermoelectric properties of Bi2Te3 thin films

采用MS制备Bi2Te3基热电薄膜具有沉积温度低、薄膜生长均匀且微观结构和成分可控性强等优点,但由于制备过程中晶体生长受热力学和动力学等因素的影响和限制,通常会导致较多的晶体缺陷,因此需结合后续的优化工艺来提高薄膜的综合性能。

2.2 真空蒸发法

VE是在高真空环境下通过加热蒸发源,使该蒸发源汽化或升华,最终在基底表面凝聚形核生长成固相薄膜的简便PVD方法,主要用于熔点低于1500 ℃的金属、半导体等材料的蒸镀成膜。

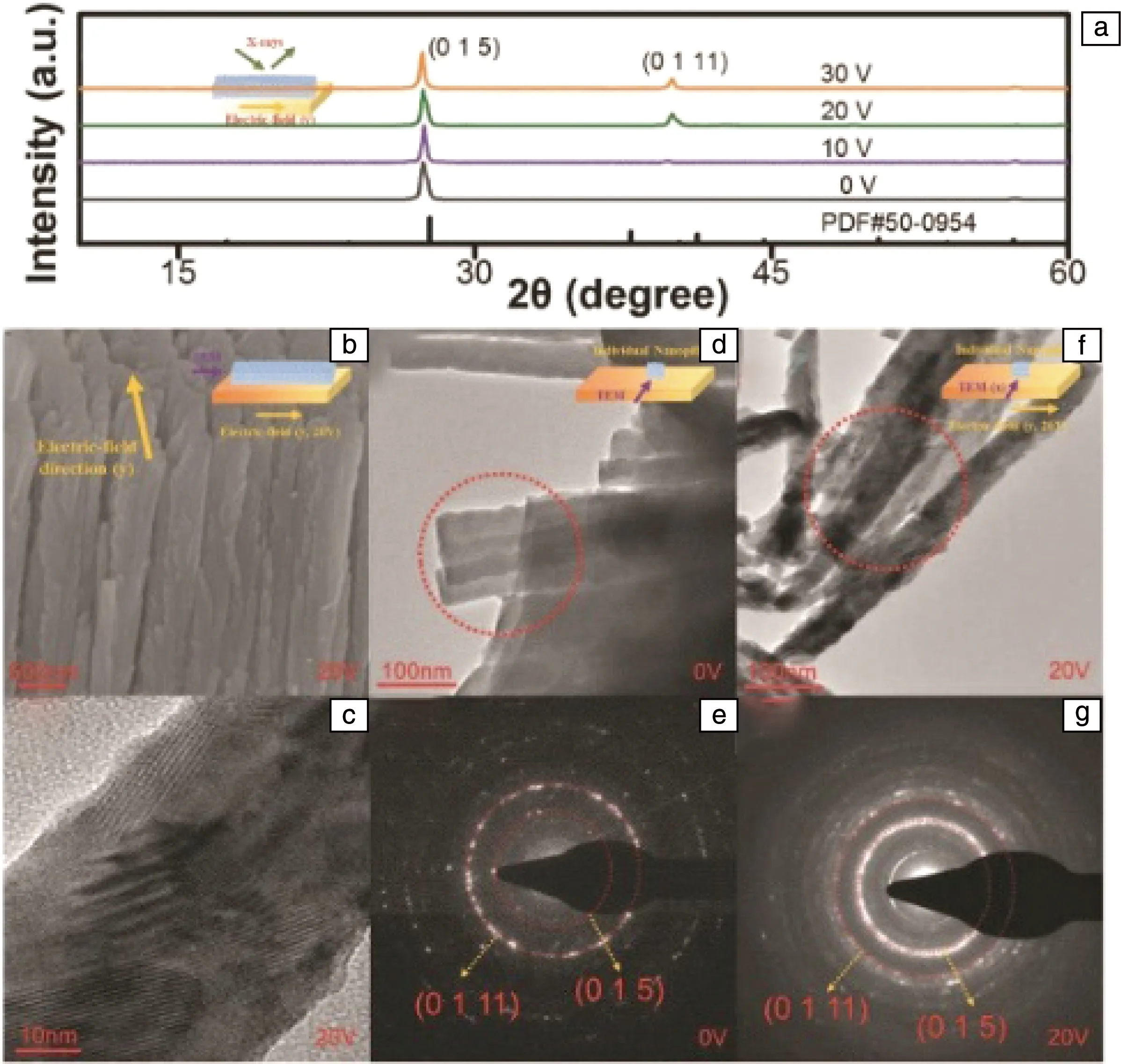

真空蒸发过程中的过饱和度决定了材料的纳米结构形貌,可通过调节沉积速率来实现。2009年,Deng等[17]首次报道了一种使用VE且无需模板即可制备出有序Bi2Te3纳米线的工艺,研究发现,过饱和度在控制纳米结构的形貌方面起着重要的作用,彼此平行、均匀分布的纳米线阵列具有良好的载流子输运性能,制备出的薄膜Seebeck系数可达到-150 μV·K-1。2018年,Tan等[18]使用真空热蒸发法通过调控衬底倾斜角度,制备了一种45°倾斜且排列紧密的(Sb,Bi)2Te3纳米线阵列。这种特殊的微观结构在强烈散射声子的同时,还可以为载流子输运提供良好的通道,使得薄膜的zT值在室温下高达1.72,且在200 ℃条件下,Seebeck系数达到255 μV·K-1。为实现热电薄膜的电声解耦,Tan等[19]采用外加电场辅助真空热蒸发沉积技术,在玻璃表面生长了具有纳米线阵列的Bi2Te2.7Se0.3薄膜。研究发现,随着外加电场的增加,薄膜生长取向逐渐由(015)方向转变为(015)和(0111)方向,如图3所示。通过调控外加电场可以精确控制薄膜的各向异性,形成晶界角,引入能量过滤效应,进而产生独特的热电性能各向异性,提高材料的zT值,最终在室温下薄膜的zT值高达1.6。随后,Tan等[20]在热蒸发沉积薄膜后对薄膜进行退火处理,成功制备了晶态和非晶态复合的纳米柱状Bi0.5Sb1.5Te3薄膜,在室温下该薄膜zT值达到1.5。与退火处理前相比,薄膜性能的改善归因于非晶态的局部无序结构可增强声子散射,有效降低晶格热导率,同时高结晶度区域可削弱载流子散射效应,显著提高薄膜的电导率,这种晶态和非晶态复合的结构为改善热电材料性能提供了新的策略。

VE具有工艺简单、薄膜沉积速率可控以及外源污染较低等特点,是实现大面积薄膜沉积最具潜力的方法,有望制备出热电性能优异的薄膜材料。但此方法生长的薄膜与基底之间的结合力较差,易造成膜层脱落,因此不适宜多层膜的制备。

2.3 分子束外延法

MBE是在超高真空环境下通过加热使靶材蒸发,蒸发出的具有一定热能的原子或分子束流直接喷射到基底上,从而结晶生长出薄膜或超晶格结构的方法。MBE是制备单原子层尺度薄膜最适宜的方法,主要用来制备GaAs、InP、GaN等半导体异质结,也有科研人员用这种方法制备Bi2Te3等热电材料薄膜。

图3 外加电场辅助热蒸发沉积技术制备的Bi2Te2.7Se0.3薄膜性能表征[19]:(a)XRD图谱,(b,c)20 V外加电场下沉积的薄膜截面SEM照片和HRTEM照片,(d,e)无电场辅助沉积的薄膜TEM照片和SAED图案,(f,g)20 V外加电场下沉积的薄膜TEM照片和SAED图案Fig.3 Characterization of Bi2Te2.7Se0.3 thin films prepared by external field-assisted thermal evaporation-deposition technique[19]: (a) XRD patterns, (b, c) side-view SEM and HRTEM images of the film deposited under 20 V electric field, (d, e) TEM image and the corresponding SAED pattern of the nanopillars deposited under no electric field, (f, g) TEM image and the corresponding SAED pattern of the nanopillars arrays deposited under 20 V electric field

相比于其他薄膜制备方法,采用MBE法可以实现对原子层厚度的精确控制,同时具有薄膜组分精确可调、沉积温度低、薄膜质量好的优点,但由于这种方法制备薄膜时生长速度慢,且使用成本极其昂贵,因此在制备Bi2Te3热电薄膜时使用相对较少。

2.4 脉冲激光沉积法

PLD是利用高能量密度脉冲辐射冲击靶材,激光与材料之间发生相互作用,靶表面发生蒸发电离,产生含有靶原子或离子的等离子体,最终等离子体在电场作用下沉积于基底表面成膜,目前常用于ZnS、MgO、MoS2及Bi-Sb-Te合金等材料的制备。

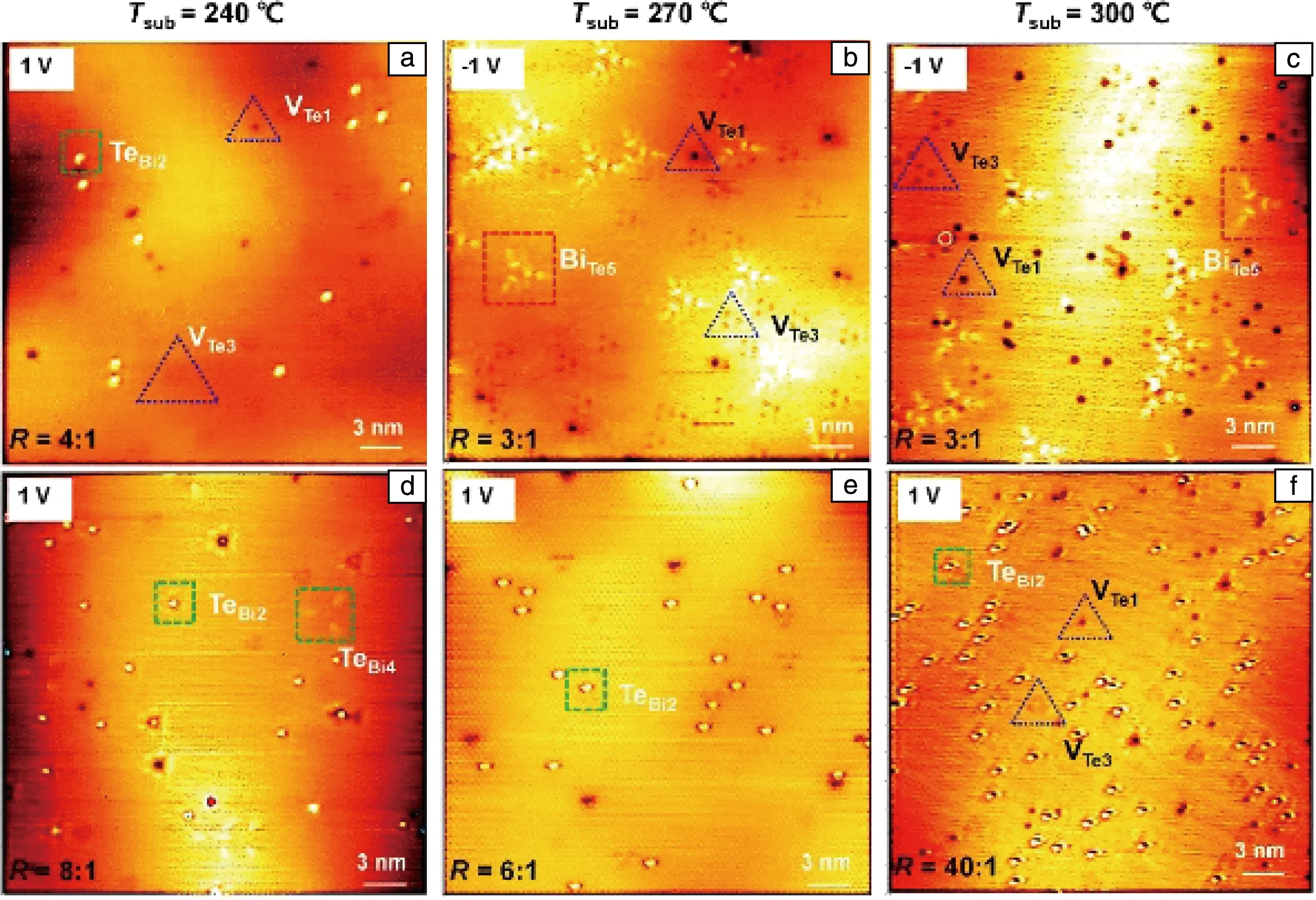

图4 采用分子束外延法在不同衬底温度和Te/Bi通量比条件下制备的Bi2Te3薄膜扫描隧道显微镜照片(30 nm×30 nm)[25]:(a,d)衬底温度240 ℃,Te/Bi通量比4∶1(上)和8∶1(下);(b,e)衬底温度270 ℃,Te/Bi通量比3∶1(上)和 6∶1(下);(c,f)衬底温度300 ℃,Te/Bi通量比3∶1(上)和 40∶1(下)Fig.4 STM images (30 nm×30 nm) of Bi2Te3 films grown at different substrate temperatures (Tsub) and Te/Bi flux ratios (R) by molecular beam epitaxy[25]: (a,d) Tsub=240 ℃, with R=4∶1 (top) and 8∶1 (bottom); (b,e) Tsub=270 ℃, with R=3∶1 (top) and 6∶1 (bottom); (c,f) Tsub=300 ℃, with R=3∶1 (top) and 40∶1 (bottom)

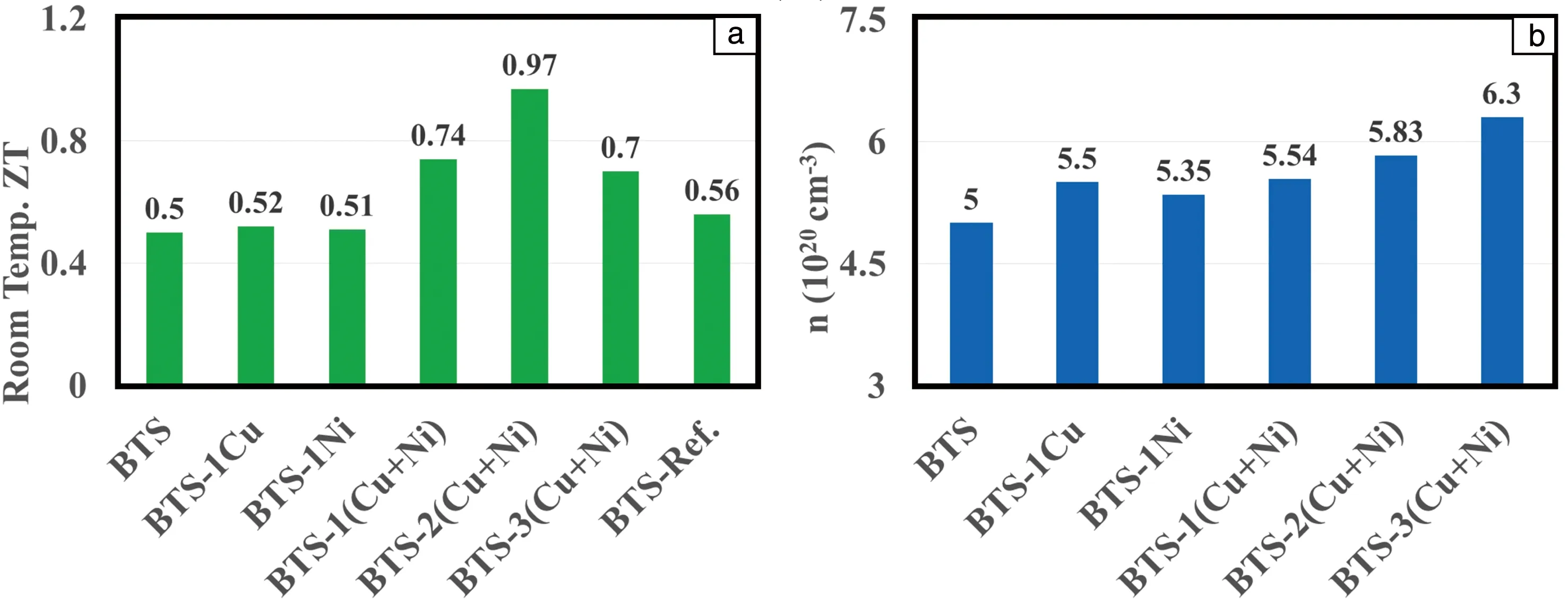

图5 脉冲激光沉积法制备的Cu/Ni/Bi2Te2.7Se0.3纳米复合薄膜性能表征[30]:(a)室温下纳米复合薄膜的热电优值,(b)纳米复合薄膜的载流子浓度Fig.5 Characterization of Cu/Ni/Bi2Te2.7Se0.3 nanocomposite films prepared by pulsed laser deposition method[30]: (a) room-temperature thermoelectric figure of merit of the thin film nanocomposites, (b) charge carrier concentration of the nanocomposite films

PLD具有沉积速率快、生长温度低、组分可控以及工艺设计性强等优势,能够实现超薄薄膜生长和多层膜沉积,是制备薄膜材料的常用方式。但PLD在制备薄膜过程中,激光与材料相互作用出现的相爆炸等效应会引起表面颗粒飞溅,导致薄膜质量降低。

2.5 化学气相沉积法

CVD方法是近几十年发展起来的薄膜制备方法,主要用于制备氧化物、硫化物、III-V和II-IV族化合物等无机材料体系。

3 热电薄膜器件的制备与应用

近年来,随着物联网、可穿戴设备等领域的快速发展,微电子器件的自供电问题亟需解决,基于热电器件的自供电模块是最有潜力的解决方案之一;此外,随着电子元器件性能越来越强,且集成度越来越高,对小空间的散热能力也提出了新的要求,热电薄膜制冷器件则非常适合于小空间快速制冷。本节将对常见的热电薄膜器件结构设计与制备方法、界面设计与优化以及在发电和制冷等领域的应用进行简要介绍。

3.1 热电薄膜器件结构设计与制备

热电器件一般由n型热电臂、p型热电臂以及将它们连接起来的金属电极组成,器件冷热两端采用绝缘导热的材料进行封装,同时还可以作为基底起到支撑主体结构的作用。常见的热电薄膜器件可以根据热流方向与基底所在平面的关系分为面内型热电器件和面外型热电器件。

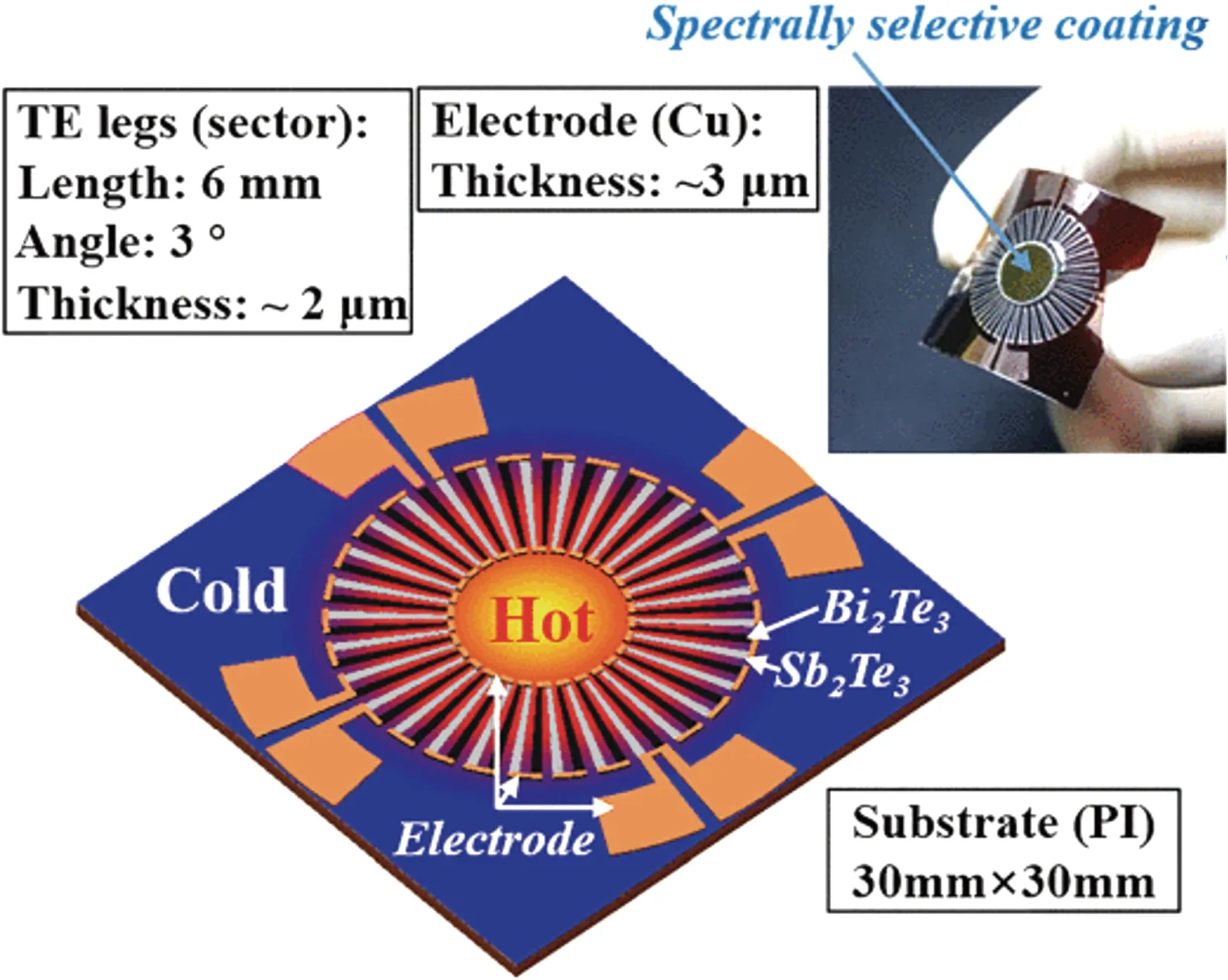

3.1.1 面内型热电器件

面内型热电器件的热流方向与基底所在平面平行,与其他结构的器件相比,面内型器件的制备工艺相对简单。由于热电器件常用的AlN、Al2O3等陶瓷基底热导率较高,不利于在面内型器件热电臂两端建立温差,因此通常将面内型热电器件制备到热导率较低的柔性衬底上。Hou等[33]设计了一种仅由p型Bi0.5Sb1.5Te3/环氧树脂材料与Al/Cu/Ni多层薄膜电极串联而成的面内型热电器件。该器件仅需将简单的印刷工艺与热压固化工艺相结合,即可在聚酰亚胺衬底上实现(0001)择优取向的热电材料图案化阵列的制备,再将该热电材料图案化阵列与热蒸发法制备的图案化电极进行集成即可制备出面内型热电器件。Yuan等[34]设计了一种放射状结构面内型器件,通过丝网印刷工艺依次在聚酰亚胺衬底上印刷p型热电臂、n型热电臂以及电极材料后加热固化即可成型该器件。此外,利用该制备方法简单、快速的优势,还可通过制作平面阵列或是进行空间堆叠来提高该器件的能量转换效率。为了提高热电材料的性能和图案化精度,Guo等[35]利用MS结合光刻剥离工艺在30 mm×30 mm的聚酰亚胺基底上沉积了30对Bi2Te3和Sb2Te3热电臂,构建了径向分布的面内型热电薄膜器件,如图6所示。近年来,无需掩模的3D打印技术也被应用到面内型热电器件的制备中,这种工艺可大大减少器件的制备流程,且易于实现三维结构的构建。例如,Chen等[36]使用喷墨打印技术,将n型Bi2Te3纳米线油墨和p型Bi0.5Sb1.5Te3纳米线油墨直接打印到聚酰亚胺衬底上制备热电臂,随后通过液态金属电极连接后即可制备出面内型柔性热电器件。

图6 磁控溅射结合光刻剥离工艺制备的放射状面内热电薄膜器件[35]Fig.6 In-plane thin-film thermoelectric devices with radial structure fabricated by magnetron sputtering combined with lithography stripping process[35]

面内型热电薄膜器件的热电臂较长,制备相对容易,能够兼容目前已经非常成熟的集成电路制备工艺,且由于器件的热流沿面内传输,所以很容易建立起较大的温差。然而,面内型热电器件是通过薄膜来传输热量,薄膜横截面积小,导致器件的吸热面积小并且在热量传输的过程中很容易流失,因此面内型器件的热利用效率通常较差。此外,为了建立大的温差,这种结构的器件热电臂一般设计的较长,导致器件的内阻较大。以上原因使得面内型薄膜热电器件更适合用作红外传感器[37]、热流传感器[38]或温度传感器[39]等与热有关的物理量探测,而较少用在大功率发电或制冷等领域。

3.1.2 面外型热电器件

面外型热电器件的热流方向与基底所在的平面垂直,呈现出与传统商用块体热电器件类似的“π”型结构。与面内型热电器件相比,面外型热电器件制造难度大,对材料的热电性能以及器件的集成工艺要求也相对较高。对Bi2Te3基面外型热电薄膜器件来说,常见的制备方式主要是将第2节介绍的薄膜制备工艺与掩模法、光刻法、激光刻蚀法等图案化工艺相结合构成的类微机电系统加工工艺。例如,Tan等[40]通过掩模板辅助MS,在AlN基底上分别制备了p型Bi0.5Sb1.5Te3和n型Bi2Se0.3Te2.7热电臂阵列。如图7a所示,在与Cu薄膜电极集成后,最终在30 mm×30 mm范围内构建了具有98对热电臂的面外型薄膜器件,在4 K温差下该器件输出电压可达120.5 mV,输出功率为145.2 μW,此外该器件在160 mA电流下还可产生14.6 K的最大温差。为了提高热电器件的输出功率,热电薄膜器件的阵列密度需进一步提高,传统硅基工艺中使用成熟的光刻法可以实现热电臂的高密度集成。Zhang等[41]将电镀技术与光刻剥离法相结合,在3 mm×3 mm晶圆片上制备出由127对n型Bi2Te3和p型Sb2Te3热电臂组成的面外型热电器件。该器件在52.5 K温差下最大输出功率可达2.99 mW,功率密度达到9.2 mW·cm-2。Mu等[42]采用光刻剥离法在直径为76 mm的单晶硅片上实现46 000对Bi2Te3基薄膜热电臂的集成。

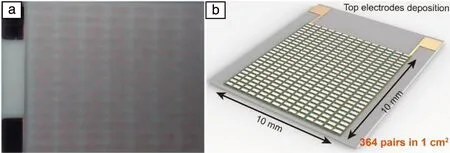

然而,尽管光刻法的加工精度很高,但这种传统的硅基加工工艺不能完全兼容热电微器件的制备。这是因为,一方面硅晶圆片的热导率偏低,相比AlN会大大抑制器件的纵向传热。另一方面,高zT值的热电材料通常需要高温处理辅助结晶,而光刻胶难以承受高温,导致光刻剥离工艺与高性能热电材料制备工艺不兼容。此外,对热电器件来说,热电臂的尺寸精度控制在微米级即可满足使用要求,不需要达到光刻剥离工艺的纳米级精度。因此,近年来热电领域的研究人员发展了基于激光微加工工艺的新型热电薄膜器件制备工艺。例如,Yu等[43]采用飞秒激光直写法,通过对激光能量的精确控制,在10 mm×10 mm的AlN基底上实现了364对热电臂的图案化加工(图7b),制备出的热电器件在33.1 K的温差下有着494 mV的输出电压和0.514 mW的输出功率。Zhou等[44]在此基础之上,使用超快激光直写技术在10 mm×10 mm范围内集成了496对热电臂,填充因子达到了55%。

图7 不同工艺制备的面外型Bi2Te3基热电薄膜器件:(a)掩膜板辅助磁控溅射工艺制备的含有98对热电臂的热电薄膜器件[40];(b)飞秒激光直写工艺制备的含有364对热电臂的热电薄膜器件[43]Fig.7 Out-plane Bi2Te3 thin film thermoelectric devices prepared by different processes: (a) thin film thermoelectric device containing 98 pairs of thermoelectric legs prepared by mask assisted magnetron sputtering[40]; (b) thin film thermoelectric device containing 364 pairs of thermoelectric legs prepared by femtosecond laser direct writing process[43]

面外型热电薄膜器件具有结构简单、热端面积大、热量利用率高等特点,因此具有较大的输出功率以及较高的转换效率。然而,对于薄膜器件来说,这种结构很难建立较大的温差,因此发电功率通常较低。且较低的内阻和微小的体积使该薄膜热电器件在小空间快速制冷和微小能源供应方面具有明显的优势。

3.2 热电薄膜器件界面设计与优化

影响热电薄膜器件性能的主要因素除了热电材料本身的性能以及器件的结构设计外,器件各层界面的优化设计同样至关重要。随着热电器件的薄膜化,金属-半导体界面电输运性能对器件输出性能的影响将显著增加,甚至有可能导致热电器件失效。理论模拟计算表明,当界面的比接触电阻率达到10-5Ω·cm2量级时,可以获得良好的电接触;而当比接触电阻率达到10-7Ω·cm2量级时,可以完全忽略界面接触电阻对器件输出性能的影响[45]。目前,热电薄膜器件中的界面比接触电阻率普遍只能调节到10-5~10-6Ω·cm2量级[46-48],要想进一步减小接触电阻对器件性能的影响,则需继续深入探索改善接触界面电性能的方法及背后的影响机理。此外,对于无需维护即可长期可靠运行的热电器件来说,其高温端的电极与热电材料之间的界面经常由于元素扩散[49]或者发生化学反应[50]而产生界面组分和结构的变化,使得器件界面电阻和热阻增加,造成器件发电或者制冷性能衰减。因此,从提高器件金属-半导体界面的电传输性能和可靠性两方面考虑,如何调节界面载流子运输、保证界面元素和结构稳定性是目前亟需解决的问题。

调控金属及半导体制备工艺、引入中间过渡层以及优化热电半导体表面结构是降低界面接触电阻,提高器件可靠性的常用手段。例如,Bulman等[31]发现在半导体上电镀致密的金属,比直接蒸发制备疏松的金属更容易获得低接触电阻界面;Kong等[51]通过控制本征热电半导体的定向生长,调节界面连接和晶格错配度,实现了有效导电接触区域的增大和表面耗尽区域宽度的减小,使得比接触电阻率可低至10-7Ω·cm2量级;Gupta等[52]对Bi2Te3与Ni和Co接触界面进行等离子清洁和后退火处理,通过调节界面键合,使界面比接触电阻率小于10-7Ω·cm2。引入金属作为中间过渡层,一方面可以从功函数匹配、晶格匹配、界面掺杂等方面调控界面电性能,另一方面还能通过热膨胀系数匹配、改善粘附性等角度控制应力,从而保证界面可靠性。例如,Qin等[47]通过引入Ti过渡层并调控其厚度,可有效控制Bi2Te3/Ti/Cu界面的元素扩散,实现接触电阻的降低和界面稳定性的提升。此外,引入分子纳米层等高导电有机物也是降低界面接触电阻的新手段。Cardinal等[53, 54]通过在Cu/Bi2Te3界面引入单层1,8-辛二醇,抑制金属碲化物的形成和氧化,使界面比接触电阻率提高了13倍;随后,他们在Cu/Bi2Te3和Ni-Bi2Te3界面插入单层3-巯基丙基三甲氧基硅烷,更有效地抑制了Cu扩散,促进了Bi/Te表面氧化物在Ni-Bi2Te3界面上的化学还原,使其比接触电导率提高了17倍。但分子纳米层在冷热交替的极端工作环境下的界面稳定性还有待进一步考量。从上述研究可以看出,半导体材料的表面态以及金属和半导体接触的界面态调控,对界面的电性能有决定性的影响。

半导体表面改性的手段主要有等离子清洗、离子注入2种。等离子清洗可以去除半导体表面的氧化物杂质,增加薄膜粗糙度,增强界面的结合力,提升界面电传输性能。例如,He等[55]通过Ar+预溅射(Bi,Sb)2Te3超晶格表面,使该表面与Cr涂层之间的界面粗糙度增加,通过控制界面形态调控接触电阻,且去除界面处的氧,增加直接接触面积,进一步降低了接触电阻,使比接触电阻率由10-6Ω·cm2(p型接触)和10-7Ω·cm2(n型接触)均降低至10-8Ω·cm2。Zhu等[46]采用Ar/H2等离子体清洗增强了Bi2Te3/Cu界面结合力,使得界面临界负载从44.25提高到52.05 mN。此外,通过离子注入对半导体表面进行重掺杂也是目前对半导体表面改性的重要方向。离子注入可以大幅提高半导体表面的载流子浓度,降低场致热电子发射机制主导的接触电阻,增强基于载流子隧穿效应的场发射机制,显著降低金属和半导体之间的接触电阻。例如,Taylor等[56]将碘供体和银受体分别注入n型和p型(Bi,Sb)2(Se,Te)3表面,实现表面10倍高的掺杂,使得界面比接触电阻率可降低至10-7Ω·cm2。Vikhor等[50]建立了在Bi2Te3基热电臂与金属接触界面中元素扩散与界面电阻关系的物理模型,理论验证了表面离子注入降低界面接触电阻的可行性。但是,离子注入和等离子清洗都是采用高能粒子轰击半导体表面,特别是离子注入工艺,高能杂质离子注入到半导体晶体内,会与晶格碰撞,不可避免地造成晶格损伤,导致半导体表面和内部产生大量缺陷。因此,虽然这2种方式可以增强表面载流子浓度,提升界面的电性能,但容易导致界面的可靠性下降,一般需要进行退火热处理才能消除高能粒子损伤带来的晶格缺陷[57]。

具有平整形貌、无缺陷的高质量半导体薄膜表面对于界面电传输性能和可靠性至关重要。Shen等[58]的研究表明,具有高缺陷密度的本征半导体表面会导致由硫族元素空位引起的费米能级钉扎效应,只有高质量的半导体薄膜才有可能形成饱和间隙态诱导的欧姆接触,进而获得较低的界面接触电阻。半导体的表面能和粗糙度会影响附着金属的形核模式和界面之间的范德华力[59],从而显著影响接触界面的电性能[60, 61]。例如,Feng等[62]发现金属Ni在高润湿Bi2SeyTe3-y表面呈层状生长,而在低润湿半导体表面呈现形核较差的岛状生长,因此光滑的无划痕表面可为获得较低的接触电阻提供基础。Zhang等[63]通过调节结晶方式和生长取向来控制Sb2Te3半导体的表面能,改善金属的形核方式,使高表面能、低粗糙度的本征Sb2Te3薄膜与Ni/Cu金属紧密结合,比接触电阻率降低至8.2×10-6Ω·cm2。激光表面退火可以平整重塑半导体表面结构[64],增强半导体表面的结晶性而不影响择优生长取向。例如,Joshi等[65]在电镀金属前用激光表面退火对Bi0.5Sb1.5Te3进行表面处理,使得热电材料表面在短时间内吸收高能光,表面结构被平坦化重塑并减少缺陷,这不仅增强了界面的电导率和热导率,而且还提高了金属和热电材料之间的结合力。因此,对热电半导体进行激光表面退火处理是一种有望大幅提高金属-半导体界面电传输性能和可靠性的手段,但目前的相关研究还比较少。

综合来看,热电薄膜器件中界面的结构设计和优化对于提升器件性能至关重要,也是未来热电薄膜器件研究需关注的重点。

3.3 热电薄膜器件应用

3.3.1 微能源采集

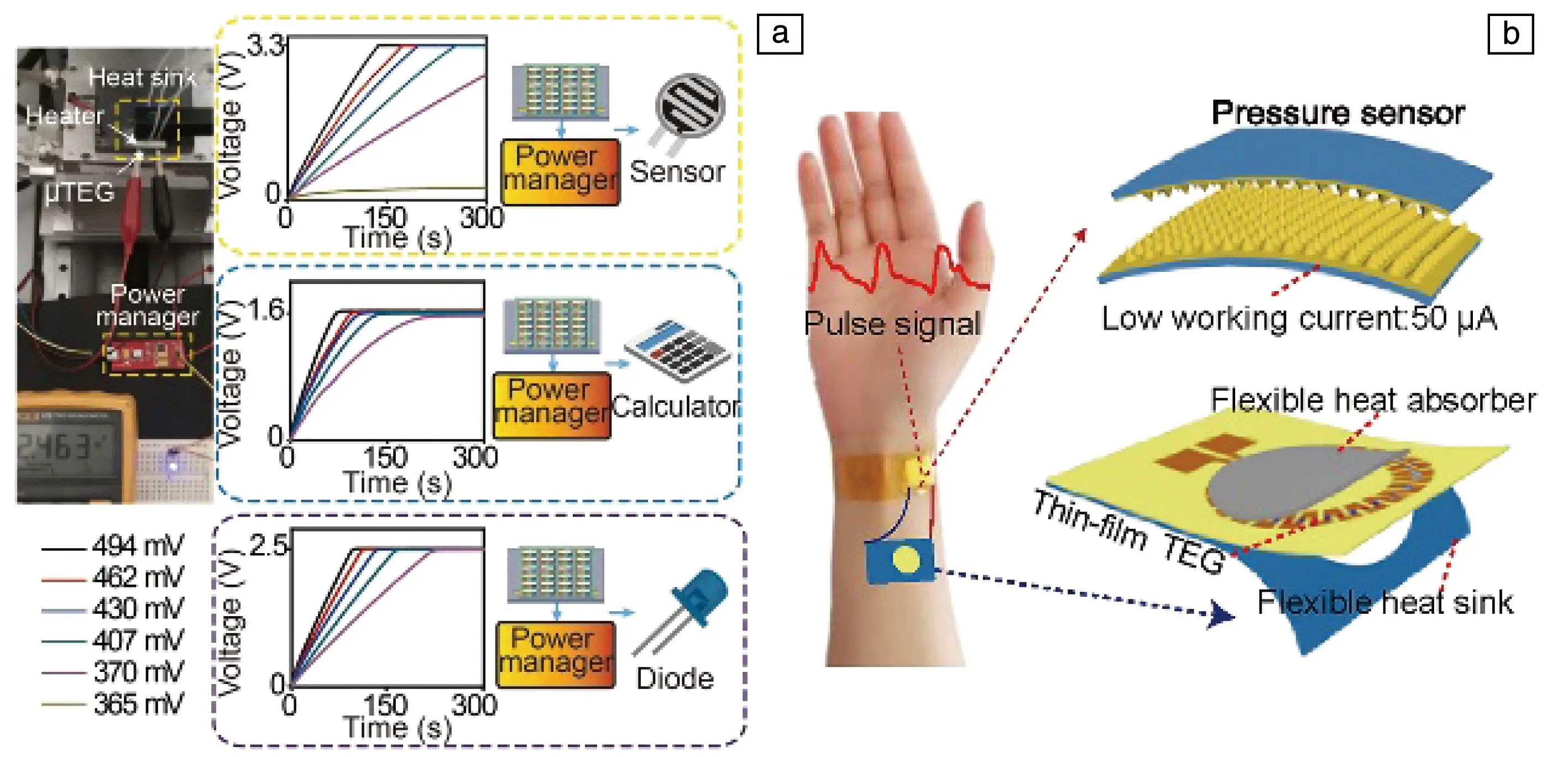

物联网和大数据时代的到来使得各种类型的微电子元器件需求量剧增,这其中有大量的元器件功耗仅在毫瓦级甚至微瓦级,传统使用电池或外接有线电源的供电方式需要消耗大量人力进行维护。与上述供电方式相比,基于温差发电的热电器件具有体积小、免维护、可靠性高、无污染等优势,非常适合作为低功耗元器件的供能方案。例如,Yu等[43]针对物联网传感器自供电的需求,利用超快激光微加工技术在1 cm×1 cm范围内集成了364对热电臂,制备出的热电薄膜器件在33.1 K温差下输出电压可达494 mV,足以驱动商用电源管理器,使得输出电压能稳定提升至3.3 V,可为压力传感器、计算器、二极管等低功耗器件供电(图8a)。Zhang等[41]使用脉冲电镀和微加工工艺,将127对热电臂嵌入SU-8基体中,通过自下而上的方式制备出的微型热电器件内阻仅约13 Ω,较低的内阻和高集成密度使得该器件在52.5 K的温差下最大输出功率密度可达9.2 mW·cm-2,可以用来收集低品位废热为无线传感器网络提供动力。为了直接从自然环境中获得大温差,Zhu等[66]利用菲涅尔透镜将太阳光汇聚至热电薄膜器件的热端,同时在器件冷端集成热沉,使得器件两端建立起大的温差。该装置在30 mW·cm-2的光照条件下可以产生150 mV的输出电压,同时还具有最高4.89 V·cm-2·W-1的光敏感响应,在自供电光传感领域具有广阔的应用前景。

近年来,用于人体生命体征监测的可穿戴设备迅速发展,利用人体体温与环境之间的温差为可穿戴设备供能的柔性热电薄膜器件也成为了研究人员重点关注的方向。例如,Zou等[67]通过MS在聚酰亚胺衬底上制备的Bi2Te3和Bi0.5Sb1.5Te3薄膜,即使以曲率半径5 mm弯曲900次后,薄膜的电阻仍能保持基本不变。基于该薄膜制备的柔性热电薄膜器件,在44 K的温差条件下,输出功率密度可达218.8 μW·cm-2,在柔性可穿戴电子器件领域表现出良好的应用潜力。Wang等[68]使用掩模辅助MS制备了Bi2Te3基柔性热电薄膜器件,将该器件用聚二甲基硅氧烷/氮化硼高导热复合材料进行封装后与水凝胶散热器进行集成,集成后的器件可利用人体体温与环境之间的温差,最高输出15.8 mV的电压。将集成后热电器件与柔性压力传感器集成后开发的自供电可穿戴式压力传感系统(图8b),可用于人体脉搏信号的连续不断监测。为了满足可穿戴设备所需的可拉伸性和轻便性,Guo等[69]受中国剪纸艺术的启发,创新性地设计出一种含有三维剪纸结构的Bi2Te3柔性热电薄膜器件,该器件仅重29 mg,在36 K温差下最大输出功率密度为255.395 μW·g-1,利用人体体温与环境的温差可实现54 mV的输出电压,且特殊的剪纸结构使得该器件在弯曲、扭转等机械变形状态下仍能表现出良好的性能稳定性,非常适合为可穿戴设备供能。

图8 热电薄膜发电器件的应用:(a)用于给压力传感器、计算器和二极管供电[43],(b)构建自供电可穿戴式压力传感系统[68]Fig.8 The application of thin-film thermoelectric generator device: (a) power supply for pressure sensor, calculator and diode[43], (b) construct a self-powered wearable pressure sensing system[68]

3.3.2 快速制冷与精准控温

除了用于微能源采集给低功耗器件供电外,基于Peltier效应的热电器件还可通过外加电流实现快速制冷和精准控温,特别是对于薄膜型热电器件来说,由于其体积小、制冷功率密度高,十分适合小空间、高集成度、高热流密度的局部控温应用场景。例如,2009年,Chowdhury等[70]将基于Bi2Te3基超晶格薄膜材料制成的热电器件进行封装后集成到硅芯片上,对热流密度高达1300 W·cm-2的目标区域实现了15 ℃的降温,这是将热电薄膜器件应用在芯片制冷领域的首次报道,展现出其在该领域的巨大应用潜力。Saber等[71]针对计算机芯片在使用过程中温度分布不均的问题,在芯片表面的热点区域集成了热电制冷器件,并通过理论计算结合实验验证的方式,证明了该器件可以在总面积为15 mm×15 mm、总发热功率为145 W的芯片上实现3 mm×3 mm尺寸热点区域内277.8 W·cm-2的制冷功率密度,可将芯片热点区域的温度控制在要求的阈值范围内。Li等[72]使用电化学沉积与光刻相结合的工艺在2 mm×2 mm尺寸范围内集成了220对热电臂,集成密度高达5500 对·cm-2。该器件在热电臂与电极之间无支撑材料的设计可有效减少使用过程中的内应力,因此即使经过高达1000万次冷却循环和在恒定电流下服役超过30 d,器件仍能保持正常工作,表现出极高的稳定性。

4 结 语

本文以Bi2Te3基热电薄膜材料与器件为主线,对热电薄膜的制备方法、热电薄膜器件的设计制备与界面优化,以及热电薄膜器件在微发电和快速制冷领域的应用等方面做了介绍。当前,温室条件下Bi2Te3基热电薄膜热电优值已突破2.0的大关,基于薄膜材料的热电薄膜器件性能也不断取得突破。然而,要使热电薄膜器件能够实现大规模商用,依然有以下问题亟需解决:① 在材料方面,目前的Bi2Te3基热电薄膜最佳性能温区较窄,无法在宽温域范围内保持高热电性能,需进一步优化其最佳性能温区;② Bi2Te3基热电薄膜是各向异性的,当前薄膜电导率和Seebeck系数等性能只能实现面内方向的准确测量,然而在面外型器件工作过程中使用的是薄膜面外方向的性能,因此亟需发展薄膜热电性能的面外表征手段;③ 薄膜型热电器件体积小、集成度高,加工集成工艺比块体器件要更为复杂,特别是对于制冷器件来说,要想获得好的制冷性能,热电薄膜与电极间的键合工艺十分重要,必须解决界面间的力学匹配和热学匹配问题;④ 在服役条件下,热电薄膜与电极之间会存在界面扩散的现象,引起界面接触电阻的升高,使器件的性能衰减,因此如何提高薄膜器件在服役条件下的性能稳定性也是亟需解决的问题。未来,随着物联网、可穿戴设备领域的进一步发展,用于小空间高热流密度电子器件快速散热以及实现低功耗传感器节点自供电的热电薄膜器件将具有迫切的应用需求和广泛的市场前景。