一种基于FPGA资源复用的时域脉压方法

王辉辉 袁子乔 徐 伟

(西安电子工程研究所 西安 710100)

0 引言

雷达数字脉冲压缩主要有时域和频域两种方法,时域脉压处理方式更直接,处理效率要高于频域脉压,同时处理速度也快,频域脉压处理时间随着处理长度的增加成对数增加,而时域脉压处理时间只与滤波器阶数有关,与输入数据长度无关[1]。特别是当距离单元较大时,采用频域实现运算过程复杂,延迟大[2]。FPGA在数字信号处理的硬件实现中扮演着重要角色[3],使用FPGA设计出特定的结构来实现具体的信号处理算法,能提高系统的算法实现性能和执行效率[4],因此对于实时性要求高的雷达系统,一般利用具有在线动态重构能力的FPGA平台来实现时域脉压。软件化雷达通过开放式架构和软件化设计能灵活地实现系统扩展、更新和升级[5],极大地增加了雷达灵活性。软件化雷达存在功能可重构要求,需要重构多种可变波形,如果针对不同波形分别独立设计时域脉压,这将大大增加了FPGA的乘法器和存储器资源。因此为满足软件对波形的可重构性,本文提出了一种基于资源复用的时域脉压方法。该方法通过复用FPGA的乘法器和存储器资源,重构滤波器系数和参数,能实现对多波形多波束多数据率的脉压处理。

1 脉冲压缩原理

系统输入端信号为

x(t)=s(t)+n(t)

(1)

其中,s(t)为目标回波信号,n(t)为系统噪声。s(t)的频谱为

(2)

由匹配滤波理论可知,如果时域脉压滤波器的频率响应为:H(f)=S*(f)e-j2πft0,则滤波器输出端的信噪比最大,响应的脉冲响应为

(3)

其中t0是滤波器的时延,因此时域脉冲滤波器的脉冲响应为收入信号的镜像共轭。在忽略噪声情况下,脉冲压缩输出为

y(t)=x(t)*h(t)

(4)

2 设计实现

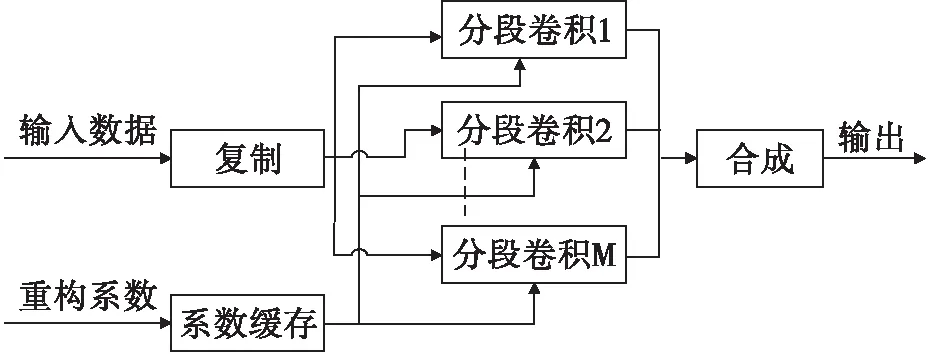

软件可重构的脉压面临不同波形、不同数据速率、不同波束个数分时工作的可能,因此进入脉压模块的数据速率是不同的,波束个数也不同,但对于数据速率确定、波形样式确定的工作模式,时域脉压的匹配滤波器系数就是固定的,该数据速率该波形条件下的一个波束数据的时域脉压实现所需的资源是固定的。时域脉压采用滤波器进行处理,滤波器的阶数和波形及采样率是相关的。基于资源复用的时域脉压处理流程图如图1所示,将输入的数据进行复制分割得到多个数据段,每个段和对应的系数进行乘累加操作,最后将多段的结果合成输出。通过系统控制重构系数,即可实现不同波形的脉压处理。

图1 资源复用时域脉压处理流程图

2.1 设计原理

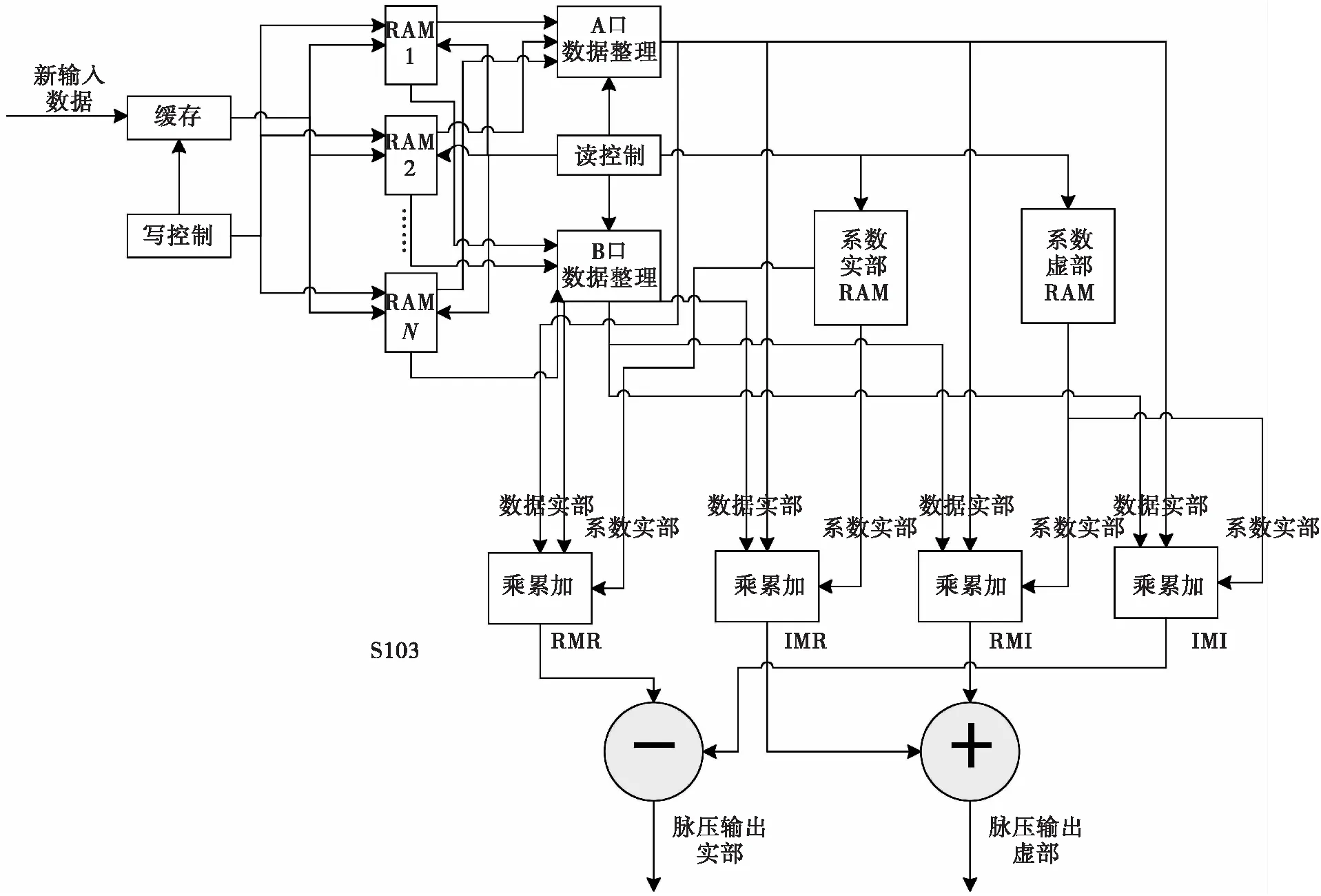

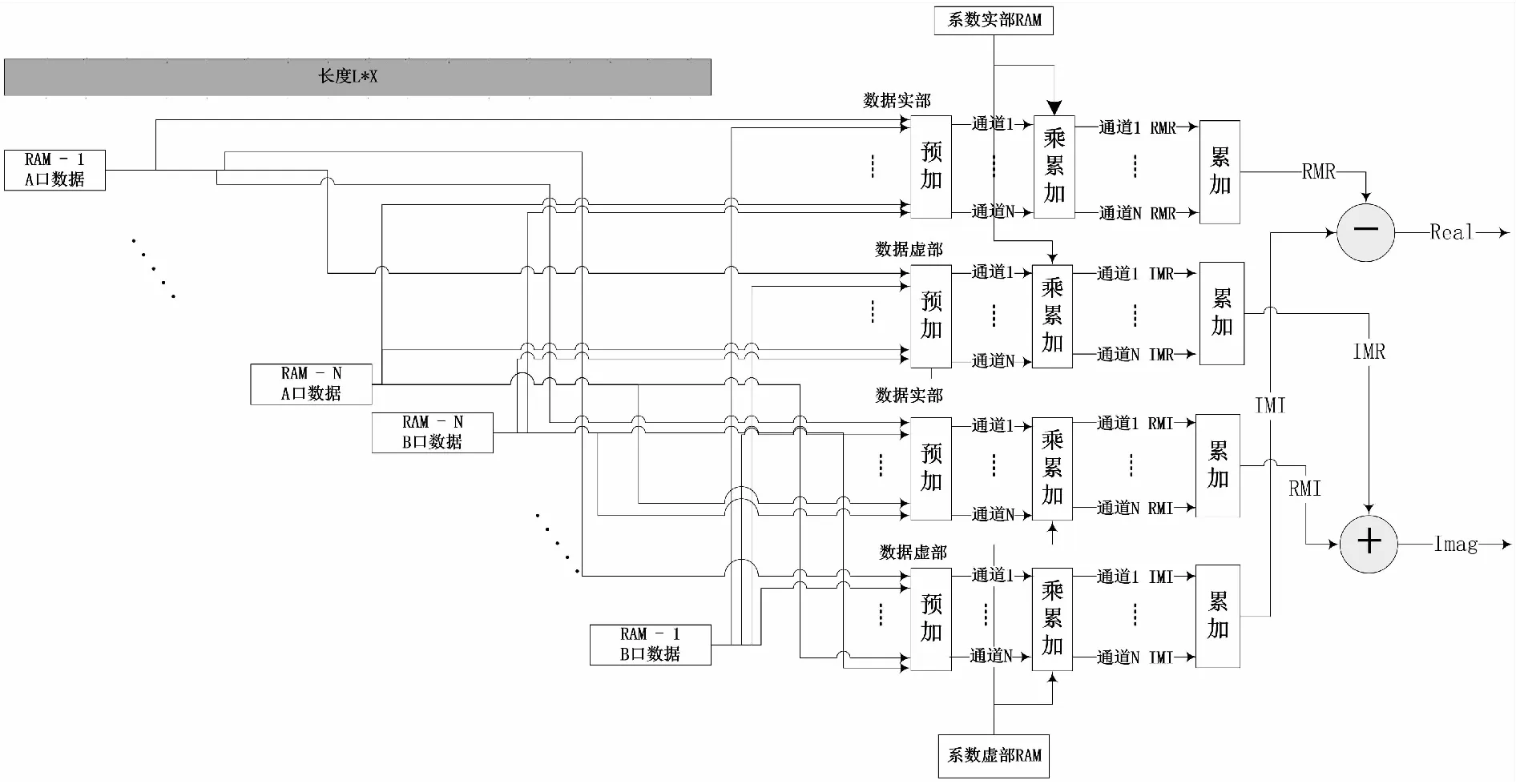

基于Xilinx公司7系列FPGA的资源复用的时域脉压详细设计图如图2所示,首先对输入数据进行缓存,计算并行处理通道个数,并初始化所有处理通道,然后将输入数据写入多个双口RAM;其次进行数据读处理,根据读时间片产生读地址和读控制信号,控制数据从双口RAM两个口正序和反序对称读出,并对读出的数据进行结构调整处理,使得多余的数据不参与计算,根据系统选择重构滤波器系数和控制参数;一般来说,雷达系统为了节省系统资源,采用的波形一般都是奇对称或偶对称的,最后根据重构系数的对称特性,对处理后的数据进行相应的预加处理,并将预加后的数据和对应的滤波器系数进行乘累加操作得到脉压输出,通过重构滤波器系数和控制参数可实现不同波形对相同乘法器的复用。

图2 资源复用时域脉压详细设计

2.2 数据缓存

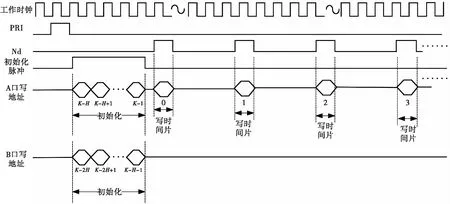

根据输入数据速率、系统工作时钟频率以及时域脉压滤波器阶数这三个参数来计算需要并行处理的通道个数,一个通道对应一个双口RAM。不失一般性,假定当前波形的脉冲宽度为L(μs),系统时域脉压模块的工作时钟频率为X(MHz),脉压模块输入的数据率为Y(MHz),M=X/Y,M为大于等于1的正整数。根据波形的对称特性,与当前波形相匹配的脉压匹配滤波器的阶数为:H=ceil(L×X/2),需要同时处理的通道个数为:N=ceil(H/M),ceil为向上取整。FPGA中存储数据的双口RAM的深度K应当大于L×X,并且K为2的整幂次方。由于存储数据的双口RAM不具备数据清零操作,为了不同的脉冲重复间隔(PRI)之间数据进行脉压处理时互不影响,需要在一个新的PRI到来时,对双口RAM进行清零操作,也就是将双口RAM中的最后面的深度为L×X的缓存区置零。当PRI到来时,产生一个初始化脉冲,该脉冲的周期个数为H。为了减少清零时间,对N个双口RAM的两个输入口A和B同时进行写操作,A口写地址从K-H开始写,B口地址从K-2×H开始写,这样大大减少了清零的时间。当置零结束后,写控制模块控制数据按照X(MHz)的速率从缓存区读出,数据的有效信号如图3中的Nd信号所示,当有效信号为高电平时,将A口地址进行累加操作,增量为1,同时在写时间片内将数据同时写入N个双口RAM的A口中去,完成数据的写操作。在写时间片内,B口不进行写操作。数据写缓存的操作时序见图3所示。

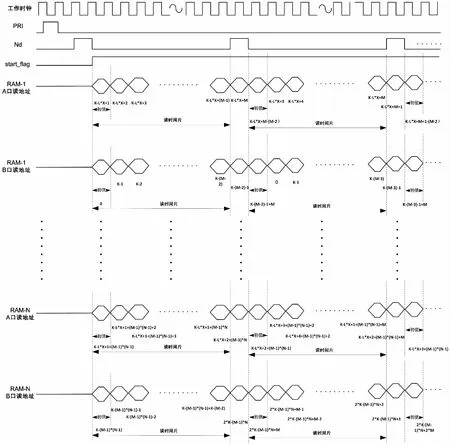

图3 数据缓存时序图

2.3 数据读处理

数据读处理控制时序如图4所示,当第一个输入数据写入N个双口RAM中后,由读控制模块产生一个开始脉压处理的标志信号start_flag,该信号在PRI脉冲到来时进行复位操作,也即将start_flag置为低电平。当第一个输入数据的Nd到来后,将该信号置为高电平,高电平一直保持到下个PRI脉冲到来。在start_flag为高电平期间进行读操作,每输入一个新的数据也就是一个新的Nd到来时,需要对双口RAM的A口和B口的读地址赋初值。当第一个Nd到来时,第一个双口RAM的A口和B口的初始化读地址为:K-L×X+1和0;第二个双口RAM的A口和B口的初始化读地址为:K-L×X+1+(M-1)和K-(M-1);…… 依此类推,第N个双口RAM的A口和B口的初始化读地址为:K-L×X+1+(M-1)×(N-1),K-(M-1)×(N-1)。在Nd信号不为高且start_flag信号为高电平的读时间片内,所有通道的双口RAM的A口的读地址进行累加操作,增量为1。所有通道的双口RAM的B口的读地址进行递减操作,递减量为1,如图4所示。从第二个Nd信号到来开始,每当一个新的Nd信号到来时,所有双口RAM的A口的读地址在当前的基础上减去一个固定值,该值为(M-2)。所有双口RAM的B口的读地址在当前的基础上加上一个固定值,该值为M。然后将当前值作为A口和B口下一个读时间片的初始值,当读时间片到来时,所有RAM的A口的读地址进行累加操作,增量为1,B口的读地址进行递减操作,递减量为1。按照上述过程重复进行,由于在FPGA中地址是定点数,双口RAM的A口和B口的地址循环范围为0~(K-1),因此当地址为K-1时,如果地址进行自加1操作,则下一个地址变为0;当前地址为0,如果地址进行递减1操作,则下一个地址变为K-1;因此通过循环地址的读操作就可实现数据的正序列和反序列对称输出。在数据读出后需要对数据进行整理,只对最后一个通道进行处理,其他通道数据保持不变。在所有的读时间片内,都将最后一个通道的RAM的B口输出数据的前H-(M-1)×(N-1)个数据保留,而该通道B口输出的其他数据强制置零。这样不管对于奇对称还是偶对称能保证一个完整的数据长度L×X被读出来进行脉压。数据整理模块输出数据时,读控制模块同时控制滤波器系数读出,并将系数和数据同时送入乘累加模块进行处理。

图4 数据读时序图

2.4 乘累加

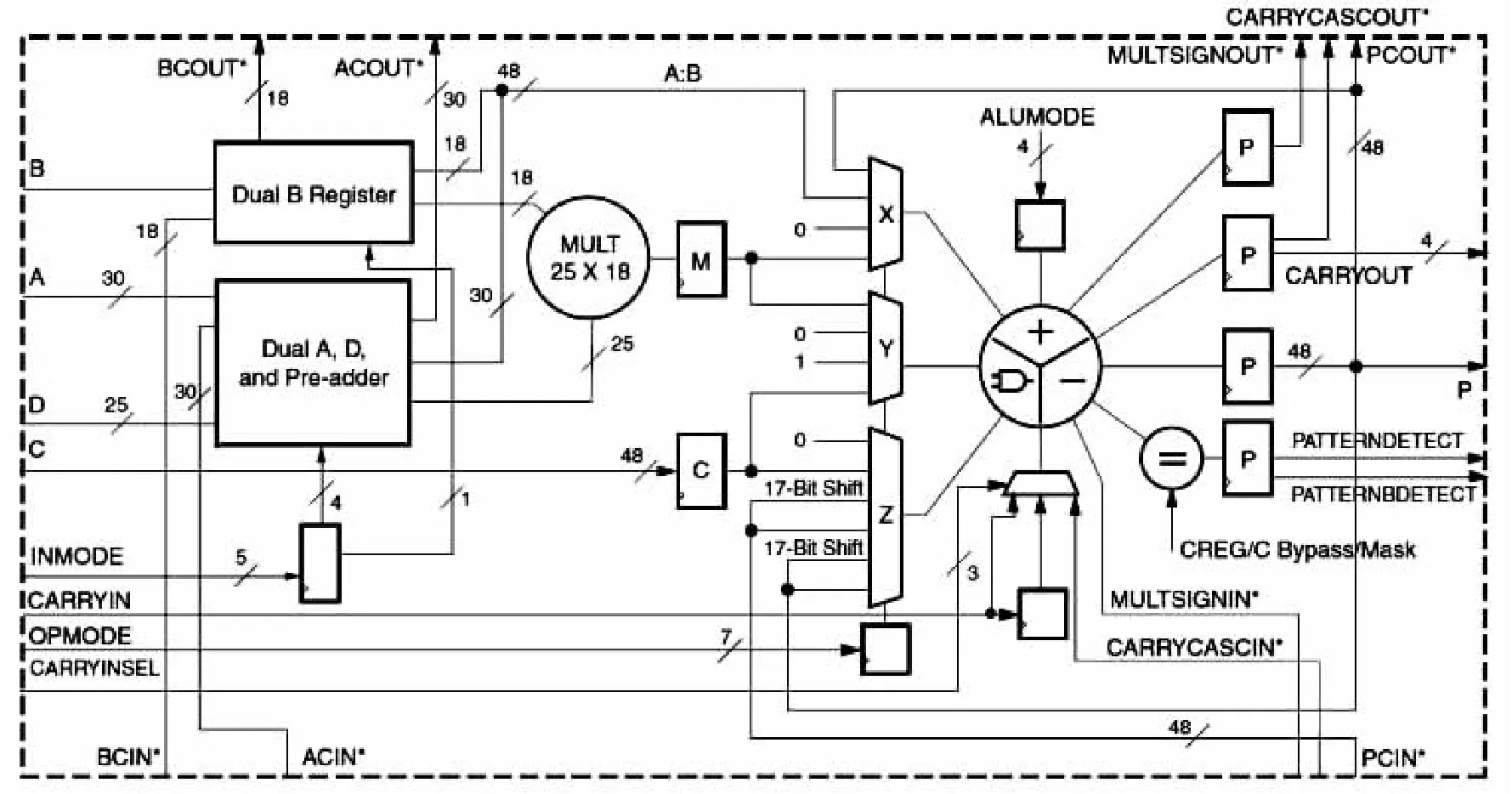

本文中的乘累加模块使用FPGA自带乘累加的IP核,该IP核可以对输入口A和D的两路数据进行预加处理,然后将预加的结果和B口输入数据相乘,相乘结果可以从C口输入和下一个乘的结果进行累加操作并输出,该IP核的原理图如图5所示。

图5 乘累加器IP核原理图

将同一个通道的A口和B口整理后的数据送入FPGA自带的乘累加IP核的A口和D口,先进行预加处理,也就是将A口和B口对应的数据先进行加法计算。同时将系数从系数RAM中读出,送入乘累加IP核的B口,预加的结果和C口对应的系数相乘得到第一个数据的乘结果,并在一个读时间片内将相乘的结果反馈到乘累加IP核的C口,实现当前读时间片内所有乘结果的累加,从而得到当前读时间片内的当前通道的乘累加输出结果,最后把N个通道当前读时间片内的结果对应相加就得到了该读时间片内最终的乘累加结果,也就是一个脉压输出值。数据和系数都为复数,因此一个通道需要四个乘累加器。

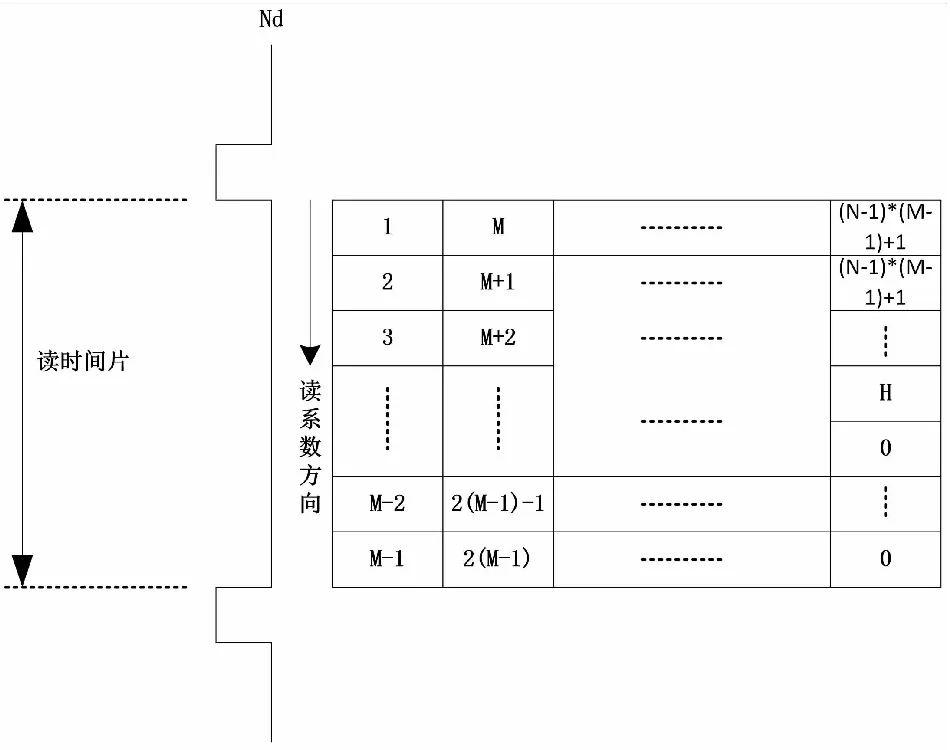

滤波器系数可通过软件进行重构,由于划分了N个通道,因此滤波器的系数存储需要做特别的处理,滤波器系数矩阵按照M-1 行N列进行存储,第一列存储滤波器系数的1~M-1第二列存储滤波器系数的M~2×(M-1),依此类推,第N列存储滤波器系数的(N-1)×(M-1)+1~H,第N列未填满的共(M-1)-(H-(N-1)×(M-1))-1 个数据进行补零处理,在重构不同滤波器系数时,只需要按照次规则生成对应系数矩阵,并将矩阵写入FPGA的内部存储器RAM中即可。

读控制模块在每个读时间片内对该RAM进行读取,按照当前波形对应的脉压滤波器系数存放的地址依次读出滤波器系数。滤波处理是个线性卷积的过程,为直观可见,本文仅以一个长度为L×X的完整输入数据的乘累加过程示例,乘累加数据控制流程实现如图6所示。在每个读时间片内,将第一列系数和第一个通道的预加后的数据依次相乘并进行乘累加,第二列系数和第二个通道读时间片内的预加后的数据依次相乘并进行乘累加,依此类推,第N列系数和第N个通道读时间片内的预加后的数据依次相乘并进行乘累加。重构系数读取如图7所示,每个读时间片内都按照行地址进行递增,一次读出一行的数据,并把该行的N个数据分别对应的送到N个通道,依次循环往复,直到所有输入数据全部处理完毕。

图6 乘累加处理流程图

图7 系数矩阵读取示意图

3 仿真与实现

利用本文的设计,对某相控阵雷达的三种波形进行仿真验证。波形1脉冲宽度为1.5μs,波形2脉冲宽度为31μs,波形3脉冲宽度为40μs。三种波形对应的带宽也不同,所形成的波束个数也不一样。使用乘法器资源最多的为40μs对应的波形。因此该系统设计只需要满足40μs所需资源即可,其余消耗资源少的波形都可以通过参数重构来实现,不局限于本文仿真的三种波形,只需要按照本文设计进行计算,所需资源少于最大资源,都可以进行重构脉压处理。

波形1的脉压仿真结果如图8所示,波形2的脉压仿真结果如图9所示,波形2的脉压仿真结果如图10所示。通过重构不同的滤波器系数和配置参数,在相同资源的条件下实现了三种波形的脉压结果,验证了本文方法的正确性。

图8 波形1对应脉压仿真结果

图9 波形2对应脉压仿真结果

图10 波形3对应脉压仿真结果

4 结束语

以软件为核心的软件化雷达是未来雷达的重要发展方向,通过灵活的软件化重构即可实现系统的扩展、更新和升级。因此软件化雷达存在不同波形不同波束不同数据速率的脉压需求,如果对多个波形的脉压进行分别设计,则大大增加了FPGA内的资源消耗,并且不利用系统重构。因此本文设计了一种基于资源复用的时域脉压方法,根据系统波形和FPGA 资源,计算得到最大化的可用资源,只要脉压资源小于所使用的最大资源,通过重构滤波器系数和配置参数,在不改变系统设计的条件下即可实现多波形的脉压,能满足对多波形多波束多数据率的重构需求。本文所提方法在一定程度上推动了软件化雷达发展。