基于FPGA 的RS-422/485 芯片自动化测试平台的设计与实现

宋晨阳,吴 松,何 威,时晓升

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

随着芯片国产化的飞速发展,国产芯片的测试需求也日益增加。集成电路测试[1]技术作为保证集成电路性能和质量的关键环节,其在集成电路产业中的重要性不言而喻。国内在芯片自动化测试系统领域基础较弱[2],多数自动化测试都基于国外引进的测试设备[3]开展,在量产测试中主要采用国外自动化测试设备ATE(Automatic Test Equipment)。但是ATE测试机台价格昂贵,测试程序开发也较复杂[4]。同时,芯片测试模式下,ATE 测试机有别于传统嵌入式软件,测试程序也无法在线修改,不能进行现场调试。而在国产芯片研发阶段的测试过程中,需要根据实际测试结果,实时调整测试方法和程序等。显然,ATE 测试并不适用实验环境下的自动化测试[5-6]。所以,实验环境下,提供一套低成本、灵活性高、测试范围广的自动化测试系统[7-9]成为亟待解决的问题。

该文针对国产RS-422/485收发芯片的功能测试,设计并实现了一种自动化测试平台,通过上位机[10-11]界面控制,可以同时实现多种隔离型、非隔离型RS-422/485 收发芯片的通信测试。

1 系统概述

测试平台主要由外部电源、测试底板和测试主机构成。测试底板包含电源控制模块、FPGA 控制模块、待测器件和串口通信模块;测试主机即PC 机,配有基于LabVIEW 软件开发的上位机程序;外部电源为两路隔离电源,为测试底板上的器件供电,并且通过测试底板上的电源模块的开关控制可以实现RS-422/485 收发芯片在3.3 V/5 V 两种工况的切换。测试平台架构如图1 所示。

图1 测试平台架构

2 硬件设计

2.1 FPGA控制模块硬件电路设计

核心控制模块的主控制器为FPGA,具体型号为EP3C25Q240C8N,此款FPGA 是由Altera 公司生产的cyclone3 系列FPGA,具有成本低廉、功耗小、性价比高等优点,其性能指标也满足测试平台的使用要求。FPGA 主要实现两项的主要功能:1)向RS-422/485 发送器发送相应的测试码,并对相应的接收器的数据进行回读,通过与发送数据进行比对,计算出待测芯片数据传输的误码率;2)通过底板232 串口模块完成与上位机之间的通信,接收并处理上位机的控制指令以及上传误码率等测试结果。

FPGA 的外部时钟参考源选择50 MHz 有源晶振,配置电路部分采用专用配置芯片,型号为EPCS16SI8N,该芯片内部自带16 Mb Flash 存储容量,可擦写次数大于100 000 次。在系统调试阶段,可以通过底板JTAG 接口实现在线调试,后期通过AS 接口将程序固化至配置芯片的内部Flash 中,实现上电后程序自启动。由于需要测试芯片在两种不同的电压等级下测试,在5 V 测试条件下,FPGA 与待测芯片之间的数据信号需要进行3.3~5 V 电平转换,底板上采用两片电平转换芯片,并由FPGA 控制其转换通道的开关状态。FPGA 启动模式配置如图2所示。上位机串口232通信模块原理图如图3所示。

图2 FPGA启动模式配置原理图

图3 上位机232串口通信模块原理图

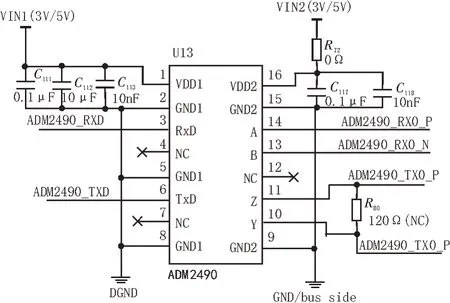

2.2 RS-422/485通信模块硬件电路设计

RS-422/485 是现代工业中应用范围极为广泛的两种通信接口,都可以实现主设备和从设备之间的数据传输。两者的主要区别是RS-485[12]通信是一种半双工通信方式,其接口采用平衡驱动器和差分接收器,需要两根数据线,其中一线定义为A,另一线定义为B。而RS-422[13]是在RS-485基础上提出的一种全双工的通信方式,即有四根信号线,四根信号线分别定义为Y、Z、A、B。Y、Z 用于发送,A、B 用于接收。两者的电气性能指标一致,最大通信速率为10 Mb/s。

目前,市场上RS-422/485 收发器大致分为两类,即隔离型和非隔离型,隔离型芯片一般内部含有DC-DC 电路模块,采用变压器耦合的方式实现电气隔离。在电路设计中,非隔离型收发器的数据端和总线端需要采用两路隔离电源进行供电。目前,国产化芯片大多是对标国外主流芯片厂家的相关型号进行仿制,同一种功能类型的RS-422/485 收发芯片的封装也大多采用如SOIC-16 等标准封装。为了保证平台的通用性,同时有效地控制设计成本,选用了三款芯片测试插座,分别用来放置隔离型RS-422/485、非隔离型RS-422、非隔离型RS-485 三种类型的某国产化芯片。为了便于对比测试,选用国 外ADI 公 司 的ADM2682、ADM2486、ADM2490。ADM2682 为 隔离型RS-422,ADM2486 为RS-485,ADM2490 为非隔离型RS-422。其中一路非隔离型RS-422 通信模块部分原理图如图4 所示。

图4 非隔离型RS-422通信模块部分原理图

为了验证硬件设计本身的可靠性,需要首先进行板级测试[14],将已经通过筛选考核的国外成品芯片(如ADM2490)的引脚按照“Y—A、B—Z”的接线方式进行自回环测试,若通信测试正常,则说明板级链路功能正常,可以进行国产芯片的通信测试。

通过软件配置可以实现“国产芯片发送/国外芯片接收”或者“国产芯片接收/国外芯片发送”两种通信模式,以此来测试国产化芯片数据发送功能以及接收功能是否正常。上述两种测试模式不仅可以实现芯片的板级测试,还可以通过测试平台的DB9 接口将RS-422/485 总线用电缆引出,以模拟长距离通信的实际工业应用场景。

3 软件设计

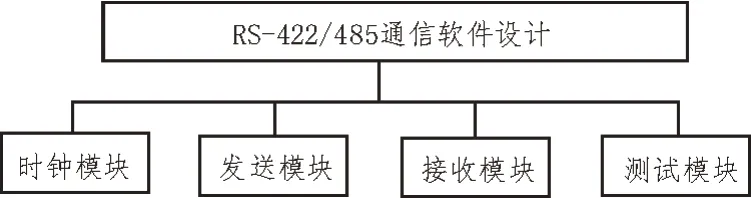

3.1 RS-422/485通信软件设计

测试平台的通信软件基于FPGA 开发,开发环境为Quartus 12.1,采用Verilog 编程语言。由2.1 节可知,软件功能设计主要考虑上位机与测试系统之间的通信和测试系统与待测芯片之间的通信。待测芯片和测试系统之间通过GPIO 接口相连。程序主要分为四个模块:时钟模块、发送模块、接收模块、测试模块。软件功能框图如图5 所示。

图5 软件功能框图

时钟模块的程序设计主要是考虑到芯片的用户在实际使用中,可能会选择不同的工作频率,为了确保国产化芯片通信测试的完整性。需要实现RS-422/485 通信[15]速率0~10 Mb/s(最大通信速率)可调。程序中利用PLL 将PFGA 主时钟进行二分频,再通过对参数的选取实现测试频率可调。由于偶数分频,部分频率设置需要近似,RS-422 常见波特率,如9 600 Baud、115 200 Baud 等数值的近似误差都小于0.1%,满足实验要求。

发送模块和接收模块用于完成FPGA 与待测芯片的通信。如ADM2486 芯片,需要对其数据发送TXD、数据接收RXD、接收使能RE、输出使能DE 等引脚进行控制。

测试模块主要完成与上位机之间的协议通信,接收处理上位机的控制命令,和将三款国产化芯片的测试数据结果打包发送给上位机。测试模块与上位机通信的协议帧格式主要包含起始位、波特率设置位、数据量设置位、数据位、校验位、停止位。再将三款国产化芯片的测试数据结果打包发送给上位机。

3.2 上位机自动化测试程序设计

上位机软件是RS-422/485 芯片测试平台实现自动化测试的核心,主要通过平台外部串口实现测试参数设置、测试命令下达以及从平台内存储器采集测试数据[16]。上位机软件功能主要划分为三个模块,即通信配置模块、数据上传模块、统计分析模块。各模块的详细功能如图6 所示。

图6 上位功能结构图

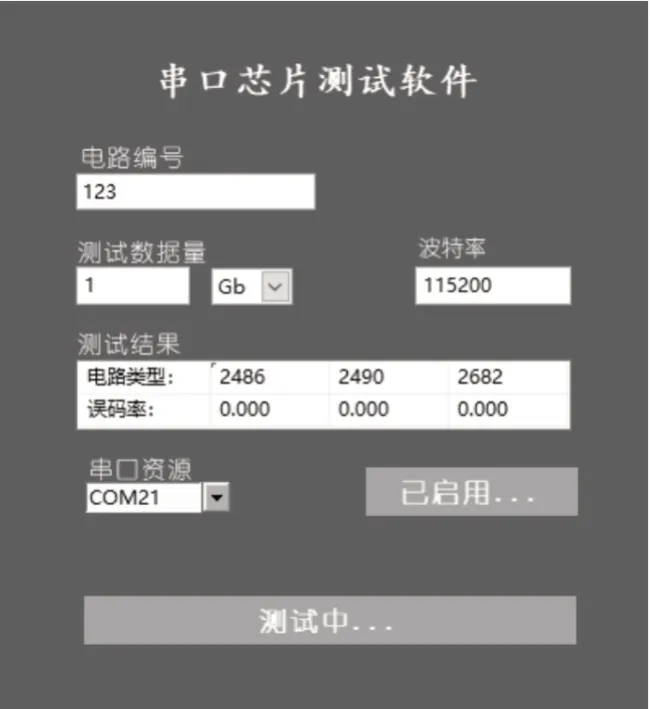

简洁合理的上位机软件的窗体设计能给芯片测试人员带来诸多便利。考虑到上位机的实际功能,使用单文档界面作为上位机软件界面。上位机界面如图7 所示。

图7 上位机界面

4 实验测试与结果

实验时,首先使用外部电源给底板供电,使用RS232-USB 串口线将测试底板与电脑连接,启动上位机软件,打开相应串口,输入电路编号,如123;设置需要的测试数据量、波特率后,点击开始测试按钮,便可以启动测试。测试过程会实时显示三种待测芯片的通信误码率,并将测试结果放置在自动生成的CSV 文件。选取某一次测试过程截图如图8 所示。可以看到在波特率数值为115 200 Baud 时,三种国产芯片数据传输误码率都为0。

图8 测试过程

考虑芯片的实际应用场景,不同用户选择通信模式、通信速率、数据量等也存在差异,为了保证测试结果的可靠性,设置三种通信测试模式:发送模式、接收模式和自回环模式;除了选择串口常用波特率2 400 Baud、4 800 Baud、9 600 Baud、19 200 Baud、115 200 Baud 之外,在RS-422/485 允许通信速率0~10 Mb/s 范围内,进行扫频测试,步长为0.2 Mb/s;数据吞吐量范围为1~10 G,步长为0.5 G。测试结果表面,三种对标国外ADI 公司的ADM2682、ADM2486、ADM2490 国产化芯片数据收发功能正常。可基本实现对国外同类型芯片的功能替代。

从实验过程可以看出,测试人员仅需要完成上电、测试芯片更换等基本操作,便可以通过上位机界面实现国产RS-422/485 收发芯片的一键自动化测试,极大地提高了实验环境下的测试效率。除此之外,测试平台硬件设计也充分考虑了环境温度对通信稳定性的影响,测试硬件可整体置于-40~85 ℃的环境温度下进行自动化测试,满足工业环境温度要求。

5 结束语

该文通过嵌入式软硬件和上位机程序设计,实现一种RS-422/485 芯片自动化测试平台。详细介绍了FPGA、RS-422/485 的硬件电路、RS-422/485 通信程序和上位机自动化测试程序的设计,并通过实验对自动化测试平台的功能进行了验证。研究表明,该自动化测试平台可以实现多种RS-422/485 芯片的全速率范围的通信能力测试,能够满足实验环境下国产芯片的测试要求。