基于VHDL语言的74LSl60计数器电路设计

江苏商贸职业学院 蔡广飞

目前,电子设计自动化技术(EDA)已经广泛应用于电路设计领域。本文介绍了使用VHDL语言设计74LSl60计数器,结合波形仿真工具,验证设计是否正确。

1 电子设计自动化技术

电子技术的发展给人们生活带来巨大的改变,各类电子产品层出不穷。近年来,电子系统的设计方法也发生革命性的转变。早期的数字电路设计,主要针对电路板进行,设计过程中,把一些具备指定的集成电路按要求摆放在电路板上,最后,通过设计电路板,完成电路功能的设计。20世纪90年代以后,基于EDA技术的电子系统设计已经成为主流[1]。

EDA,电子设计自动化的简称。以计算机为主要的设计工具,结合由多学科多领域的最新科技成果得到的各类软件,可以帮助工程师们完成电路的相关设计。利用硬件描述语言进行电路与系统的设计是当前EDA技术的一个重要特征[2]。由于较强的电路仿真能力,相较于传统的设计方法,它更加适合大型、复杂的电子系统设计,它还是进行逻辑综合优化的重要工具,具有如下突出优点:(1)语言的公开利用性:硬件描述语言可在不同的开发平台上进行使用,设计者只需遵循语言的使用规则,即可完成设计任务;(2)电路设计与生产工艺无关性:设计者不需要考虑器件的工艺结构,能够方便地从逻辑行为级别进行描述和设计电路系统;(3)描述能力强;(4)便于组织大规模系统的设计。

2 VHDL语言概述

超高速集成电路描述语言VHDL是由美国国防部开发,后被IEEE(Institute of Electrical and Electronics Engineers,电气与电子工程师协会)确定为标准化的硬件描述语言,经过1984年的修订,新增部分命令与属性,增强描述能力。VHDL语言能在电路设计时,对其进行仿真、模拟,便于发现设计存在的不足,有效地减少了可能发生的错误,降低实际的开发成本。

VHDL语言是一种行为描述语言,其编程结构和C语言相似。同时,程序本身也让设计师门易于接受。VHDL语言使用周期长,与器件工艺无关,不会因为工艺技术的发展,导致程序失效。当电路的工艺改变时,只需在程序中对相应的属性参数作出修改即可。

它可以完成多层次的设计描述功能,VHDL程序既可以设计系统级电路,也可以完成对门级电路的设计与描述。具体的描述方式可分四种:(1)行为描述;(2)寄存器传输描述;(3)结构描述;(4)采用三者混合的混合级描述。需要说明的是,VHDL语言在原有的数据类型基础上,支持用户自定义的数据类型,使硬件开发者有着较大的自由空间,便于创建高层次的系统模型。

3 MAX plusII开发工具介绍

近年来,FPGA和ASIC的设计在规模和复杂度方面不断取得进展,它们的设计也离不开EDA软件的帮助,在众多设计工具中,MAX plusII是常用的开发工具之一,它是由Altera公司开发的一个电路系统开发工具,采用了先进的工艺和全新的逻辑结构,支持多种设计输入方式,包含原理图输入、文本输入等,它会把设计内容转换成最终结构所需的格式,支持波形仿真,设计简单高效。因为有关结构的相关知识已经装入MAX plusII开发工具,目前能够支持业界多家EDA公司提供的工具接口。因此,设计者不需手工优化自己的设计,实现非常快速的电路系统设计。

本设计采用MAX plusII开发工具,利用波形仿真功能,验证设计电路的功能是否准确,过程简单易懂,形式生动有趣,结果直观明了。

4 程序设计

能累计输入时钟脉冲个数的逻辑电路称为计数器,它也是数字电子系统中的基本逻辑器件,除了具有计数功能外,还可用于定时、分频、产生节拍脉冲序列及进行数字运算等[3]。同时,它还是一种时序逻辑电路,由各类门电路和触发器构成。

计数器的种类很多,根据不同的分类依据,存在多种多样的分类方法。按照触发器翻转的时序不同,可分为同步计数器和异步计数器,若系统中所有的触发器共用一个时钟信号,则称为同步计数器,反之,称为异步计数器;按照计数功能的不同,可分为加法计数器和减法计数器,加法计数器每来一个脉冲计数值加1;减法计数器每来一个脉冲计数值减l;按照计数类别的不同,可分为二进制计数器、十进制计数器、N进制计数器,例如,输出二进制代码来表示所累计脉冲个数的计数器称为二进制计数器。

同步计数器中的全部触发器的时钟信号来自同一个脉冲,各个触发器的翻转和时钟脉冲同步,具有工作速度快,工作频率高的优点[4]。异步计数器的电路结构虽然简单,但由于它的进位或借位信号是逐级传递的,因而工作的速度收到限制,电路的级数越多,工作的延时越长,甚至会造成系统的逻辑错误,因此,同步计数器在高速数字系统中受到设计师们的青睐。

74LS160是一个十进制计数器,内部由JK触发器和逻辑门电路构成[5],它具有清零端CLR和置数端LD,计数控制信号p和t,可以实现清零、置数、保持和计数的功能。

74LS160的功能如表1所示,在实际工作中,若清零端有效,则电路输出0;若置位端有效,则电路输出与输入保持一致,完成置数功能,若清零端和置数端无效,p和t有一个为低电平时,计数器输出保持不变,执行保持功能;当计数控制信号p和t且清零端与置数端无效时,电路执行计数功能,当检测到到第十个脉冲时,计数器输出端显示为0,并给出相关信号,完成一个循环[6]。

表1 74LSl60功能表Tab.1 Function table of 74LSl60

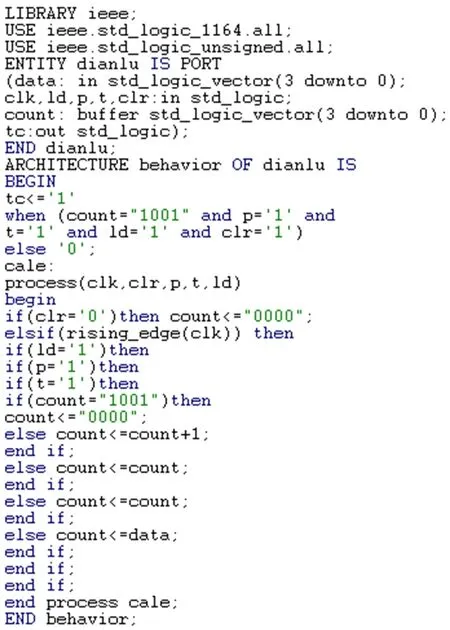

基于对功能表的分析,利用VHDL程序设计计数器电路。如图1所示,程序的实体名为Dianlu,实体中包含一个结构体Behavior,结合74LSl60的功能表,程序列出了4位的置数端Data,4位的输出端Count,此外,程序列出了相关功能的控制信号。

图1 74LSl60计数器的VHDL程序Fig.1 VHDL program for 74LSl60 counter

5 功能验证

如图2所示,当复位信号有效时,电路输出为0;当复位信号无效时,电路执行其他的功能。

图2 清零功能波形图Fig.2 Waveform of zeroclearing function

如图3所示,Data值为“1100”,在复位信号无效,置位信号有效的条件下,输出为“1100”,完成置位功能。

图3 置位功能波形图Fig.3 Waveform diagram of setting function

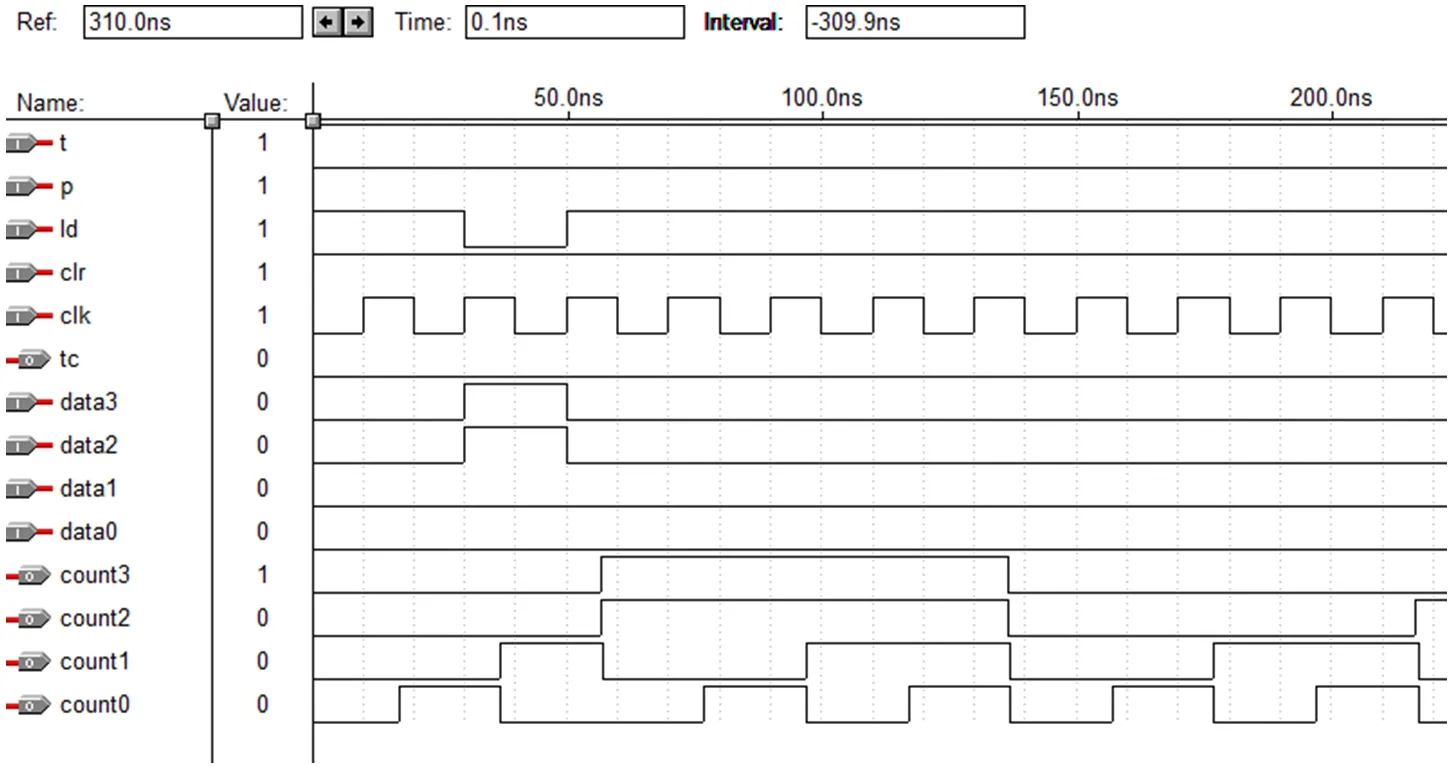

如图4所示,改变控制信号t的取值,当p和t不全为高电平时,电路输出保持不变。

图4 计数保持功能波形图Fig.4 Waveform of counting hold function

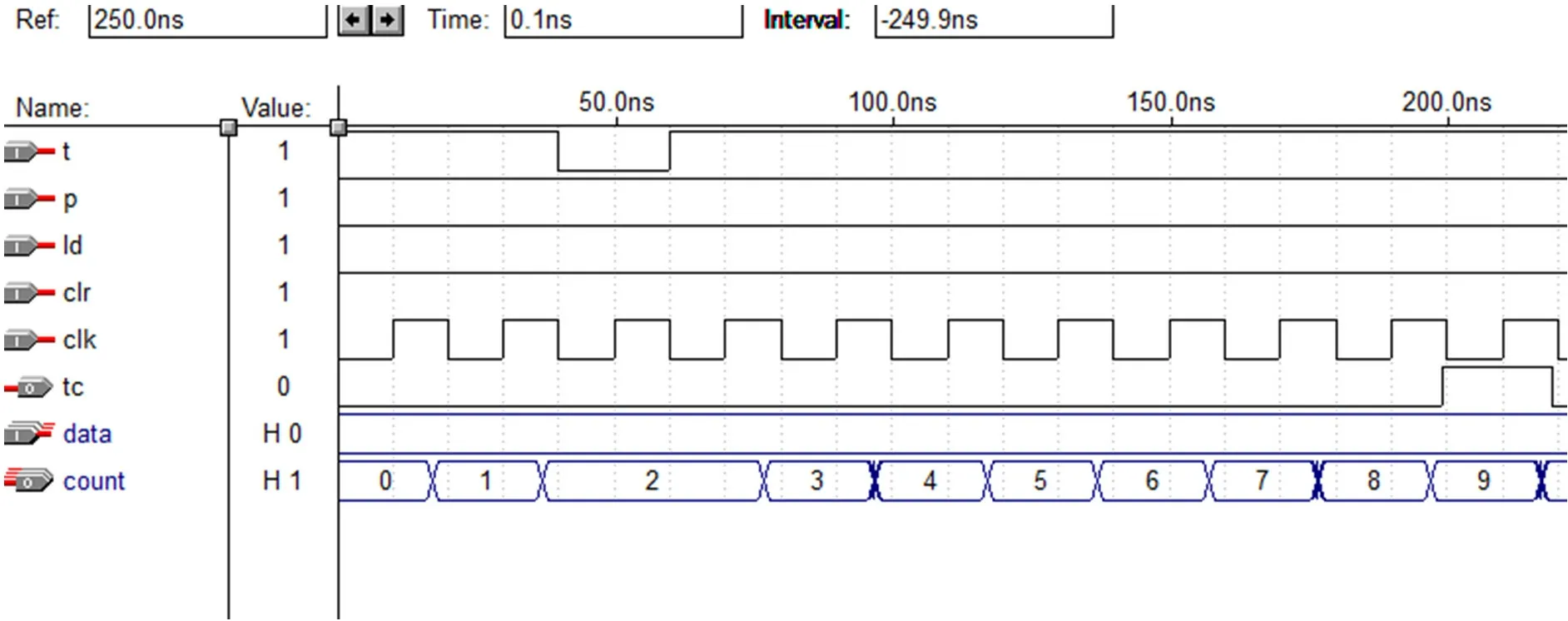

如图5所示,电路的复位端、置位端无效,且p和t均为高电平时,电路在上升沿的触发下,电路执行计数功能,每完成一个循环,TC端口给出一个相应的提示信号。

图5 计数功能波形图Fig.5 Waveform diagram of counting function

从验证结果中还可看出,电路的输出存在一定的延时,这是不可避免的。设计者可以通过不断的优化,降低延时对电路的影响。

6 结语

本文利用MAX plusII开发工具,设计了74LSl60 计数器电路,并进行波形仿真,对其相关功能进行逐一验证,结果表明达到设计要求。

引用

[1]顾斌,赵明忠,姜志鹏,等.数字电路EDA设计[M].西安:西安电子科技大学出版社,2004.

[2]魏欣,顾斌,姜志鹏.数字电路EDA设计(第三版)[M].西安:西安电子科技大学出版社,2016.

[3]黄建华.汽车电工电子技术[M].西安:西安电子科技大学出版社,2006.

[4]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2013.

[5]胡锦.数字电路与逻辑设计[M].北京:高等教育出版社,2011.

[6]乔琳君.基于74LS160的 N进制计数器仿真设计[J].电子设计工程,2013(12):191-193.