用于Si-PIN探测器的小尺寸电荷灵敏前置放大器的设计

张玲玲,何资星,郭凤丽

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

1 引言

在辐射检测系统中,核辐射探测器一直是探测技术应用的关键器件,自20世纪60年代起,半导体探测器作为核辐射探测器被重点研究[1],其中,Si-PIN探测器因具有制造工艺成熟、体积小、封装简单、工作电压低等特点,在射线测量中得到广泛应用[2-3],特别是在γ射线探测领域[4]。Si-PIN探测器的输出信号幅度较小,因此需要搭配前置放大电路对其信号进行放大。核辐射探测器的核心前置放大电路主要有电荷灵敏、电压灵敏、电流灵敏3类。由于在增益稳定性以及噪声性能上的优势,电荷灵敏前置放大电路在核辐射探测领域应用更广泛[5]。目前,国内外大部分低噪声电荷灵敏前置放大器的主运放电路由结型场效应晶体管(JFET)与高速运算芯片构成[6]。这样可同时利用JFET输入噪声低、跨导较高的特点与高速运算放大器增益高、带宽高的特点。为了满足小型便携式核辐射探测器的应用需求,本文直接采用带有N沟道JFET输入的高带宽、低噪声、双通道运放芯片AD8066,设计了一种小尺寸电荷灵敏前置放大器,应用于耗尽层厚度为300μm、灵敏面积为25 mm2的Si-PIN探测器。

2 前置放大器的设计原理

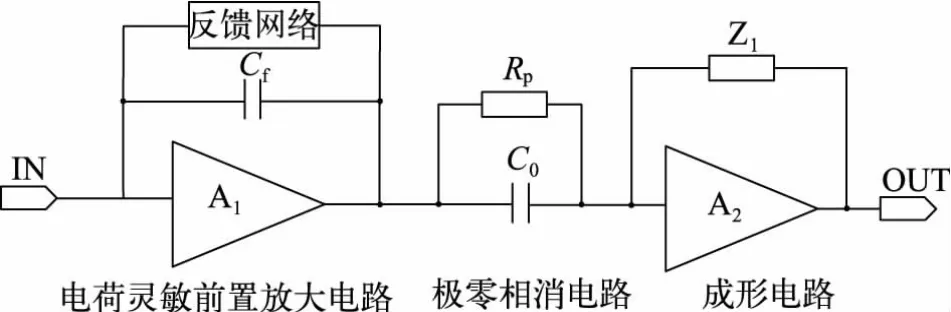

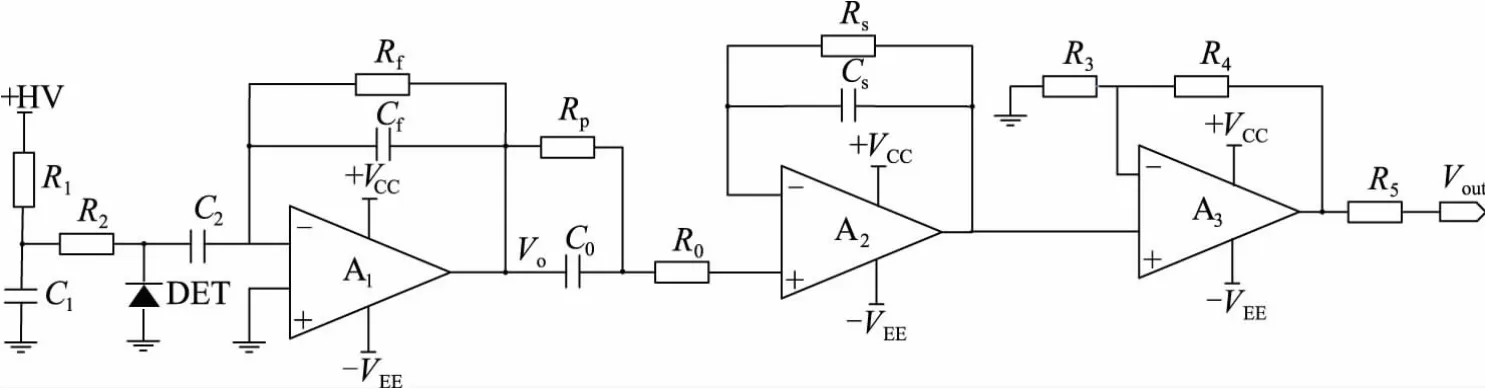

在核辐射检测系统中,前置放大器的主要功能是对辐射探测器的输出信号进行放大、滤波以及成形。前置放大器的原理如图1所示,其主要由电荷灵敏前置放大电路、极零相消电路以及成形电路组成。

图1 前置放大器的原理

2.1 电荷灵敏前置放大电路

电荷灵敏前置放大电路的原理见图1,其主要由核心运算放大芯片A1、积分电容Cf以及反馈网络组成。当放大芯片A1的增益A0很大时,输入电荷Qi基本积累在Cf上,输出电压V0可由式(1)表示:

考虑到Cf为常量,所以V0只与Qi有关,不受探测器的极间电容、放大器的输入电容的影响。同时,可以通过减小Cf来提高电路增益并降低噪声,但这将同时降低反馈深度,因此,设计电路的A0必须足够大。此外,随着电荷在Cf上的不断积累,电荷灵敏前置放大电路的输出电压V0将达到饱和。因此,为了防止输出电压饱和以及稳定反馈直流工作点,电路需要加入一个反馈网络以泄放反馈电容上的电荷[7]。

为了简化电路结构,稳定电路增益,本文采用电阻反馈作为电荷灵敏前放的反馈复位模块。在选择反馈电阻与反馈电容时,考虑到反馈电阻会产生分布电容与热噪声,为了提高信噪比,应尽量选择较大的反馈电阻和较小的反馈电容。但过大的反馈电阻又会使电路的输出电压达到饱和,降低系统整体的计数率上限。综合考虑高带宽、低噪声需求后,反馈电阻Rf值设置为200 MΩ,积分电容Cf设置为0.5 pF。

2.2 滤波成形电路

在辐射探测系统中,为了尽量降低前置放大器输出信号的噪声和干扰,在放大器中还需要加入滤波电路。同时,前置放大器输出信号的时间常数过大,导致输出波形的宽度较大,在探测较高的信号频率时,有可能因信号堆积而引起信号输出波形畸变。此外,辐射探测器所产生的电流脉冲宽度也会因入射粒子的射程和径迹位置不同而波动,因此,还需要加入成形电路[8]来减少输出波形的宽度,并统一输出波形的成形时间。

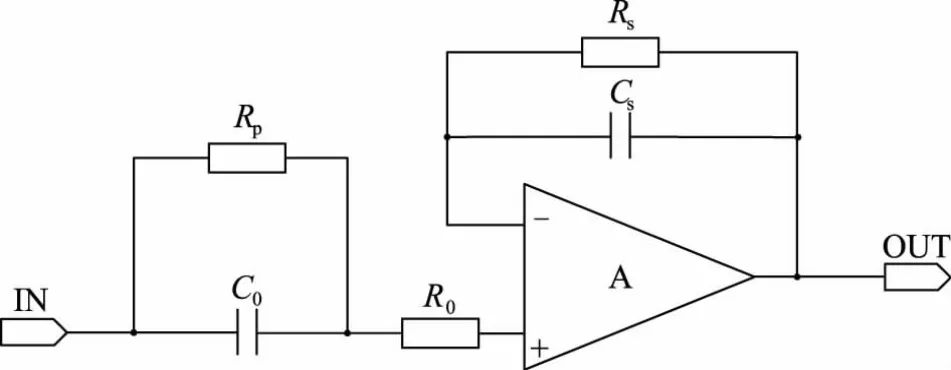

为了简化电路结构,本文采用了有源CR-RC滤波成形电路,并且添加了极零相消电路来消除输出信号的下冲。极零相消电路大多是在电容C0上并联电阻Rp来实现[9]。带有极零相消电路的滤波成形电路如图2所示。其中,电容C0与电阻Rp并联构成极零相消电路,电阻R0、电容Cs、电阻Rs以及运放芯片A构成有源CR-RC滤波成形电路。

图2 带有极零相消的有源CR-RC滤波成形电路

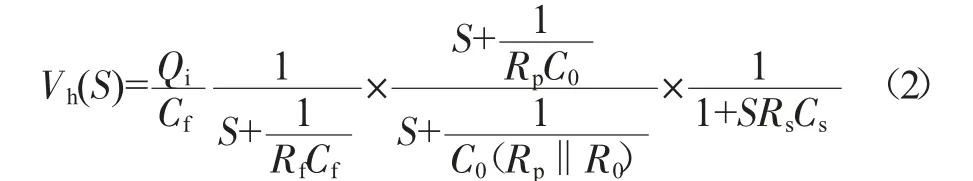

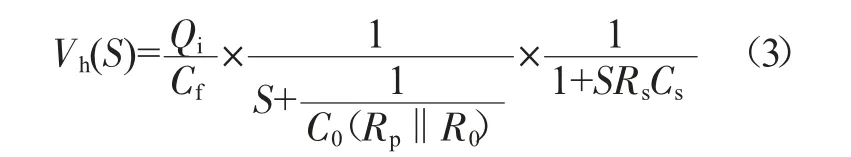

滤波成形电路的输出脉冲频域函数Vh(S)可由式(2)表示:

当RfCf=RpC0时,式(2)可转换为式(3):

由式(3)可知,电荷灵敏前置放大器的极点与极零相消电路的零点相互消除,衰减时间常数由RfCf变成C0(Rp‖R0),通过设置参数使得RfCf>>C0(Rp‖R0),因此,最终滤波成形电路的输出为单极性的指数衰减波形,消除了电荷灵敏前置放大器电路带来的下冲。在进行阻容网络设计时,为了获得最优信噪比以及较高的电路稳定性,还应使得C0(Rp‖R0)=RsCs。此外,考虑到滤波成形电路放大的增益有限,本文在滤波成形电路中还加入了2次放大电路,以此进一步增大探测器的电路增益。最终设计的用于Si-PIN探测器的电荷灵敏前置放大器电路如图3所示。

图3 电荷灵敏前置放大器电路

3 用于Si-PIN探测器的前置放大器设计

不同类型探测器的输出信号幅度和持续时间有差异,这些参数将影响前置放大器的放大增益以及频率带宽的设计,本文设计的电荷灵敏前置放大器主要用于Si-PIN探测器,因此有必要对Si-PIN探测器的输出信号进行分析,选择合适的运放芯片进行电路设计。

3.1 输入信号特性

电荷灵敏前置放大器的输入信号为Si-PIN探测器的输出信号,该信号可视为一个最大宽度为tw的微弱电流脉冲信号i,其所携带的电荷量Qi可表示为电荷量Qi与入射粒子的损耗能量成比例。因此,可以通过电荷量Qi的大小来表示入射粒子的能量。考虑到Si-PIN探测器主要用于γ射线探测,根据式(4)可以得到γ射线的输入能量为10 keV~2 MeV时,其所携带的电荷量Qi。

其中,E为输入信号的能量,we为产生电子-空穴对所需的平均电离能,e-为一个电子的电荷量。

考虑到硅半导体探测器的平均电离能为3.62 eV,因此,由式(4)可知,硅半导体探测器探测信号的输入电荷范围为0.5~88 fC。同时,电流信号脉宽tw主要由硅半导体探测器接收信号的电荷收集时间决定,即输入信号的上升时间。其中电子的电荷收集时间tn和空穴的电荷收集时间tp分别由式(5)(6)表示。

其中,x为吸收射线处距离n+电极的距离,w为探测器耗尽层厚度,μn为电子的迁移率,μp为空穴的迁移率,Eg为电场强度。

对于硅半导体探测器而言,当电场强度足够强时,电子-空穴对饱和后的速率为107cm2/(s·V)。而对于耗尽层厚度为300μm的Si-PIN探测器,可得到其饱和收集时间tmax为3 ns。考虑到探测系统的低功耗需求,在实际应用中,Si-PIN探测器的反向偏置电压偏低,导致实际收集时间t约在几十至几百纳秒内。以t为30 ns为例,在输入电荷Qi的范围内,通过式(7)可以得到在信号收集时间t内,Si-PIN探测器输出的平均电流ip,其范围为14.4 nA~4.27μA。

3.2 器件的选择

在选择电荷灵敏前置放大器电路的核心运放芯片时,通常要求运放芯片有足够的增益、较高的带宽以及尽量小的电流噪声。通过上面的分析可知,在对脉冲宽度为30 ns、脉冲幅度范围为14.4 nA~4.27μA的输入电流脉冲信号进行探测时,选择的放大器带宽应大于33 MHz,同时为了降低放大器电流噪声的干扰,选择运放的电流噪声应在pA量级。综合考虑后,本文采用高速、低噪声、双通道运放芯片AD8066构成前置放大电路,运放芯片AD8066在满足Si-PIN探测器高增益带宽、低噪声设计需求的同时还能有效简化电路结构。该芯片的输入端采用JFET,输入偏置电流仅为2 pA,输入失调电压仅为400μV,同时增益带宽达145 MHz。

在选择成形电路的核心运放芯片时,通常要求核心运放有足够大的增益,且电路带宽必须满足成形信号的要求,同时还需要有较大的运放动态范围,以便信号在变换过程中不失真,而AD8066的参数性能同样也满足设计要求。因此,利用AD8066的双路通道分别作为电荷灵敏前置放大与成形电路的核心运放芯片,在达到设计要求的同时进一步简化了电路结构。考虑到电路设计的一致性,同样选择AD8066作为二次放大电路的核心运放芯片。

4 仿真及结果

4.1 仿真参数设置

依据图3的电路原理图,利用高性能SPICE仿真软件LTspice绘制仿真原理图并进行瞬态仿真。将信号发生器产生的电流脉冲信号作为仿真信号源,通过设置信号源参数模拟241Am源59.5 keVγ射线与137Cs源662 keVγ射线输入信号来进行仿真。由前面的分析可知,Si-PIN探测器的输出信号可视为微弱的电流脉冲信号,室温工作下其饱和收集速率约为几十纳秒,以30 ns为例,电流脉冲宽度设置为30 ns,周期为100μs。同时结合式(4)(7),可以获得241Am 59.5 keVγ射线的仿真电流脉冲源的脉冲幅值为87 nA;同理,获得137Cs 662 keVγ射线仿真电流脉冲源的脉冲幅值为975.3 nA。

4.2 仿真结果

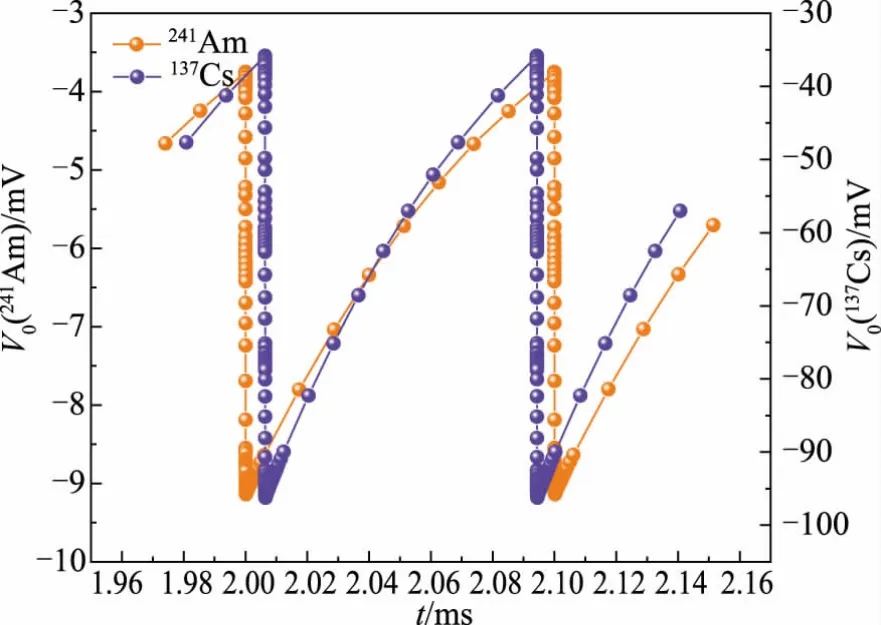

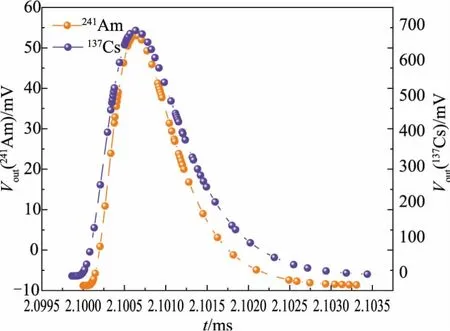

根据上述信号发生器的参数进行电路仿真,可分别获得电荷灵敏前置放大器的输出电压V0的仿真波形和成形电路的输出电压Vout的仿真波形,结果如图4与5所示。其中,图4为电荷灵敏前置放大器的输出电压V0的波形,图5为成形电路的输出电压Vout的波形。

图4 电荷灵敏前置放大器的输出电压波形

由图4可知,当分别模拟241Am源与137Cs源的γ射线输入时,电荷灵敏前置放大器的输出电压V0的变化量ΔV分别为-5.4 mV和-59.4 mV。同时,根据式(1)与式(4)可知,在Cf为0.5 pF时,通过理论计算,同样可以分别获得V0的变化量,分别为-5.3 mV与-58.5 mV。电路仿真在3%的误差范围内,仿真测量结果与理论计算结果基本一致。同时,由图5可知,它们的成形电路输出电压幅度分别为62.2 mV与693.9 mV,而波形成形时间约为2.5μs,输出增益达24 V/pF。

图5 成形电路的输出电压波形

5 试验测试结果

5.1 试验测试方案

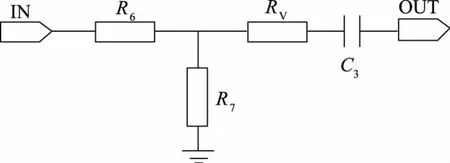

在进行探测器电路测试时,需要产生与Si-PIN探测器的输出信号相似的电流脉冲信号作为测试信号,并确保其所携带的电荷量Qi可被计算测量。考虑到电流脉冲信号无法直接产生,需要对信号进行转换,转换电路如图6所示。

图6 转换电路

图6中由脉冲发生器产生脉冲宽度为tw的电压脉冲信号Vtest,作为转换电路的输入信号,然后,通过精密电阻Rv将电压脉冲信号转换成电流脉冲信号。通常情况下,信号发生器产生的脉冲幅度下限为毫伏级,因此,采用电阻R6、R7进行分压来降低测试信号的脉冲幅度下限。测试信号所携带的电荷量Qi可由式(8)表示:

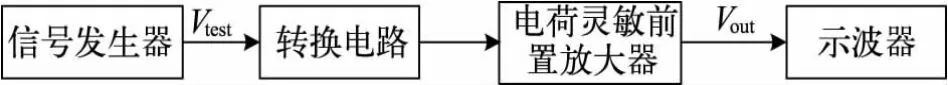

此外,为了避免Si-PIN探测器的漏电流造成信号堆积并减少探测器噪声的影响,前置放大电路的输入信号与测试信号通过电容C3以AC耦合方式进行连接。试验测试方案如图7所示,信号发生器产生的输出信号作为转换电路的输入信号,而转换电路的输出信号作为电荷灵敏前置放大器的输入信号。最后,电荷灵敏前置放大器的输出信号由示波器显示。在进行试验测试时,通过调节信号发生器的输出信号Vtest的电压脉冲幅度以及脉冲宽度参数来改变每个信号脉冲所携带的电荷量Qi,最后再使用示波器记录分析电荷灵敏前置放大器的输出信号Vout。

图7 试验测试方案

5.2 试验测试结果

5.2.1241Am源、137Cs源模拟测试

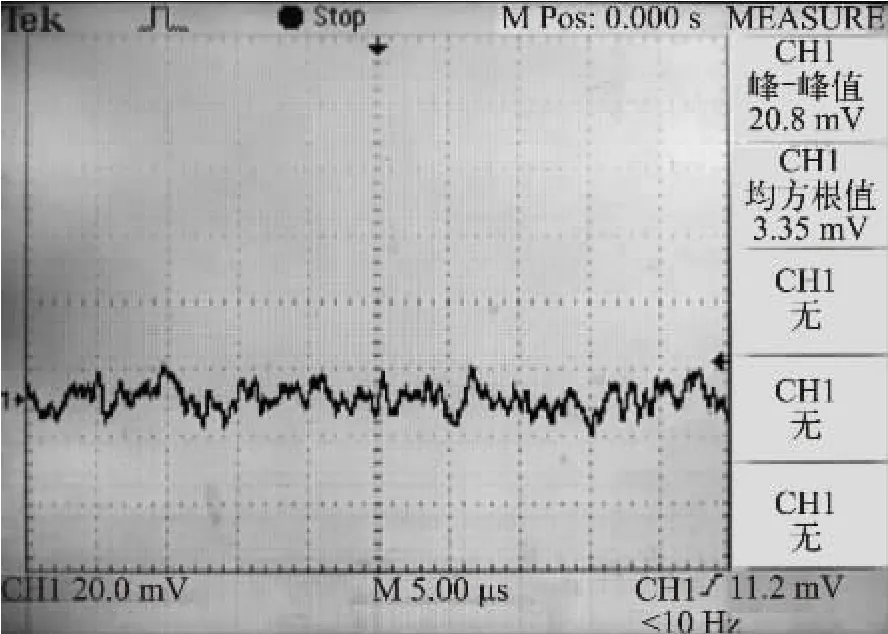

依据上述电路仿真原理以及实验测试方案来设置输入的电荷量Qi,分别模拟241Am源与137Cs源的γ射线信号输入进行测试,再使用示波器观察成形电路的输出电压Vout的波形。本底噪声输出波形如图8所示,测试241Am源和137Cs源的γ射线信号输入时,成形电路的输出波形如图9所示。

图8 本底噪声输出波形

由图8可知,在室温环境下,测试电路本底噪声的均方根约为3.35 mV,其电子学等效噪声电荷(ENC)约为0.15 fC。由图9可知,模拟测试241Am源和137Cs源的输出波形成形时间约为2.5μs,而它们的输出电压峰值分别为64 mV和696 mV,与仿真结果基本一致。将本次试验测试结果与实际241Am源[10]和137Cs源[11]的测试结果对比,发现本设计的电荷灵敏前置放大器能有效对241Am源和137Cs源γ射线进行探测,同时同类电荷灵敏前置放大器的成形时间为6μs[12],本设计的放大器波形成形时间仅为2.5μs,可探测更高计数率辐射环境下的γ射线。

图9 成形电路的输出波形

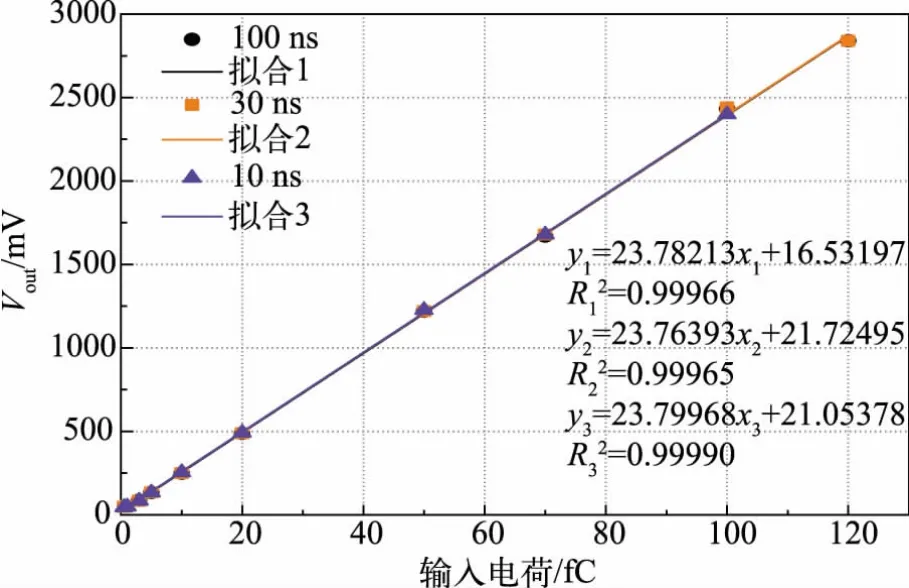

5.2.2 电路带宽测试

通过设置信号发生器的输出信号脉宽tw可实现对电路带宽的测试,考虑到使用的Si-PIN探测器的饱和收集时间约为30 ns,因此分别针对脉宽为100 ns、30 ns、10 ns的输入信号,在不同输入电荷量下进行测试。最终,在0.5~100 fC的输入电荷范围内,其测试结果如图10所示。

图10 100 ns、30 ns、10 ns脉宽线性拟合

图10中,在0.5~100 fC的输入电荷范围内,100 ns、30 ns、10 ns的测试脉宽信号表现出较高的线性拟合度,均达到0.999,且放大增益稳定,约为24 V/pC,与仿真结果基本一致。对比同类仪器的时间响应速度(40 ns)[13],本设计的电荷灵敏前置放大器的时间响应速度可达10 ns,满足Si-PIN探测器的应用需求。

6 结论

本文设计了一种小尺寸电荷灵敏前置放大器,该电路采用低噪声、高带宽、双通道的放大器芯片AD8066,简化了电路结构,减小了空间体积。经过电路仿真和241Am源、137Cs源的γ射线模拟测试,发现本设计的小尺寸电荷灵敏前置放大器能有效对241Am和137Cs源的γ射线进行探测,电子学等效噪声电荷约为0.15 fC,输出波形成形时间约为2.5μs。此外,经过电路带宽测试发现,该前置放大电路的时间响应速度可达10 ns,且在0.5~100 fC的输入电荷范围内,有较高的增益稳定性,具有良好的应用前景。