基于0.7 μm InP HBT工艺的10 GS/s宽带Σ-Δ模数转换器设计

张 翼,刘 坤,韩春林,王 洋,张有涛2,,6,李晓鹏,杨 磊,郭宇锋,2

(1. 南京邮电大学 集成电路科学与工程学院,江苏 南京 210023;2. 射频集成与微组装技术国家地方联合工程实验室,江苏 南京 210023;3. 微波毫米波单片集成和模块电路重点实验室,江苏 南京 210016;4. 东南大学 毫米波国家重点实验室,江苏 南京 210096;5. 南京工业职业技术大学,江苏 南京 210023;6. 南京国博电子股份有限公司,江苏 南京 210016)

0 引 言

超高速宽带模数转换器在宽带通信和雷达接收机中被广泛使用. 随着移动通信和光通信技术的迅速发展,信号处理的速度变得越来越快,同时也使得超高速(Ultra-High-Speed)模数转换器(Analog-to-Digital Converter,ADC)电路的市场需求变得更大. 例如,在移动数据需求不断增长的推动下,移动通信LTE Advanced(LTE-A)之类的标准已经被快速更新以支持更多用户,并提供更高的每用户带宽[1]. 因此,由宏基站(Base Station, BTS)支持的信号带宽预计将从35 MHz~100 MHz赫兹扩增至200 MHz. 因此,这也对模数转换器的带宽提出了更高的要求. 除了带宽和采样速度,模数转换器的精度也是系统性能的瓶颈.

从工艺角度,InP HBT工艺具有很多的优点[2-5],其高频性能好,电流密度大,功率密度高,驱动能力强,线性度好,InP HBT的击穿电压约为SiGe HBT的3倍,同时截止频率更高. 这对于超高速和大带宽的模数转换器设计非常有利,然而化合物工艺由于其集成密度的限制,无法实现大规模复杂数字电路.

从电路结构上来说,全并行ADC电路的工作速度在所有单通道ADC电路结构中是最快的. 然而,全并行ADC一般精度较低,不超过6位,否则电路规模和功耗将变得非常庞大从而不适合InP HBT工艺. Σ-ΔADC通过过采样和噪声整形两个关键技术,结合InP HBT工艺的优势,可以实现超高速宽带和中高精度的模数转换.

本文基于国内独立自主的0.7 μm InP HBT工艺,设计了一款超高速宽带Σ-Δ模数转换器,其在300 MHz的宽带内,信噪比(Signal-to-Noise Ratio, SNR)都大于42.6 dB,可以满足宽带通信和雷达接收机等的需求. 本文主要介绍了超高速宽带Σ-ΔADC系统架构,进行了关键单元电路设计及制版,并对系统进行了仿真分析.

1 Σ-ΔADC电路设计

1.1 Σ-ΔADC系统架构

与离散时间∑-ΔADC相比,连续时间∑-ΔADC不需要引入抗混叠过滤器,而是通过环路滤波器进行滤波. 此外,由于没有开关的操作且没有对建立时间的严格要求,因此连续时间∑-ΔADC能够以更高的速度工作. 然而,连续时间∑-Δ转换器会受到来自时钟抖动的双重影响,除了每个采样器中的抖动产生的噪声,在内部数模转换器(Digital-to-Analog Converter, DAC)中的时钟抖动也会在DAC中引入噪声. 由于InP HBT工艺具有高频性能好但集成度较差的特点,因此采用InP HBT工艺设计实现的∑-ΔADC一般都是采用连续时间的结构. 此外,由于内部DAC的非线性和噪声等非理想特性无法通过环路的噪声整形加以解决,因此内部DAC设计的要求更高,对其线性度的要求必须超过整体∑-ΔADC的要求. 因此,很多设计采用了单比特DAC,就是利用其天生线性的优点. 然而,单比特DAC也有自身精度比较低和量化噪声固定而随机性不够的缺点. 本文设计中要求采样时钟为10 GHz,最大输入信号带宽大于300 MHz,其过采样率(Over sampling rate, OSR)大约仅为16,通过过采样和噪声整形技术能够提升的精度有限. 常规设计中可以采用引入扰动或高阶调制的方法,然而,高阶调制需要参考系统稳定性的问题,并且以上的方法都会使系统结构变得较为复杂,化合物工艺由于其集成密度的限制,不适合采用上述方法. 因此,本文方案中设计了高线性度的2 bit 电流舵DAC[6],从仿真结果来看,该DAC的线性度性能足以满足∑-ΔADC系统的要求. 图1 为本文设计采用的∑-ΔADC系统框图.

由图1 可以看出,系统包括了两级环路滤波器,一个2 bit ADC和一个2 bit DAC. 主要的噪声源是第一级滤波器的输入参考噪声和DAC的输出噪声. DAC噪声包括晶体管产生的噪声电流,以及时钟和数据抖动引起的噪声. 为了减轻数据抖动的影响,ADC中的比较器由主从结构[7-8]组成,其中输出与采样时钟同步良好. 然而,主从比较器的输出延迟了时钟周期的一半,该延迟会在Δ-∑反馈路径上引入额外的环路延迟. 因此,必须使用补偿方法纠正延迟引起的调制器的不稳定[9]. 此外,在系统输出加入了一个2 bit DAC和输出缓冲电路,该DAC与系统中的DAC完全相同,该部分构成了测试辅助电路,可以降低系统测试的难度.

调制器的环路传输函数可用-HqH2(1+H1)来表示,其中,H1,H2和Hq分别是第一、第二环路滤波器和量化器的传递函数.前面的表达式意味着,如果H2中存在零点,则环路传输函数将继承相同的零点. 因此,本文在第二个滤波器中添加了一个零点,具体见下节说明.

1.2 关键单元电路设计

1.2.1 环路滤波器设计

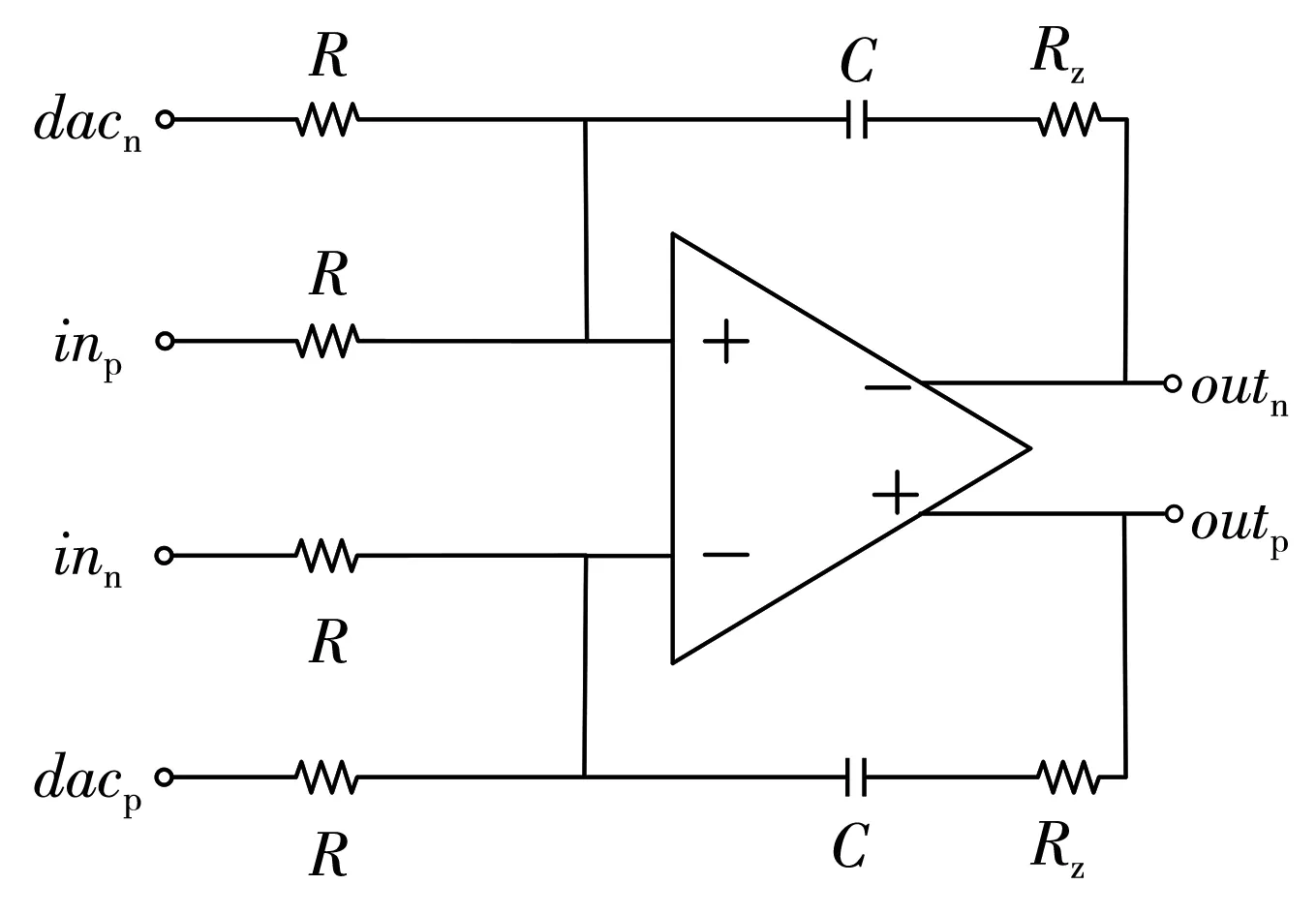

每级环路滤波器由一个全差分运算放大器组成,该放大器构造成一个求和积分器,如图2 所示. 图2 中电阻RZ将零点引入传递函数,该电阻仅存在于第二个滤波器中. 正如1.1节介绍的在第二个滤波器中添加了一个零点,该零点的引入是为了补偿环路增益.

图2 环路滤波器结构示意图Fig.2 Schematic diagram of loop filter

运算放大器设计中的关键参数是低频增益和线性度. 高的低频增益改善了低频下的噪声整形,减少了不希望出现的死区非线性现象[10]. 第一个积分器中运算放大器的线性度对∑-ΔADC的线性性能至关重要,因为这种失真会直接返回到ADC的输入端,而第二个积分器的线性度要求则会低一些.

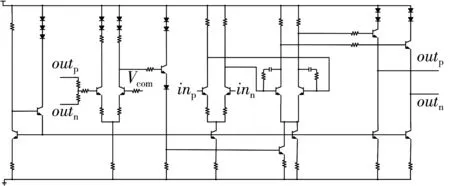

运放电路原理图如图3 所示. 该电路采用了密勒补偿的两个增益级,输出级采用共集电极输出. 第一级由一个射极电阻退化,以提高放大器的线性度. 由于第二个积分器的线性度要求不高,因此,第二级未采用射极退化电阻. 为了避免启动过程中的闩锁效应问题,共模反馈电路只控制第二增益级电流的一半,而另一半是固定电流.

图3 运算放大器电路图Fig.3 Circuit diagram of operational amplifier

1.2.2 2 bit模数转换器设计

图1 中的2 bit ADC电路结构如图4 所示.VREF处的电压控制Flash ADC的动态范围. 这三个比较器都包括一个前置放大器和主从锁存器.

图4 2 bit ADC电路图Fig.4 Circuit diagram of 2 bit ADC

前置放大器提高了灵敏度并且减轻了时钟回踢的影响. 如图5 所示,它包括一个共射共基级和两个射级跟随电路. 前置放大器有一个独立的偏置电路,以防止时钟信号通过电流源干扰偏置.

图5 比较器的预放大器电路图Fig.5 Circuit diagram of pre-amplifier for the comparator

本文设计的比较器电路的主从锁存器采用标准的ECL拓扑. 时钟回踢效应可以通过时钟切换对的退化来降低. 锁存器对包括射级跟随器,以增加其速度并中和密勒效应. 此外,设计中还通过引入峰化电感提高主锁存器的速度. 完整的主从锁存器电路图如图6 所示.

图6 比较器的主从锁存器电路图Fig.6 Circuit diagram of master-slave latch of comparator

1.2.3 2 bit数模转换器电路设计

本文设计中,2 bit DAC采用电阻负载的标准差动电流舵结构,其电路图如图7 所示.

图7 2 bit DAC电路图Fig.7 Circuit diagram of 2 bit DAC

每个输入位(D0~D2)在差分对的输出之间切换电流. DAC的数字输入由flash ADC以温度计编码的结果作为其输入. 因此,开关电流源(I0~I2)是相同的. 形成电流开关的差分对加入射极退化电阻,以减少由急剧输入瞬变引起的输出过冲. 构成电流源的电阻和晶体管以一种每组器件由 3个平行器件组成的方式变换. DAC的线性度是本设计中的一个关键. 本文在电路设计上采用了差分电流舵结构;形成电流开关的差分对进行了射极退化设计,以减少由输入的急剧瞬变引起的输出过冲. 版图设计上差分对采用了共中心方式实现对称;为了增强器件的均匀性,在电流源晶体管周围设计了两排伪晶体管以增强器件的一致性.

2 仿真结果

基于第1节提出的系统架构和关键单元电路来进行版图设计,本文的Σ-ΔADC电路基于0.7 μm InP HBT工艺设计实现,该工艺的ft>250 GHz,fmax>280 GHz. 图8 是Σ-ΔADC电路的版图,版图尺寸为1.58 mm×1.82 mm.

图8 Σ-ΔADC电路的版图Fig.8 Layout of Σ-ΔADC

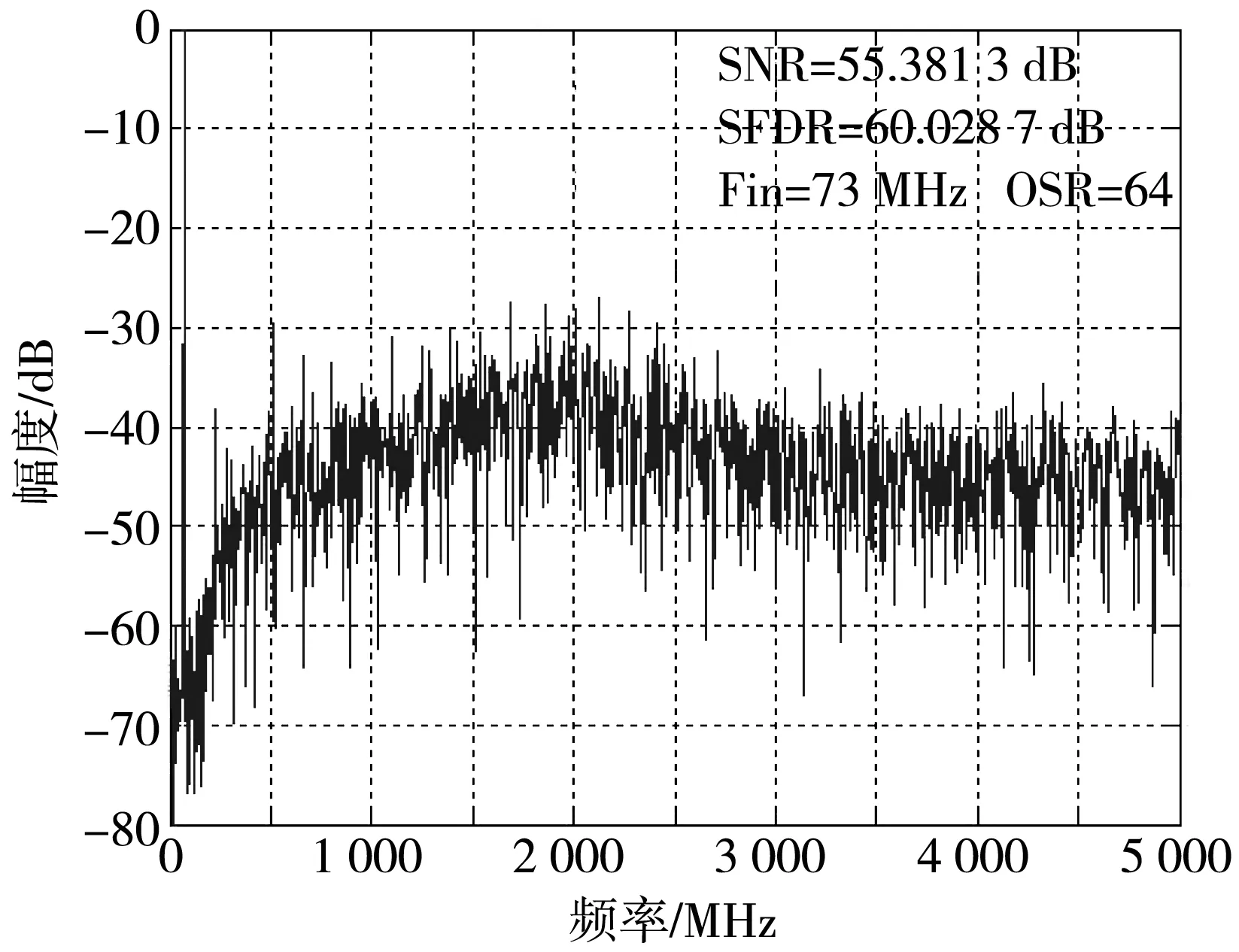

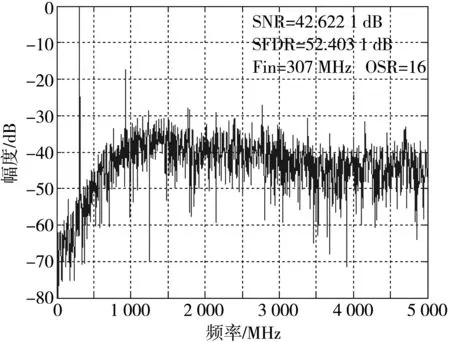

仿真中设置时钟信号频率为10 GHz,输入差分信号摆幅为1 000 mV,不同频率输入信号下的输出信号的频谱如图9~图11 所示.

由图9~图11 可以看出:当输入信号频率为73 MHz,OSR约为64时,该ADC的SFDR大于60 dB,SNR大于55.3 dB;当输入信号频率为151 MHz,OSR约为32时,该ADC的SFDR大于56.5 dB,SNR大于49.9 dB;当输入信号频率为307 MHz,OSR约为16时,该ADC的SFDR大于52.4 dB,SNR大于42.6 dB.

本文设计的结果与相关文献结果的对比如表1 所示. 由表1 可以看出,由于InP HBT工艺设计时特征尺寸较大,对光刻机等半导体设备要求不高. 本文设计的Σ-Δ模数转换器的采样速度和带宽均超过其他的设计,性能介于相关文献所设计的ADC的中间.

图9 输入73 MHz, OSR为64时输出信号的频谱Fig.9 Output signal spectrum at input signal of 73 MHz and OSR of 646

图10 输入151 MHz, OSR为32时输出信号的频谱Fig.10 Output signal spectrum at input signal of 151 MHz and OSR of 326

图11 输入307 MHz, OSR为16时输出信号的频谱Fig.11 Output signal spectrum at input signal of 307 MHz and OSR of 16

表1 Σ-ΔADC性能对比Tab.1 Σ-ΔADC performance comparison

3 结 论

本文提出了一种基于国内自主可控0.7 μm InP HBT工艺,时钟采样率为10 GS/s,最大输入信号带宽超过300 MHz的超高速宽带Σ-Δ模数转换器电路的设计和仿真. 结构上采用了二阶2 bit 量化,可充分发挥InP HBT工艺的特点. 后仿真结果表明:本文所设计的Σ-ΔADC在5 V供电电压下,当输入信号幅度为1 000 mV,频率为307 MHz 时,ADC的无杂散动态范围(SFDR)和信号与噪声及谐波的失真比(SNDR)分别为 52.4 dB 和42.6 dB,功耗为1.3 W,可以应用在宽带通信和雷达接收机中.