自供电式同步翻转电荷提取电路的优化设计

邱泓程,隋丽,王东亚

(1.北京理工大学 机电工程与控制国家级重点实验室,北京 100081;2.西北工业集团有限公司,西安 710043)

现代引信电子化、智能化以及小型化的发展趋势对引信电源的设计也提出了相应的需求,传统化学电源因体积大、需频繁更换和回收难等缺点,已无法满足引信微型化的要求[1-2]。从环境中收集能量转换为电能是解决上述问题的方法之一。其中,压电振动能量俘获技术是具有广阔前景的方式之一。压电材料作为新型能源,具有体积小、寿命长、能量密度高等诸多优点,不仅能够满足现代引信电源小型化的需求,还可以为引信安保系统提供基于环境激励的解保信号[3-5]。

压电换能器(Piezoelectric Transducers,PZT)在周期性往复振动状态下时,输出的是交流电压,而普通电子设备一般需要直流供电。因此,需要在PZT和负载之间设计一种接口电路,来实现AC-DC 转换,并保证接口电路的能量俘获效率维持在较高水平[6-7]。其中最简单、最经典的接口电路是由4 个二极管组成的全桥整流电路(Full Bridge Rectifier Circuit,FBR),但其输出功率对负载阻抗变化敏感,并且由于PZT 上寄生电容不断充放电的影响,使得FBR 的能量俘获效率较低[8-9]。

研究人员提出了多种非线性能量俘获技术来提高对PZT 的能量俘获效率,主要包括同步开关电感(Synchronized Switch Harvesting on Inductor,SSHI)技术[10-18]和同步电荷提取(Synchronous Electric Charge Extraction,SECE)技术[19-23]等。相较于SSHI 电路,SECE 电路具有输出功率不受负载影响的特点[19],在任何负载情况下的输出功率都是最优输出功率。Lallart 等[24-25]在SECE 技术基础上,提出了同步翻转电荷提取(Synchronous Inversion and Charge Extraction Circuit,SICE)电路,进一步提高了接口电路的能量俘获效率。目前,大部分基于SICE 技术的派生电路都需要外部辅助电路来控制开关通断,控制策略繁琐,电路结构复杂。基于此,本文提出了一种自供电式的优化同步翻转电荷提取电路(Self-Powered Optimized Synchronous Inversion and Charge Extraction Circuit,SP-OSICE),该电路优化了SICE(n=1)开关控制策略,通过自供电设计,使得SP-OSICE 电路能自动检测PZT 两端电压的峰值,在电压正峰值时刻实现电压翻转,在电压负峰值时刻实现电荷提取,消除了对外接辅助控制电路的依赖,且该电路无需整流桥,降低了接口电路的能量损耗。

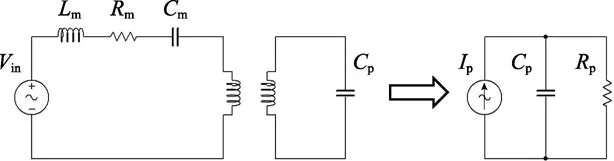

1 压电等效模型

压电换能器可利用压电效应将外界振动能转换为电能。典型的压电换能器装置通常为单自由度悬臂梁结构[15],其机电耦合等效模型如图1 所示。其中,Lm为机械质量;Rm为机械阻尼;Cm为机械强度。在正弦谐振情况下,压电换能器可近似等效为交流电流源Ip、寄生电容Cp和寄生电阻Rp并联的电路模型[15,23]。

图1 压电等效模型Fig.1 Equivalent model of piezoelectric energy harvester

2 经典接口电路分析

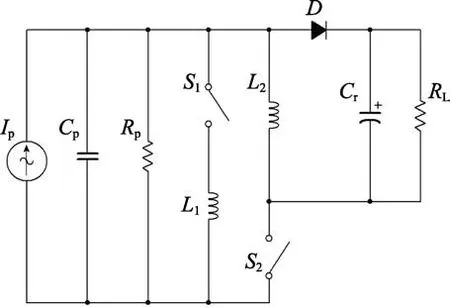

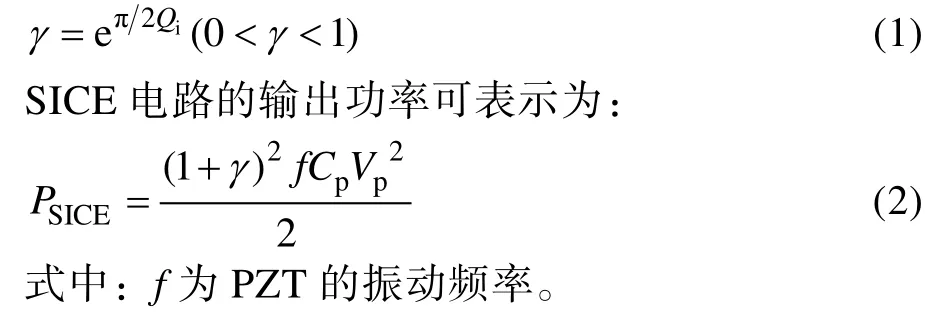

2.1 同步翻转电荷提取电路(SICE)

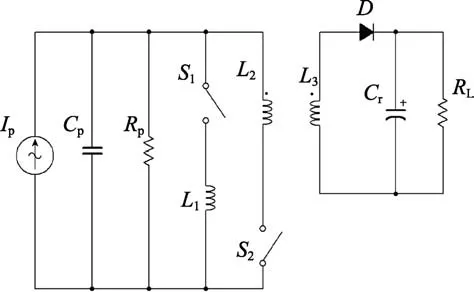

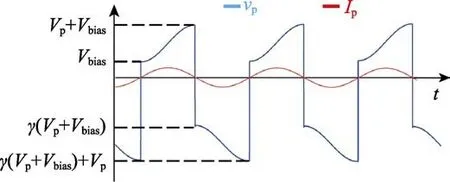

SECE 电路具有输出功率与负载大小无关的特点,且任意负载情况下的输出功率都是FBR 最大输出功率的4 倍。SICE 与SECE 电路不同的是增加了一个翻转电感L1,在电荷提取之前,先对PZT 两端电压进行翻转来提高PZT 的开路电压,以此提高接口电路对PZT 的能量提取效率。在文献[24-25]的基础上,本文给出了n=1 情况下同步翻转电荷提取电路的原理,如图2 所示。同步翻转电荷提取电路的电压波形如图3 所示。SICE 电路的工作原理如下:在电压正峰值时刻,开关S1闭合,Cp、S1和L1形成LC振荡回路,经1/2 个振荡周期后,S1断开,PZT 两端电压完成翻转。PZT 两端电压继续增大,在电压负峰值时刻,开关S2闭合,Cp、S2和L2形成LC 振荡回路,经1/4 个振荡周期后,S2断开,此时Cp上的电荷全部提取完毕,L2上的电流达到最大值,此后L2上的电流经二极管D缓慢流向滤波电容及负载。

图2 SICE 电路原理(n=1)Fig.2 Schematic of the SICE interface(n=1)

图3 SICE 电路电压与电流波形Fig.3 Voltage and current waveform of the SICE circuit

定义Qi为电压翻转电路的品质因数,则电压翻转系数γ可以表示为:

2.2 优化同步翻转电荷提取电路(OSICE)

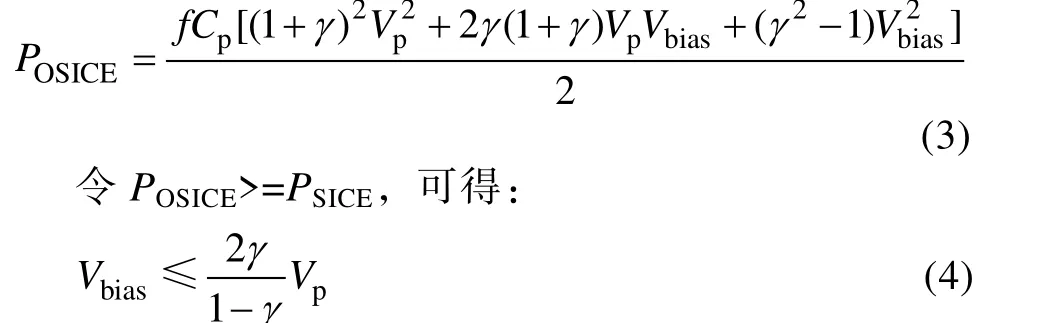

为简化SICE 开关控制策略,进一步提高接口电路输出功率,提出了OSICE 电路。OSICE 电路的原理如图4 所示,OSICE 电路的电压波形如图5 所示。与SICE 电路不同的是,OSICE 电路利用由2 个互感线圈L2、L3组成的变压器代替单个电感来完成能量从PZT 到负载的传递,L2、L3的电感比值为1∶1。OSICE电路的工作原理如下:在电压正峰值时刻,OSICE电路中的开关动作与SECE 电路相似,开关S1闭合,Cp、S1和L1形成LC 振荡回路,经1/2 个振荡周期后,S1断开,PZT 两端电压完成翻转,此后PZT 两端电压继续增大。在电压负峰值时刻,开关S2闭合,Cp、S2和L2形成LC 振荡回路,PZT 两端电压迅速上升。当PZT 两端电压上升到VD+VR时,L3上产生感应电流,储存在Cp上的电能开始流向滤波电容和负载,直至L3上的感应电流降为0。

图4 OSICE 电路原理Fig.4 Schematic of the OSICE interface

图5 OSICE 电压与电流波形Fig.5 Voltage and current waveform of the OSICE circuit

相较于SICE 电路,OSICE 中的开关S2在电荷提取过程中持续保持导通,直至PZT 两端电压上升为VD+VR。正是这个动作赋予了PZT 一个值为VD+VR的直流电压偏置,增大了PZT 两端开路电压。

若不考虑互感变压器的能量损耗,OSICE 电路的输出功率可表示为:

由此可见,提高电路品质因数、使用容值较大的滤波电容都利于改善电路性能,理论上可使得OSICE电路输出功率高于SICE 电路。实际上,只要合理选择电子元件,可保证γ的取值范围为0.6~0.9,而Vbias≤Vp,式(4)条件更容易满足。

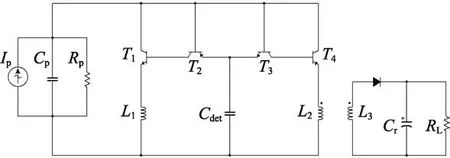

3 SP-OSICE 电路设计及工作原理分析

因采用自供电开关能使OSICE 电路的实用性更大,本文提出了SP-OSICE 电路,电路结构如图6 所示。该电路主要包括正/负峰值电压检测电路、互感变压器(L1、L2组成)、二极管D、滤波电容Cr及负载RL组成。正峰值电压检测电路由晶体管T1、T3、电感L1和检测电容Cdet构成,负峰值电压检测电路由晶体管T2、T4、电感L2和检测电容Cdet构成。SPOSICE 电路主要分为4 个工作阶段,下面将结合SPOSICE 电路两端电压波形对其工作原理进行详细说明。

图6 SP-OSICE 电路Fig.6 SP-OSICE circuit

3.1 正半周期自然充电阶段

等效电流源Ip给寄生电容Cp充电,PZT 两端电压逐渐上升。当Vp大于晶体管T2的Vbe时,T2的基射结导通。由于Cp与Cdet并联,Ip同时给Cp与Cdet充电,如图7a 所示。由于晶体管T4的基射结电压反偏,T4处于断开状态。电容Cp、Cdet两端电压均达到最大值后(分别为Vpmax,Vpmax-Vbe),电路进入下个工作阶段。

3.2 正半周期电流反向阶段

如图7b 所示,当正半周期自然充电阶段结束后,电流源Ip开始对Cp反向充电,Cp两端电压逐渐减小。由于T1基射结阈值电压和T2反向截止的缘故,Cdet上电压保持不变。当Vp下降至Vp-2Vbe时,T1导通,电路进入电压翻转阶段。

图7 SP-OSICE 电路工作原理Fig.7 Working princIple of the SP-OSICE circuit: a) positive half cycle natural charging stage; b) positive half cycle current reverse phase; c) voltage reversal phase; d) negative half cycle natural charging stage; e) negative half cycle current reverse phase;f) charge extraction stage

3.3 电压翻转阶段

T1导通促使T3导通,因此,Cp、T3和L1形成LC振荡回路,电路工作状态如图7c 所示。由于T3集射结的反向截止作用,经1/2 个LC 振荡周期后,T3断开,Cp和Cdet两端电压均完成翻转。

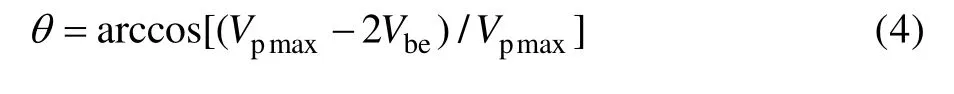

可以看到,开关T3的动作时刻并不与PZT 两端电压峰值时刻完全重合,两者存在一定的相位差,该相位差可表示为:

3.4 负半周期自然充电阶段

等效电流源Ip对Cp反向充电,Vp继续降低。当Cp与Cdet电压差达到晶体管T1基射结导通电压时,T1基射结导通,Ip同时对Cp和Cdet进行反向充电,直至Vp达到负峰值。电路工作状态如图7d 所示。

3.5 负半周期电流反向阶段

在电压负峰值时刻,Ip再次反向,Cp两端电压逐渐升高。由于晶体管T2存在阈值电压,T1反向截止,Cp两端电压保持不变。当Cp两端电压高于Cdet两端电压,且两者之差达到Vbe时,T2导通,促使T4导通,电路进入电荷提取阶段,如图7e 所示。

3.6 电荷提取阶段

T4导通后,Cp、T4和L2形成LC 振荡回路,Cp上储存的电能逐渐转换为L2上的磁能,Cp两端电压迅速上升。当Cp两端电压达到VD+VR时,电感L3上的电压大于VD+VR,电感L3上出现感应电流,感应电流通过二极管D向滤波电容Cr和负载RL流动,直至电流下降为0,至此完成了1 个振动周期的能量提取过程,如图7f 所示。

4 电路仿真分析

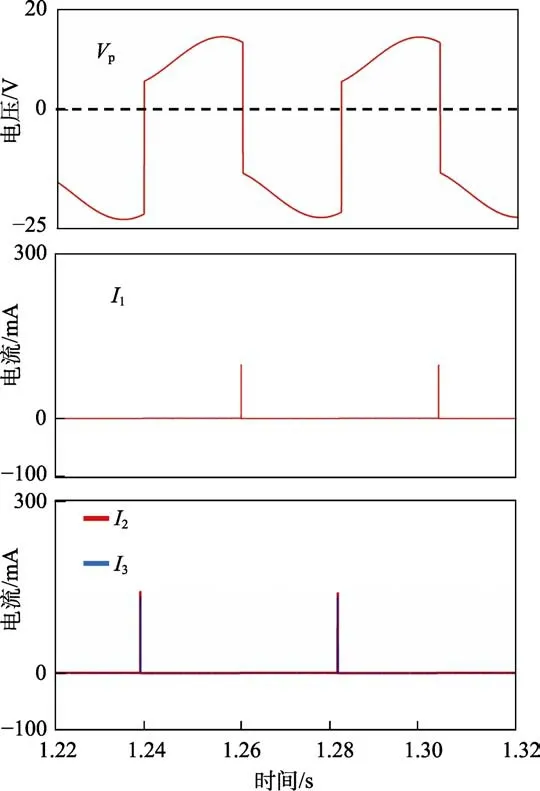

采用Multisim 软件对SP-OSICE 电路进行仿真分析。当PZT 连接SP-OSICE 电路后,达到稳态时的电压波形与各个电感电流波形如图 8 所示。由于SP-OSICE 电路只会在PZT 电压峰值处进行电压翻转或电荷提取操作,所以只有在电压达到峰值时刻,晶体管T3(T4)才能导通,LC 振荡回路建立,电感L1(L2、L3)上才会产生相应的感应电流。由图9 可见,在PZT 两端电压的正峰值时刻,L1上产生脉冲电流,PZT 两端电压完成了翻转;在PZT 两端电压的负峰值时刻,L2上产生脉冲电流。当vp上升至VD+VR时,I2迅速下降为0,此时L3上产生感应电流,缓慢将能量传递至滤波电容及负载。图8、图9 所展示的电压和电流波形很好地验证了对SP-OSICE 电路工作原理的分析。

图8 SP-SICE 电路电压和电流仿真波形Fig.8 Voltage and current simulation waveform of the SP-OSICE circuit

图9 电压与电流波形放大Fig.9 Enlarged voltage and current waveform

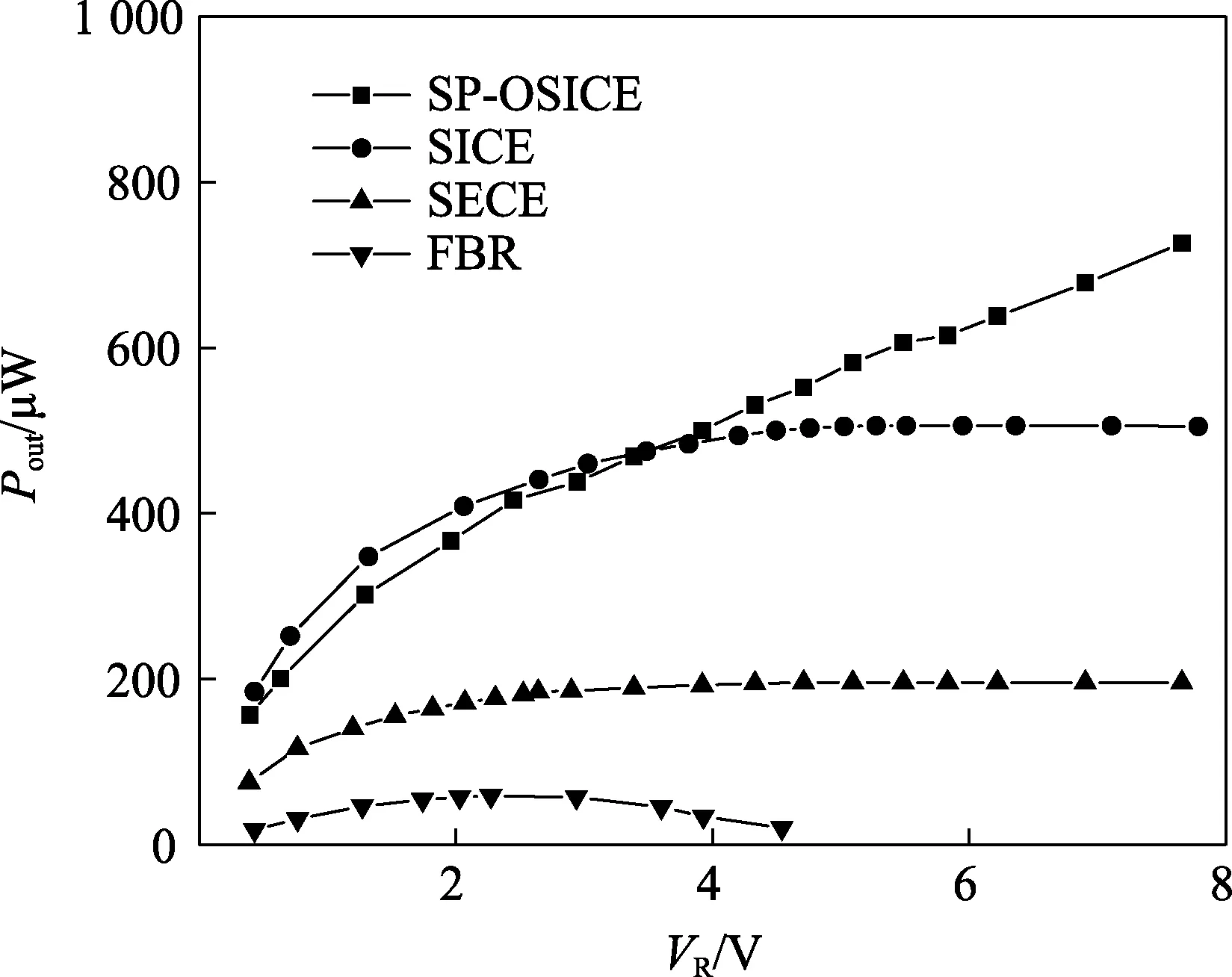

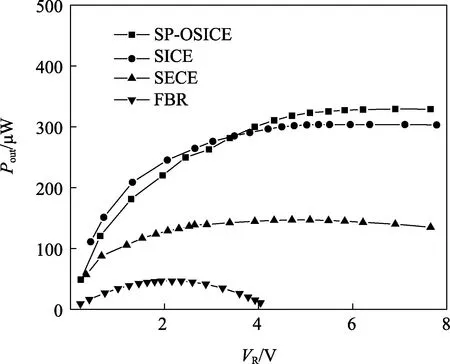

FBR、SECE、SICE 和SP-OSICE 在相同激励下(Voc=6V)的输出功率–负载电压曲线如图10 所示。在低负载电压区,各个接口电路的输出功率均较低。这是因为PZT 两端电压小,电路中二极管、晶体管等元件产生的压降,导致接口电路的能量损耗占比较高,接口电路能量俘获效率较低。随着负载电压的不断增大,SECE 和SICE 电路均展现出负载不相关性,而SP-OSICE 电路的输出功率逐渐增大。当负载电压小于3.5 V 时,SP-OSICE 电路的输出功率略低于SICE 电路。这是因为此时PZT 开路电压低,由晶体管开关电压所造成的相位延迟大,SP-OSICE 俘能效率较低。当负载电压大于3.5 V 时,SP-OSICE 电路的输出功率超过了SICE 电路,SECE 和SICE 电路的输出功率分别达到了FBR 电路的4 倍和8 倍,仿真结果验证了SP-OSICE 电路在压电能量俘获方面的高效性。

图10 仿真4 种接口电路输出功率随负载电压变化曲线Fig.10 Simulated output power versus VR of the four interface circuits

5 实验验证

为验证上述理论及仿真结果,搭建压电能量俘获实验平台对SP-OSICE 电路进行实物验证。实验系统主要包括信号发生器、功率放大器、激振器、示波器、基于悬臂梁结构的压电换能器以及SP-OSICE 能量俘获电路。

在信号发生器上设置正弦信号的振幅和频率,经功率放大器增强后,作用于激振器。压电换能器装置采用单自由度悬臂梁结构,其一端固定在激振器上,另一端固定上一块金属质量块作为自由端,改变金属质量块的质量,可调节PZT 的谐振频率,还可以起到增大PZT 自由端位移的作用。缓慢调节正弦信号的频率,使PZT 工作在谐振频率附近,此时PZT 初始开路电压达到最大值。

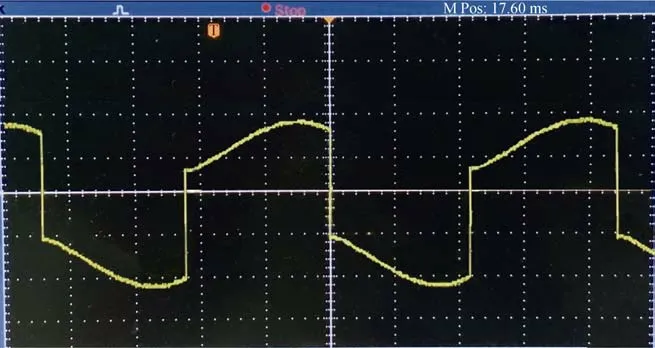

实测电路中PZT 两端开路电压波形如图11 所示。每个能量俘获周期都以正向自然充电阶段作为起始时刻,电压翻转时刻并不与电压正峰值时刻完全吻合,而是存在一定的相位延迟。由于振荡回路的品质因数问题,在翻转过程中,电流流经二极管、三极管等器件时,会产生能量损耗。然后PZT 开路电压持续下降,在电压负峰值时刻,经过短暂延迟后,电压迅速上升至VD+VR,储存在Cp上的能量流向了滤波电容及负载。

图11 SP-OSICE 实测电压开路波形Fig.11 Experimental voltage waveform of the SP-OSICE circuit

SP-OSICE 电路输出功率的仿真和实测结果对比如图12 所示。可以看到,SP-OSICE 电路的实际输出功率低于仿真输出功率,但输出功率随负载电压的变化趋势与仿真结果基本一致。这是因为实际电路中晶体管导通电压和电感寄生电阻的存在,进一步降低了振荡回路的品质因数,而且仿真采用的是理想互感变压器,实际上L2、L3并不能做到完全耦合,因此在能量传递过程中不可避免会产生能量损耗。

图12 SP-OSICE 电路仿真与实测输出功率随负载电压变化曲线Fig.12 Simulated and experimental output power versus VR of the SP-OSICE circuit

为验证本文所设计的SP-OSICE 具有较高的能量俘获效率,在PZT 初始开路电压为6 V 的情况下,测得了FBR、SECE、SP-OSICE 电路的输出功率–负载曲线,如图13 所示。可见,SECE 电路的输出功率是FBR 电路的3 倍,而SP-OSICE 电路的输出功率可达到FBR 电路的6 倍以上。整体实验结果与仿真结果基本吻合,验证了SP-OSICE 电路的有效性。

图13 实测4 种接口电路输出功率随负载电压变化曲线Fig.13 Experimental output power versus VRof the four interface circuits

6 结语

本文基于同步翻转电荷提取技术,提出了SP-OSICE 压电能量俘获电路。该电路优化了SICE电路中的开关控制策略,无需整流桥结构,提高了接口电路的输出功率。整体电路采用自供电设计,无需外部辅助电路控制晶体管通断,降低了电路结构的复杂性。仿真和实验结果均验证了 SP-OSICE电路的优势。