DSFP 在数据中心交换机TOR 中的应用

刘刚

(华勤技术股份有限公司,上海 201203)

过去一段时间内数据中心网络和服务器主要的接入是通过25 G 和100 G 的网络,涉及到的最多的接口是SFP28 和QSFP28。这两种接口使用的编码方式是28 Gbps NRZ。随着大数据、分布式存储、AI、5G 等高速业务的飞速发展,数据中心服务器和网络规模急剧增长,过去的25 G 和100 G 接口网络已经不能满足当前大数据业务的增长,TOR(Top of Rack)交换机的下行速率已经由过去的25 G 向100 G 甚至200 G 转变了。同时各大交换芯片厂商自2018 年后开始陆续推出支持56 G-PAM4 的高速Serdes 交换ASIC。这进一步推动了数据中心的交换速率和带宽往更高的400 G 方向发展。100 G QSFP28 接口与支持PAM4 的交换芯片因速率不同不能直接匹配。在TOR 从NRZ 向PAM4 升级的过程中有两条路径可以走,一条是从QSFP28升级到QSFP56。另一条就是通常提到的SFP-DD 和DSFP 即下一代100 G 接口。SFP-DD 和DSFP 是两种不同的接口形式,面向的用户有所不同。DSFP 的接口在国内部分互联网企业的数据中心有使用,但是关于DSFP 的应用在各网络及期刊杂志上却鲜有介绍,鉴于此,根据实际项目产品设计的经验介绍DSFP 在数据中心特别是TOR 交换机中的应用,以作交流推广。

1 DSFP 接口介绍

作为下一代100 G的封装形式之一,DSFP在2018年由双小型可插拔多源协议组(Dual Small Form-Factor Pluggable Multi-Source Agreement,DSFP MSA)推出并发布了其1.0规范。该规范定义了DSFP的I/O管脚,电气参数和信号、电源参数、功率等级,以及SMT 连接器与笼子的机械尺寸和规范。

DSFP 由Amphenol、Finisar、华为,Molex 等多家公司推出,旨在为5G 移动提供能兼容当前接口的更高速率的下一代接口。基于当前应用广泛的SFP+/SFP28 接口,DSFP 能够在相同占用空间的情况下,将SFP+/SFP28 模块密度翻倍,在充分利用现有尺寸基础上实现高密度传输。

1.1 DSFP硬件接口介绍

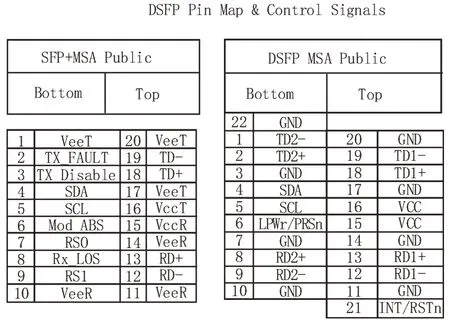

DSFP 采用了0.8 mm pitch 的22pin SMT 连接器。其与SFP+/SFP28 的pin 定义有所不同。DSFP和SFP+pin 定义对比如图1 所示。

图1 DSFP和SFP+pin定义对比

由于DSFP 增加了两对高速Serdes 差分线(一对TX,一对RX),所以DSFP 在之前SFP+管脚定义上有很大不同。根据图1 可知区别如下:

1)DSFP 在SFP+20pin 管脚定义上增加了pin21和pin22,其中pin21 紧邻pin11,pin22 紧邻pin1。

2)取消了SFP+的RS0、RS1、RXlos、TX_fault 和TX_disable。

3)pin6 为Low Power Mode/Module Present (Mod_Abs)双向复用管脚,其Module Present 与SFP+/SFP28的Mod_Abs 定义相同。

4)pin21 为Module Interrupt and Reset 的双向复用管脚。

总得来说,DSFP 牺牲了部分低速信号管脚换取了高速信号的增加。DSFP 高速信号包括两收两发差分对,从物理上来说,它可以支持单port 和双port两种模式。根据规范,DSFP 模块每条lane 可以支持9.95~53.1 Gbps 的速率,调制方式为NRZ 或PAM4。低速接口信号SCL 和SDA 与SFF-8431 规范中定义一致,在此不赘述。

低速信号的重点是两组双向复用管脚LPWn/PRSn 和INT/RSTn。从DSFP 光模块方向看,LPWn和RSTn 是输入pin,PRSn 和INT 是输出pin。

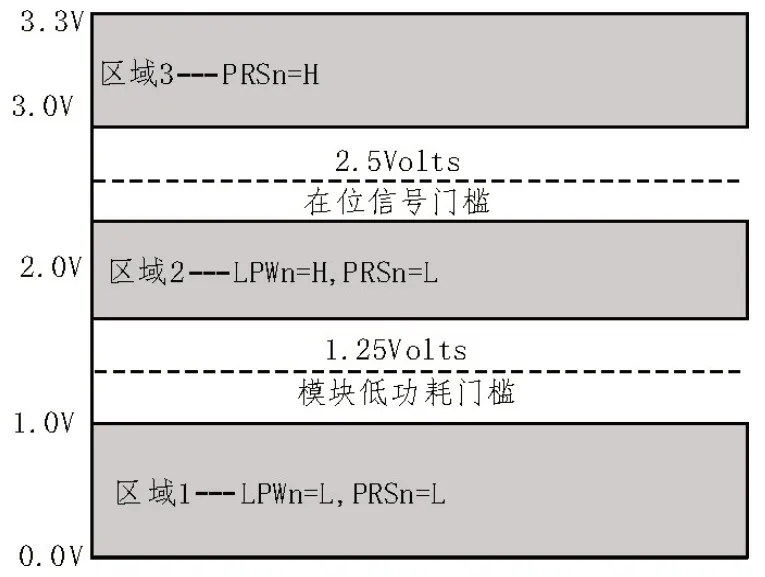

以LPWn/PRSn 为例,LPWn 是Host 发出到光模块的,使能DSFP 光模块Low Power mode,同时DSFP输出PRSn 信号到host,指示其是否在位。LPWn/PRSn 信号采用三电压区域来实现管脚的双向双功能。三电压区域如图2 所示。

图2 DSFP LPWn/PRSn三电压区域

1)区域1:电压从0 V 到1.25 V 之间的区域,代表模块在位并且为低功耗模式。

2)区域2:电压从1.25 V 到2.5 V 之间的区域,代表模块在位并且为高功耗模式。

3)区域3:电压从2.5 V 到3.3 V 之间的区域,代表模块不在位。

简单来说,该管脚就是输入管脚以1.25 V 为判断门限,输出管脚以2.5 V 为判断门限,与INT/RSTn功能类似。下面将举例说明该类管脚的应用。

1.2 DSFP模块功率分类

DSFP 模块根据功率分为I(1.0 W 以下)、II(1.0~1.5 W)、III(1.5~2.5 W)、IV 四类(2.0~3.5 W)。模块上电时及上电后的低功耗模式除LPWn 管脚控制外,还可以通过ForceLowPWR Bit(CMIS Byte=26,bit=4)进行控制。

总地说来,DSFP 在兼容SFP28 机械尺寸的基础上,将高速线pair 扩大一倍,同时能支持56 G PAM4,未来计划支持112 G PAM4,理论上可以实现224 G传输速率。

2 TOR交换机中DSFP设计

2.1 DSFP硬件设计

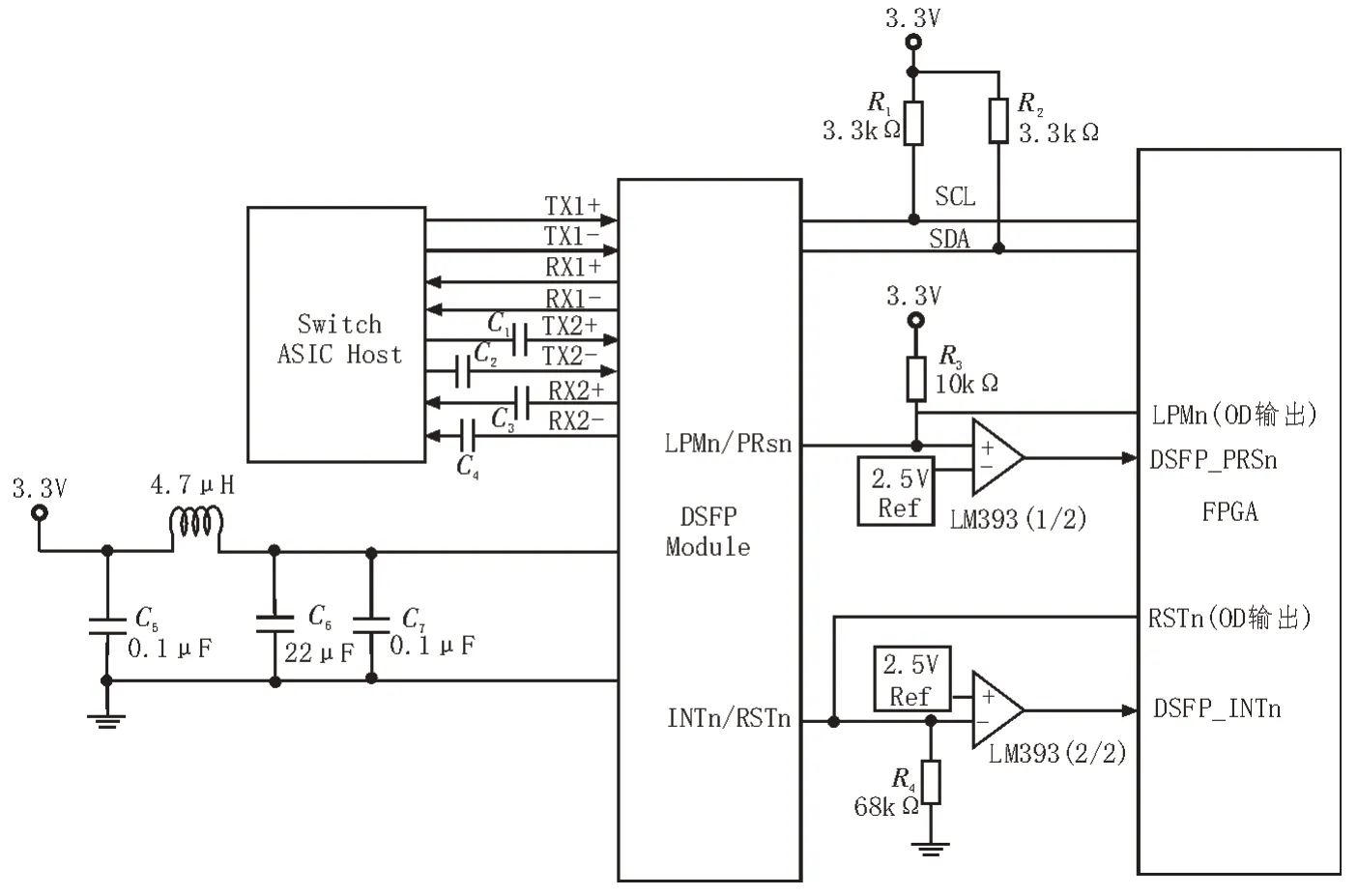

因为DSFP MSA 主要是针对DSFP 接口、光模块电气性能接口和机械的规范,所以DSFP 的设计主要是硬件设计。DSFP 接口硬件设计如图3 所示。

图3 DSFP接口硬件设计

1)高速走线

DSFP 提供双lane 的PAM4 高速Serdes 接口,DSFP 光模块可以通过两收两发高速通道与Switch ASIC 直连。

对于TD2 和RD2 两对高速Serdes 与DSFP 光模块的连接,如果可以接入SFP+/SFP28 光模块的话,需要串接0.1 μF AC 耦合电容,以保护ASIC 的高速Serdes 接口RD2+/-和TD2+/-不被损害。同时DSFP MSA 也建议ASIC 先关闭TD2+/-,检测到接入是合法的DSFP 模块后才开启TD2+/-。

2)IIC管理接口可以通过FPGA或CPU进行管理。

3)最主要的是双向双功能电路的设计。下面主要是介绍LPWn/PRSn 和INT/RSTn 管脚的电路连接。

根据三电压区域的设计,单板电路中需要提供2.5 V 的参考电源,可以通过DC/DC 电源转换芯片得到。1.25 V 的参考电源为DSFP 光模块使用,会集成在光模块内,对于交换机的设计,只要考虑host 端的设计,即考虑2.5 V 的参考电源设计即可。如图3 所示,对于双向设计电路使用电压比较器,使用双运放LM393,双运放分别应用于LPWn/PRSn 和INT/RSTn,这样每个接口需要一个LM393。

DSFP 的LPWn/PRSn 信号连接到比较器的正向端,当DSFP 不在位时,PRSn 由于上拉10 kΩ电阻电压为3.3 V,比较器的正向端电压大于负向端电压2.5 V,比较器输出高电平到FPGA,指示module 不在位;如DSFP 在位,因DSFP 内部有下拉10 kΩ电阻,由于上下拉电阻分压,比较器的正向端电压为1.65 V,小于负向端电压2.5 V,比较器输出低电平到FPGA,指示DSFP 模块在位。而在SFF-8431 规范中,SFP+/SFP28 光模块的在位信号Mod_ABS 是直接在模块内接地的,这也是DSFP 和SFP+/SFP28 的区别之一。

FPGA 通过I/O 管脚(配置为输出)连接到电压比较器的正向端。需要控制LPmode 时,FPGA 输出为Low,将直接使DSFP 管脚接收到0 电平,设置其为Low power mode;反之,如需设置为High power 模式,则FPGA 输出管脚为高阻,此时LPWn 的管脚电平因上下拉10 kΩ电阻进行分压得到1.65 V 左右的电平,高于DSFP 模块内的1.25 V 判断值,所以设置模块为High power mode。

DSFP 的INT/RSTn 信号连接到LM393 的另一个电压比较器,下拉68 kΩ电阻到GND。DSFP 在位时,该管脚有5 kΩ电阻上拉电压到3.3 V,DSFP 有中断产生时,DSFP 模块会关闭其内部的8 kΩ下拉电阻,这样INT/RSTn 管脚的电平由内部上拉5 kΩ和外部下拉68 kΩ决定,其大于2.5 V 参考电压,导致电压比较器输出为0,通知FPGA 有中断产生;反之无中断时,DSFP 模块会开启其内部的8 kΩ下拉电阻,这样INT/RSTn 管脚的电平由内部上拉5 kΩ、下拉8 kΩ和外部下拉68 kΩ决定,电压为1.9 V左右,低于2.5 V,电压比较输出为高,FPGA 接收无中断。

同样,FPGA 通过I/O(配置输出管脚)连到DSFP的INT/RSTn,FPGA 输出为Low 时,直接拉低电平为0,将module 复位;反之FPGA 输出高阻三态,该电平由外部上下拉电平决定,其值高于DSFP 内部的1.25 V 判断门限,DSFP 解除复位。

上述电路设计在参考DSFP MSA 规范的基础上进行了修改,借助FPGA 的功能使其设计连接更简洁、控制更方便。

2.2 DSFP的控制方法

在DSFP 光模块的供电电路中,使用电源开关对其供电进行限流保护,防止光模块插错,误插或因光模块损坏短路等问题导致DSFP 的3.3 V 供电电路出现过流甚至电感烧毁的情况。电流限流值可以根据使用的DSFP 光模块的power 等级来定。具体的DSFP 模块控制方法建议如下:

上电后FPGA 将各路DSFP 电源开关默认关闭,同时将LPmode 输出管脚设置为低电平,并默认使能为Low Power mode,默认复位pin 输出为低电平。当FPGA 检测到DSFP 光模块在位时,开启电源开关,但是保持复位和Lower power,然后delay 10 ms 后释放Reset,再过10 ms 后释放Lower power mode 到High power mode。如果检测到DSFP 模块不在位,同时关闭电源开关,使能复位和使能Low power mode。

2.3 其他使用规范

DSFP 的SMT 连接器与SFP+/SFP28 不具有兼容性,但是其Cage 是可以与SFP+/SFP28 兼容的,这使得在机构设计上能够保持和SFP28 保持一致。BOM 的使用需要注意DSFP 功耗的等级,从而决定是否需要在SFP28 的基础上更新散热器,在某些功耗不高的应用中,SFP28 的cage 能够满足DSFP 的要求。

根据最新的DSFP MSA,新的DSFP 管理接口规范使用推荐CMIS 规范。其中模块的类型可以参考SFF-8024,DSFP 的类型值为1B h,用户可以通过该值识别DSFP 光模块。

3 DSFP的应用

对于TOR 交换机设计来说,以一个支持56 G PAM4 的8 TB/s 带宽Switch ASIC 为例,其Serdes 数量为160 个Lane,硬件设计上可以设计成48 个下行DSFP 接口和8 个上行QSFP-DD 接口,DSFP 接口连接到机柜服务器,上行QSFP-DD 连接到数据中心spine 交换机。DSFP 硬件设计第一节介绍过。通常1U 的交换机在设计成48 个100 G 和8 个400 G 的接口时,端口数量多,空间尺寸是个很大的问题。如果100 G 采用QSFP28,空间上将完全不能容纳这么多端口,此时DSFP 端口发挥出其独特的优势,因为其cage 规格尺寸与SFP28 兼容,同时QSFP-DD 开孔尺寸与QSFP28 是一样,所以在机构尺寸上完全可以和数据中心普遍使用的48×25 G(SFP28)+8×100 G(QSFP28)TOR 交换机使用同样的结构件。以此看来,在48×100 G+8×400 G 的TOR 的应用上,DSFP 是非常不错的选择。

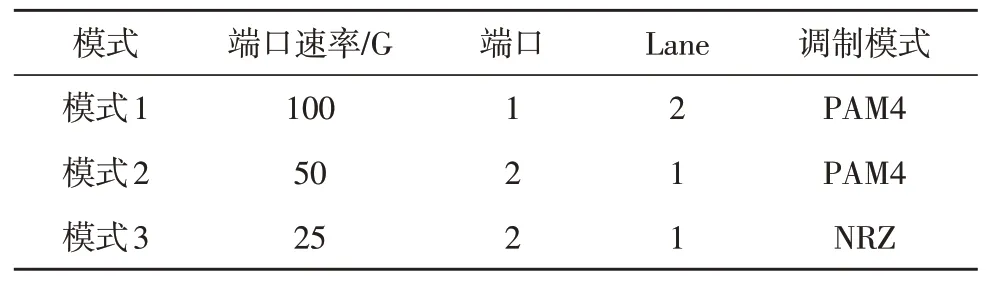

DSFP 主要用于100 G 接口通信,在数据中心应用的主要场景主要是服务器的Smart NIC 卡和网络TOR 交换机之间的互联。根据使用场景,DSFP 应用配置如表1 所示,DSFP 的应用主要分为以下几种情况:

表1 DSFP应用配置

1)100 G 的接口

接口主要是100 G(2×50 G PAM4)。在TOR 的交换机上,DSFP 接口配置为一个双Lane 单port,端口速率为100 G。同样在服务器如Smart NIC 侧,DSFP也配置为双Lane 100 G 接口。通常通过AOC 或DAC在整机架内可以通过光模块进行互联。

2)50 G 接口

主要应用于50 G 场景,TOR 交换机配置为两个port,每个port 使用一个56 G Lane,这种模式即通常的Breakout 模式。通常对端服务器网卡也使用DSFP Breakout 模式,使用DAC 和TOR 进行互联。

3)25 G 接口

这种应用是在TOR 中将DSFP 配置为两个port,每个port 使用一个25 G 的Lane。这种应用是将Switch 的Serdes 速率从50 G 降到25 G 使用。这种使用情况下,可以使用1 分2 的BreakoutDAC 或AOC cable,即一个TOR DSFP 端口连接服务器网卡端的两个SFP28 端口。这样的使用情况通常是服务器网卡SFP28 端口不变,通过TOR 交换机的DSFP 扩充了SFP28 的接口容量,如对同样的25 G NRZ Serdes 的交换芯片,可以将48 个SFP28 合成24 个DSFP 端口,节省了一半的空间,或者使用同样的空间增加一倍的接口容量。

4 DSFP未来发展

DSFP 除了支持56 G 接口,也同样支持未来的112 G 接口。在交换ASIC 领域,随着56 G PAM4 和112 G PAM4 的Serdes 的兴起,服务器网卡侧及TOR交换机侧PAM4 的使用将会是主流。100 G QSFP28很可能会成为历史,下一代100 G 及200 G QSFP56可能会成为未来服务器和TOR 交换机的应用的方向。DSFP 作为支持50 G 和100 G 的PAM4 应用接口之一,能够兼容100 G 和200 G,在未来数据中心使用中必定会有一席之地。DSFP 相比QSFP56 和之后的QSFP112G,占用体积小,可以连接的服务器数量更多。

当前阶段112 G PAM4 的Serdes 无论是交换芯片还是光模块都还在设计阶段,待后面技术成熟和大规模商用后,2×112 G DSFP 也将会被广泛应用。

另外,如同QSFP-DD 将QSFP56 密度翻倍一样,DSFP MSA 也提出DSFP 的升级版本DSFP-DD。DSFP-DD 为双密度,同样采用50 G PAM4 的Serdes,但是Serdes 通道翻倍变为4 channel,所以可以支持4×50 G=200 G 速率的传输,未来可以支持4×100 G=400 G 速率。

DSFP-DD 向后兼容DSFP,在保持DSFP 22pin脚数不变的情况下额外增加了21 pin,总pin 数为43 pin。与QSFP-DD 类似,DSFP-DD 的Cage 尺寸和SMT connector 尺寸因容纳更多的pin 脚而变宽变深。不过,DSFP-DD 当前状态并不成熟,还没有更加详细的规范,期待后续会有更新。

5 结束语

为交流和推广DSFP 接口在数据中心的应用,该文介绍了DSFP 接口的主要特点,并详细介绍了其硬件设计、功率等级及接口监控的经验。通过结合48×DSFP+8×QSFP-DD 的TOR 交换机实例,介绍了其端口的各种配置应用场景。文末也展望了DSFP未来在数据中心的发展。该文的介绍对后续DSFP的进一步应用研究具有一定的参考价值。

在参照DSFP MSA 规范的基础上,该文结合交换机的实际使用,提供了包括硬件接口电路设计,功率等级及接口监控方法。其中硬件电路设计与MSA相比,节省了器件,简化了设计。另外,接口的监控方法经验证可靠有效。目前文中设计的1U TOR 交换机在经过充分的测试之后,正在某互联网客户机房使用。顺应当前交换机白盒化趋势,该文介绍的DSFP 相关设计方法和应用可以为其他用户提供有价值的参考,对于DSFP 接口应用的推广有也很大的帮助。

但是由于pin 定义的大不相同,DSFP 接口在向下的接口(SFP28),硬件接口的兼容性上并不友好。同时,将DSFP 的100 G 降速到25 G 造成了资源的很大浪费,这也是不建议在同一硬件上同时兼容DSFP和SFP28 的理由。

但是,另一方面对于普通的25 G NRZ 的交换ASIC,利用DSFP 接口可以将两路25 G 的lane 合在一个端口上,节省了交换机的面板空间,可以接更多的服务器接口。