基于EPS信号完整性研究与设计

黄瑞,刘锴,潘亮,文礼,丁伟娜

湖南东嘉智能科技有限公司,湖南株洲 412000

0 引言

随着汽车电子技术的高速发展,人们对汽车驾驶可靠性和安全性也提出了更高的要求,作为汽车驾驶的关键部件,电子助力转向(electric power steering,EPS)系统已成为汽车的标准配置。早期传统的电动助力转向系统成本低廉,但其寿命短、可靠性差、效率低等固有缺陷,阻碍了电动助力转向系统的进一步发展。本文通过研究信号的反射,从根本上减小信号沿传输线向前传播过程中的反射问题,保护器件在稳定条件下正常工作,使得信号输出更加平稳,控制更加平滑,大大提高了EPS系统的可靠性和效率,延长了电动助力转向系统的使用寿命。

1 信号完整性介绍

1.1 信号完整性定义

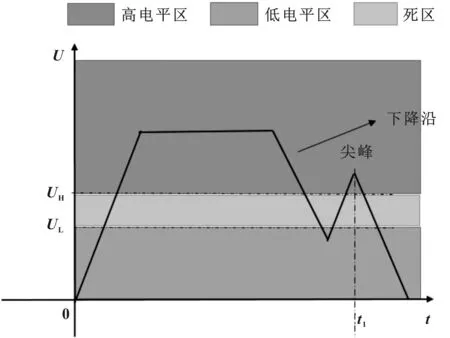

信号完整性(signal integrity,SI)是指信号在传输路径上的质量,传输路径有多种,如普通金属线、光学器件等。信号完整性包括互连、电源、器件等引起的所有信号质量和延时等问题,信号波形严重畸变、信号边沿不单调,对于上升沿触发采样的电路,可能导致对同一数据的多次采样,造成电路逻辑功能的混乱。最常见的信号反射问题包括:信号振铃、信号过冲、信号下冲、回勾等,如图1所示。如果未采取适当的改进措施,电路可能无法正常工作,因此信号完整性必须足够重视,否则失效的风险将大大增加。

图1 信号传播波形示意

1.2 信号反射的产生

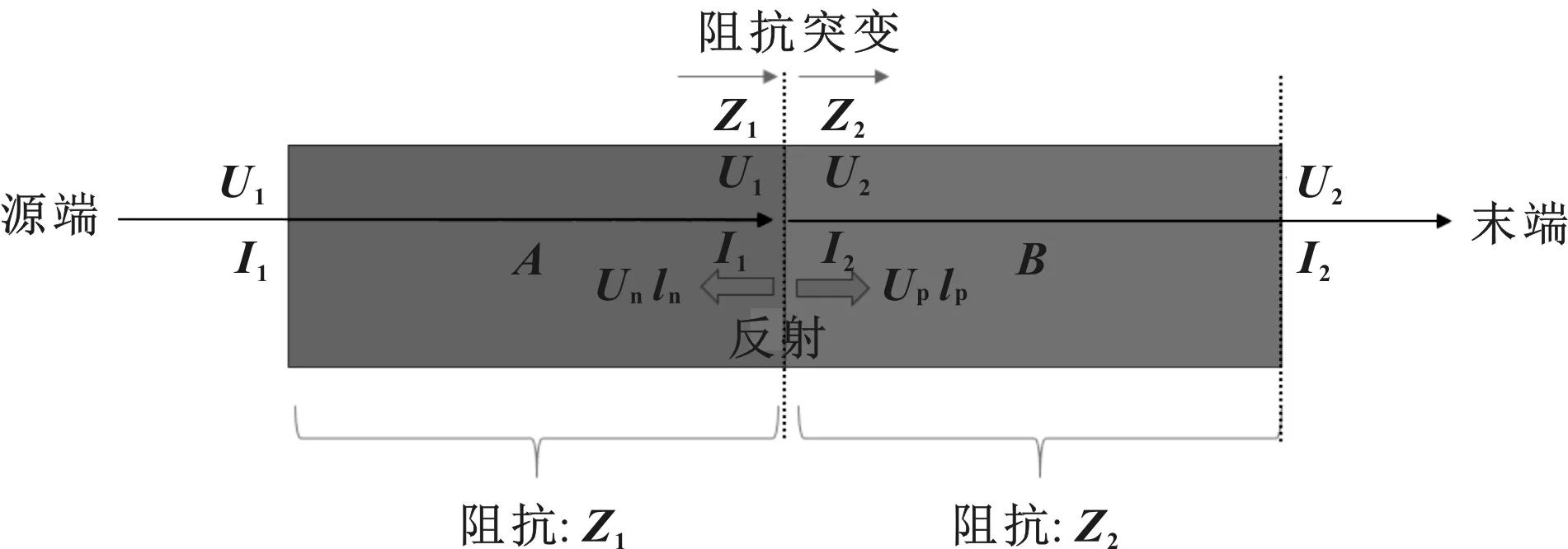

信号的反射和传输线的阻抗密切相关,只要传输线中存在阻抗不相等的点,就会在此处发生反射。假设信号传输过程中经过阻抗不相等的点,A阻抗为Z1,B阻抗为Z2,如图2所示。

图2 阻抗突变示意

由于电流和电压不会发生突变,在极短的时间内,分界面两侧的电压和电流相等。即:

(1)

式中:U1、I1分别为源端电压和电流信号;U2、I2分别为末端电压和电流信号。

当阻抗Z1、Z2不相等时,信号就会发生反射,一部分电压Up沿正向传播,产生一个正向电流Ip;另一部分电压Un沿反向传播,产生一个反向电流In,由于分界面两侧的电压相等,则:

U2=(Up/Un)±U1

(2)

要使分界面两侧电流相等,有:

I2=(Ip/In)±I1

(3)

通过调整正向电压和反向电压的关系,保证电流连续,引入反射系数,反射系数反映反射电压与源电压的比值,其中反射系数ρ为:

(4)

式中:UF为反射电压;UI为源端电压;Z1、Z2为阻抗。

当ρ=0时,无信号反射;当ρ=1时,即Z2=∞,开路时发生信号全正反射;当ρ=-1时,即Z2=0,短路时发生信号全负反射[1]。

在阻抗匹配的情况下(ρ=0),负载可以吸收所有信号的能量。在阻抗不匹配,只有一部分能量被吸收,剩余的能量以电波的形式向相反方向反射。反射次数和能量受源阻抗和负载阻抗不匹配的严重程度影响。两种最差情况是开路(ρ=1)和短路(ρ=-1),分别对应于无限负载阻抗和零负载阻抗。这两种情况没有能量被吸收,因此所有的能量都被反射。信号反射产生额外的幅度和延迟,经过传输线在源端信号上进行叠加,对于无损传输线,信号会无休止地振荡,对于常用传输线,信号振荡会越来越小,直至趋于稳态值。

信号反射中还有一种常见的现象,边沿迟缓,也称回勾。产生这种阶梯电压是由于源端信号在上升沿和下降沿时,反射信号与源端信号进行叠加,当上升沿与反射电压变化规律一致时,会产生上回勾,在下降沿会产生与源端信号相反的脉冲信号,即下回勾。向下尖峰脉冲示意如图3所示。

图3 向下尖峰脉冲示意

由图3可知,这个向下的尖峰可能会导致逻辑电平的错误。在源电压信号低于UL时,认定为低电平;高于UH时,认定为高电平。而回勾的产生在高低电平来回跳动,当持续时间超过迟滞时间时,会进行误开关动作,控制不稳定;当用于开关电路时,极易引起信号的逻辑混乱,导致系统性失效。

传输线、电源、器件引起的信号质量和延时等问题也无法避免,由于PCB布局走线过程和器件本身引入的大量寄生参数,使得电路设计过程中变得尤为复杂[2]。因此,合适的阻抗匹配、谐振电路的抑制、参考平面的一致性等都需要深思熟虑。

2 EPS信号完整性设计

2.1 EPS系统

EPS系统主要由扭矩传感器、车速传感器、减速机构和电子控制单元组成。其中电子控制单元(electronic control unit,ECU)通过PWM驱动电机在导通运行区域和换向过程中正确执行,这就要求在高速开关频率下,ECU能精确通过PWM的占空比和高低电平进行逻辑控制,使电机能正常且平滑运转,从而达到电动助力的效果。

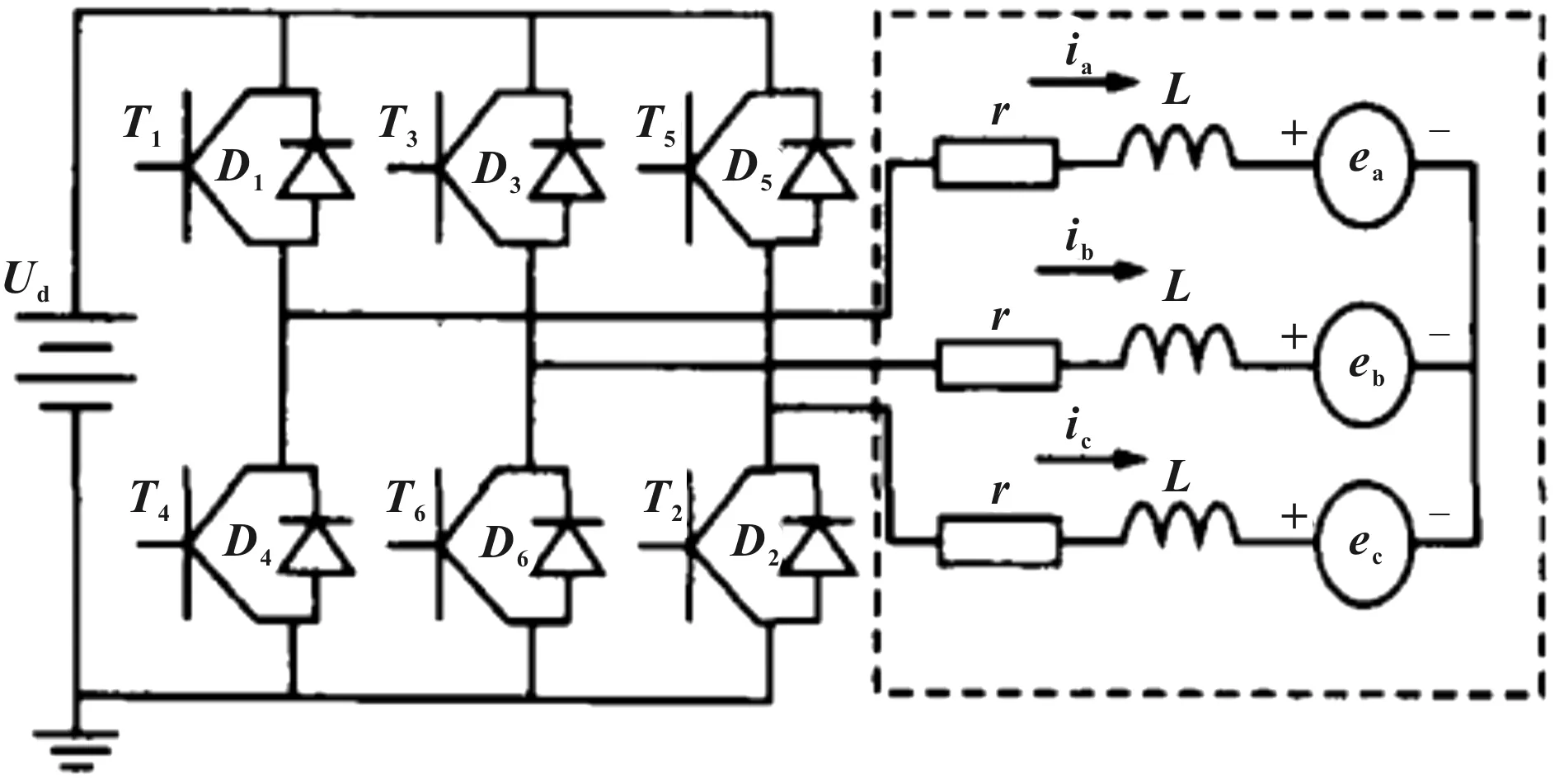

2.2 ECU信号分析

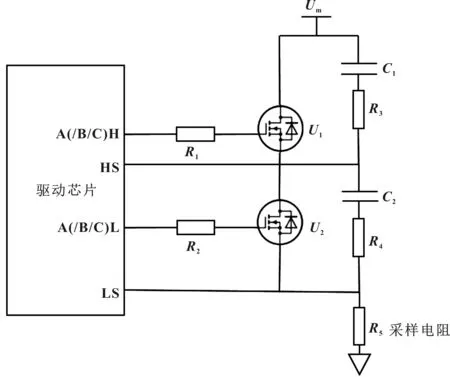

ECU包括单片机MCU、电源管理模块、电机驱动模块、采样模块等,其中电机驱动模块通过PWM控制驱动电机三相正常运行,驱动电机时,需要驱动电机的上桥臂和下桥臂不能同时导通,如果同时导通,大电流会造成系统失效,其拓扑图如图4所示。

图4 ECU电机驱动模块拓扑图

电机驱动模块中的功率半导体MOSFET、二极管、电容等在开关回路下引入了大量的寄生参数,当阻抗无法匹配时,寄生的阻抗和容抗构成谐振电路,信号反射使得信号发生振荡、过冲等。在电机运行时,每个工作状态都有导通运行区域和换向运行区域,每个工作状态的运行区域时间极短,上桥臂和下桥臂通过MCU进行PWM调制,在调制过程中,既要求驱动信号过冲不超过MOSFET的耐压值,又需要在高速开关频率下信号迅速收敛。

2.3 ECU信号完整性设计

在进行驱动电路设计时,首先考虑布局布线时,驱动信号至MOSFET源极走线的长度不宜过长,导致阻抗不匹配引起的高频振荡。其次提供足够大的充电电流使MOSFET栅-源电压上升到导通电压,保证MOSFET快速且可靠的导通。在关断瞬间时,MOSFET栅源电压通过低阻抗通路快速泄放电流,保证开关管快速关断[3]。

在开关回路中不可避免会引入寄生参数,环路振荡频率计算公式为:

(5)

其中杂散电感Lck主要来源于PCB、器件本身,寄生电容Cck存在于MOSFET的结电容中。在设计电路时要尽量减小传输线的长度、匹配的阻抗、合理的布局器件、减小环路的寄生参数,同时选择合适的MOSFET[4]。

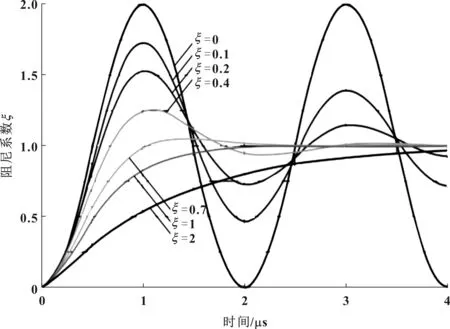

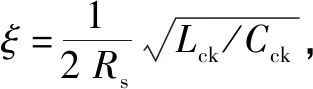

为了兼顾系统的响应时间和稳定性,需将阻尼系数ξ调整为1,其计算公式为:

(6)

其中Rs为导线匹配电阻,不同的阻尼系数,对于减小信号终止时的振荡起着不一样的作用,对于EPS驱动电路来说,信号不发生振荡,也就是ξ=1时,对于控制电路正常运转发挥巨大作用。不同阻尼系数与响应时间关系如图5所示。

图5 不同阻尼系数与响应时间关系

3 实例分析

3.1 电路测试现象

以EPS系统中驱动永磁同步电机电路为例,供电电压Um为12 V,为驱动电路供电;预驱芯片输出脉冲宽度调制(PWM)占空比调节A、B、C三相导通顺序和时间,A、B、C分别为电机三相,在图6中描述其中一相的接法,其他两相类似。其中C1、R3、R4、C2构成上桥臂和下桥臂的缓冲吸收电路;MOSFETU1、U2为半导体功率器件;R1、R2为栅极限流电阻,用于调节MOSFET的开关斜率;对电路进行阻抗匹配,减小信号反射;R5为采样电阻,对电流进行采集[5]。

图6 电机驱动模块设计

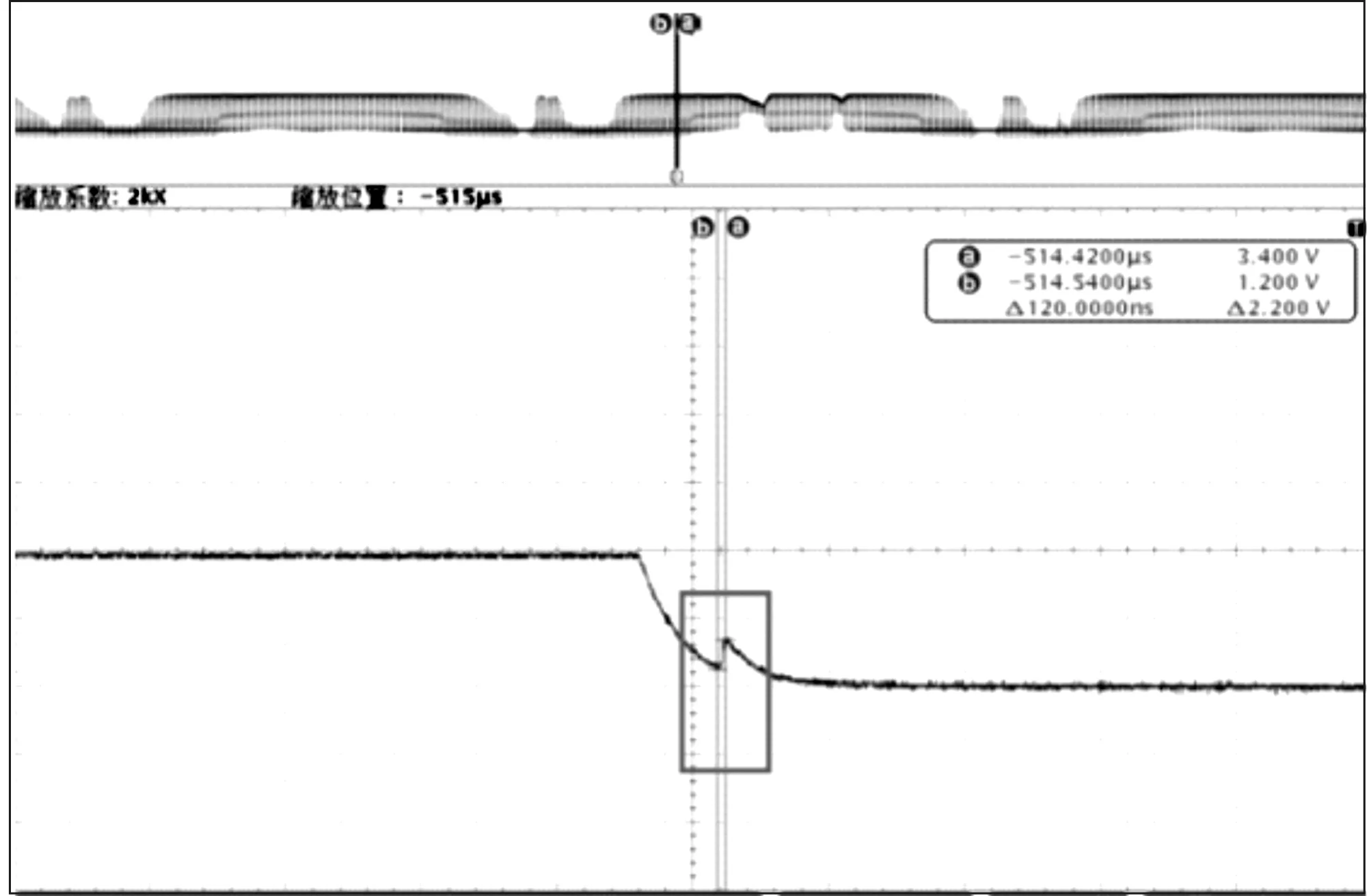

此设计选用N沟道MOSFET,其中漏极和源极电压UDS耐压值为40 V,器件导通电压为3 V,持续时间为80 ns,在软件程序中设置死区时间为2 μs。在测试中发现,以B相上桥臂为例,驱动电路的MOSFET栅源电压出现回勾,其回勾深度为3.4 V,持续时间为120 ns,超过导通电压为3 V,器件长时间工作后性能下降。MOSFET栅源电压测试回勾图如图7所示。

图7 MOSFET栅源电压测试回勾图

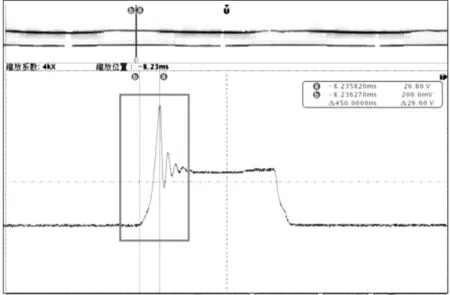

同时测量MOSFET漏源电压出现振荡,最大过冲为27.6 V,振荡多次后才进行收敛,电压信号出现严重畸变,1 ms后信号才趋于稳定。MOSFET漏源电压测试振荡图如图8所示。

图8 MOSFET漏源电压测试振荡图

信号在传输过程中,其反射电压与源电压12 V进行叠加,过冲最大达到27.6 V,经过多次反射后,恢复12 V正常电压,详见表1。发现经过多个振荡后,系统才稳定输出。

表1 源电压、接收电压及反射系数关系

3.2 电路性能分析与改进

在高速开关管的作用下,信号在PCB板间经过下降沿时发生反射,形成了向下的尖峰,此时回勾的深度已经超过了开关管的导通电压3 V、持续时间120 ns,大于MOSFET的最短开启时间80 ns,在这个阶段,由于误导通,会使开关频率在原有的基础上扩大一倍,增加了MOSFET的开关损耗。另外,在3 V电压下,MOSFET不是完全导通,比完全导通下的电阻RDSON要大,增加了MOSFET的导通损耗,在两种损耗叠加下,大大提高了器件的发热量,从而增加了系统的不稳定性,严重情况下会烧毁器件,造成EPS系统性能失效。因此,回勾深度需要及时处理。在考虑减缓回勾深度时,一方面可以减小回勾深度的幅值,使其小于开启电压;另一方面可以通过减小回勾持续时间,当持续时间小于MOSFET的开启时间时,则回勾深度不影响MOSFET的开关状态。

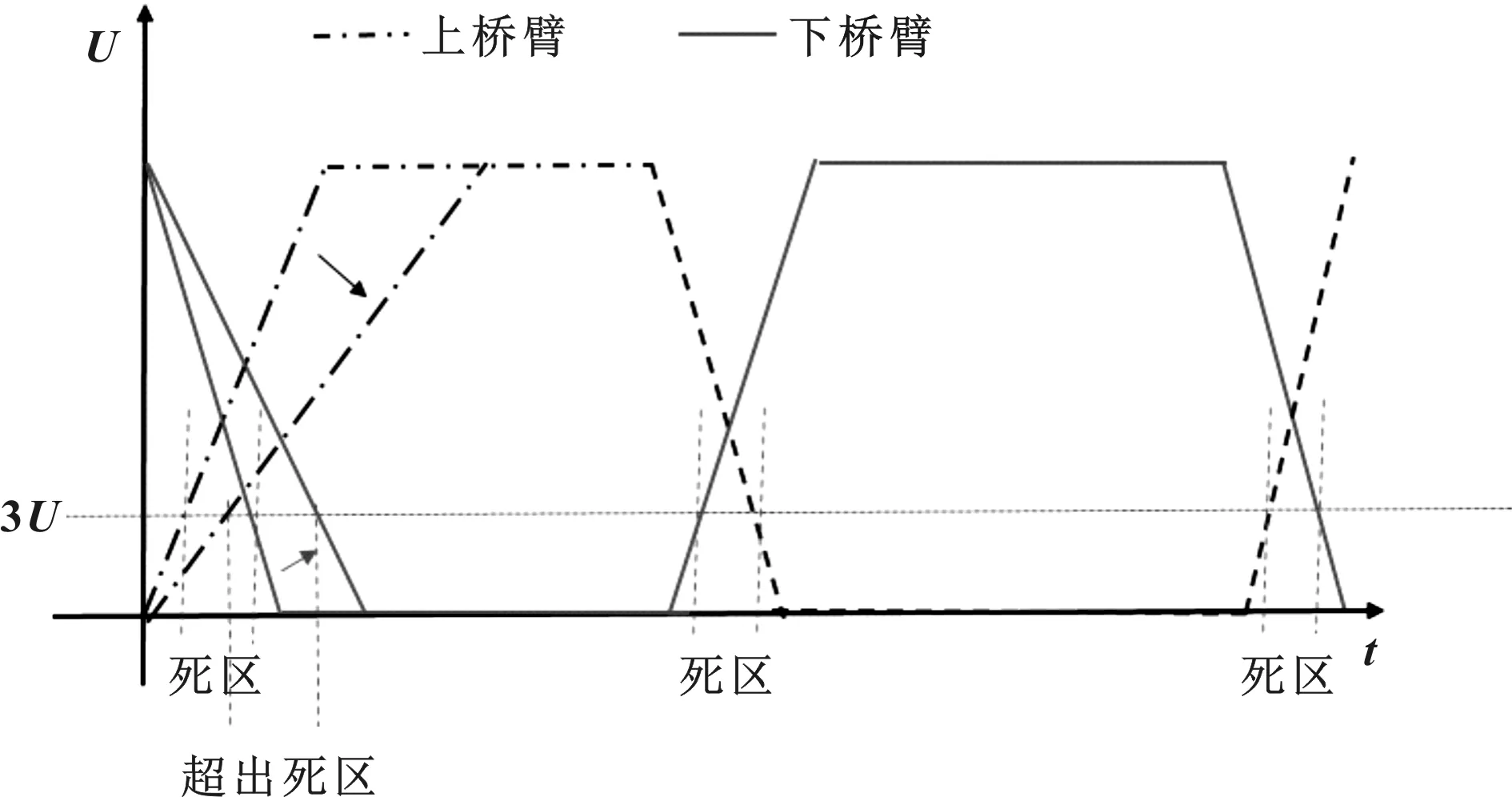

对于减小回勾深度,往往通过处理MOSFET的开关速度来实现,信号反射过程中,需要匹配合适的栅极电阻,电阻越大,回勾深度越大,但是过小的电阻会引入新的问题,MOSFET开启时间会减小,使开关斜率变陡带来过冲问题,同时还需考虑MOSFET开启时间大的情况下,同一相上桥臂导通,下桥臂关闭的边沿,过缓的延时也会促使上下桥臂的同时导通,其时序图如图9所示。所以在开启时间的选择上,要兼顾回勾、过冲和信号迟延问题上的平衡。

图9 上桥臂和下桥臂导通时序图

经过调节R1、R2阻值,发现在传输线上加上一个阻值不低于50 Ω、不高于75 Ω时取得良好效果。在下降沿过程中,测试回勾深度为2.4 V,小于MOSFET的导通电压3 V,满足设计要求。MOSFET电压测试回勾改进图如图10所示。

图10 MOSFET电压测试回勾改进图

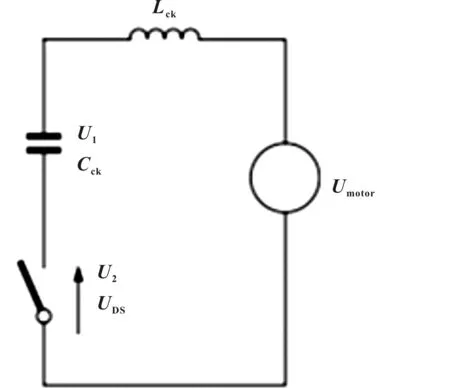

从理论上讲,如果反射系数ρ不为0,电路将无限振荡。但在实际电路中,因为存在阻抗,反射会越来越弱,直至消失。由于PCB走线、器件本身、板间等影响,总会存在杂散电感Lck和寄生电容Cck,其等效电路如图11所示。

图11 MOSFET U1导通、U2关闭等效电路

图10中振荡问题除了可以通过减小传输线的长度,阻抗匹配、器件合理的布局来减小,还有一个重要手段,设计RC缓冲电路吸收电路振铃,抑制MOSFET在开启过程和反向恢复过程产生的高频振荡。其设计等效如图12所示。图中Rs和Cs为RC缓冲电路。

图12 缓冲电路设计等效

在设计及缓冲电路前,首先确定时钟和PCB板间固有的电感量Lck,其次通过增加已知的RC缓冲电路,确定引入缓冲电路后的时钟,再调整阻尼系数ξ为1,计算Rs和Cs。改进步骤如下:

(1)去掉R3、R4、C1、C2,通过示波器测试MOSFET漏源两端电压,测出时钟频率f0为0.016 7×109Hz。

(2)将R3、R4设为0 Ω,引用辅助电容C1、C2为22 nF,通过示波器测试MOSFET 漏源两端电压,测试已知缓冲电路的时钟频率f1为0.005 6×109Hz。

(3)计算系数X:

X=f0/f1

(7)

通过计算得到X约为3。

(8)

得到Lck=33.06。

(9)

得到Rs=0.48。

(6)取符合实际工程的Rs为0.47 Ω,重新计算Cck:

(10)

得到Cck=267 nF。

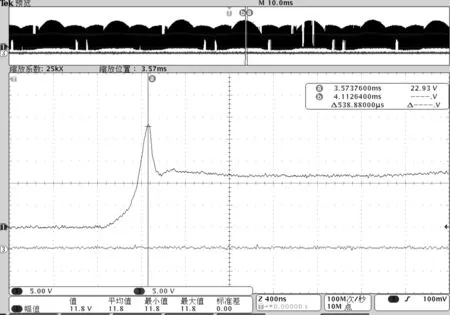

通过上述6个步骤,选定RC缓冲电路的电容C1、C2为270 nF和电阻R3、R4为0.47 Ω,其他两相缓冲电路同理,重新进行测试。MOSFET漏源电压改进测试如图13所示。

图13 MOSFET漏源电压改进测试

改进后信号在传输过程中,过冲最大达到22.93 V,小于MOSFET漏源电压的耐压值40 V,经过两次反射后,恢复12 V正常电压,振铃消失,系统稳定输出,符合设计要求。改进后的源电压及接收电压及反射系数关系见表2。

表2 改进后的源电压及接收电压及反射系数关系

4 结束语

本文采用电机驱动电路对EPS信号完整性进行了试验分析,讨论了信号反射、反射类型以及如何消除和减小信号反射,实例分析过程中通过研究信号的反射来源,从根本上减少信号沿传输线向前传播过程中的反射问题,保护器件在稳定条件下正常工作,为EPS电路的可靠性设计提供了一种有效的方法,这对后续电子转向系统中ECU的功能设计和可靠性设计具有重大意义。