神经网络异构加速跟踪系统设计与实现

吴 凯,党 鑫,郭风祥,焦禹铭,宋庆增

(天津工业大学 计算机科学与技术学院,天津 300387)

1 引 言

人工智能技术早在上个世纪五十年代便被研究者们提出和建立,人工智能技术的初衷是为了让机器可以模拟、扩展、延伸人的智能.目前,深度学习技术是人工智能领域最热门的研究方向,深度学习技术自2006年被提出以来,已被广泛的应用在计算机视觉,语音处理,数据挖掘等多个领域.在计算机视觉领域当中,目标检测是指在给定的目标范围内提取出有效的目标区域.近年来,目标检测技术在监控、搜寻、跟踪等任务中做出了极大地贡献,降低了这些任务所需要的人力成本,提高了任务的执行效率.

在目标跟踪领域,最近的研究表明,跟踪算法使用卷积神经网络来提取特征和分类,可以使算法具备区分背景和非背景的能力,提升算法鲁棒性[1].目标跟踪系统的效果往往会被作为关键环节的特征提取所影响[2].目前的卷积神经网络模型已朝向越来越庞大和复杂的趋势发展,对算力的要求也逐渐提高,所以在目标跟踪系统中使用神经网络作为提取特征的手段,会极大的影响系统的实时性.目前对目标跟踪系统的部署通常在云端和边缘计算设备端,在云端的部署当中,通常云端需要处理多个视频流,对云端的算力和数据传输的网络延迟需求也比较高,在实时性极高的边缘计算场景当中,边缘计算设备对神经网络模型带来的庞大算力需求和功耗问题又难以解决[3].

近期,研究者们在软件层面使用模型压缩技术,如剪枝、量化等轻量化网络方法,使得算法更加适应嵌入式端的移植[4].在硬件层面,使用异构计算进行算法的加速也逐渐成为主流,常见的异构加速平台有GPU(Graphics Processing Unit)、ASIC(Application Specific Integrated Circuit)、FPGA(Field Programmable Gate Array)3种,其中GPU具有数千计算内核,可以进行海量数据的并行计算,但与之而来的数据带宽需求和功耗也十分巨大.ASIC为定制电路,成品具有功耗低性能强的特点,但是缺点在于灵活性差,一旦流片便无法更改,同时具有较长的设计周期[5].FPGA别名现场可编程逻辑阵列,具有可重构,低功耗,高度并行的特点,开发周期短,灵活度高,适合目前计算量大但更新迭代快速的神经网络算法[6].

本文针对目标跟踪系统部署在资源受限的移动平台面对的需求和问题,从软件算法和硬件电路两个层面进行优化,选取设计更为灵活的高性能FPGA平台进行系统设计和搭建,采取软硬件协同设计的方法,对计算任务合理的划分,使得该目标跟踪系统获得更好的性能和功耗优势.

2 算法设计

2.1 两段式目标跟踪

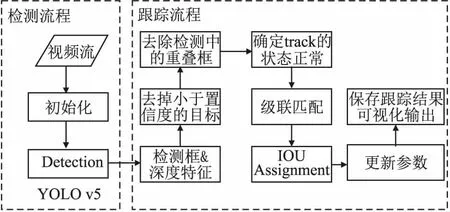

本设计采取两段式目标跟踪方法,将目标跟踪分为detection+track,即为先进行目标检测继而对检测出来相同的目标进行匹配的方式实现目标跟踪,摒弃了传统的端到端式的目标跟踪方法,此设计可以根据跟踪效果对detection部分和track部分分别采取优化手段,以达到更好的跟踪效果,算法的处理流程如图1所示.

图1 算法处理流程

从图1中可以看出,算法分为两部分,首先对输入视频流进行初始化操作,执行预处理和视频分帧,然后进入YOLOv5检测算法,接下来进入跟踪流程,将检测算法处理后得到的检测框和特征信息进行筛查,去除小于置信度的目标,对检测框进行非极大值抑制,消除一个目标身上多个框的情况,然后算法会对每个目标使用卡尔曼滤波预测目标在当前帧的位置,来确定目标是否消失或出现新目标并确认状态,之后将预测结果和检测结果进行匹配,此时会区分目标的状态.对确认状态正常的目标进行级联匹配,未确认状态的目标会进行IOU交并比检测,重新确定位置并匹配,之后将进行下一帧的处理,更新参数,并对未匹配的目标进行删除,最后保存结果进行输出.

2.2 基于YOLOv5的目标检测

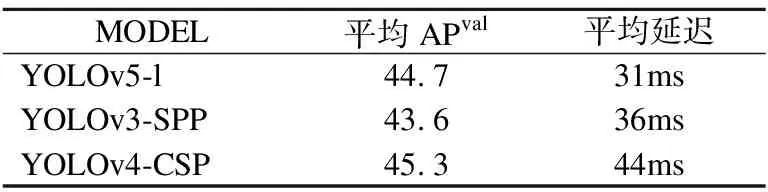

在使用目标检测为基础的两段式目标跟踪系统中,目标检测的效果对跟踪系统的性能有着至关重要的影响.目前基于深度学习为基础的目标检测算法主要分为单阶段目标检测和双阶段目标检测两种,单阶段目标检测算法将输入特征图当中的目标位置和类别信息进行回归分析,直接给出结果,而双阶段目标检测算法要先对所检测目标进行候选区域提取,再对候选区中的目标分类和候选区域的坐标进行回归修正,最后得出目标检测结果.单阶段的主流目标检测算法为YOLO(YOLO、YOLOv2、YOLOv3、YOLOv4)[7-10]系列算法;双阶段的主流目标检测算法为R-CNN((R-CNN、Faster R-CNN、Mask-RCNN)[11-13]系列算法.YOLO系列算法在检测的精度效果上不如后者,但是在检测速度上有着明显的优势.YOLOv5并不是YOLO系列的作者Joseph Redmon开发的,且其检测精度略低于YOLOv4,但YOLOv5胜在灵活性与检测速度,更加适用于部署在移动端系统当中.最新的研究结果表明YOLOv5的大小最小仅有27mb,但是使用darknet 架构的YOLOv4有244 MB,对比之下YOLOv5比v4小近90%,二者却有着接近的检测精度[14].YOLOv5与其他目标检测算法在coco数据集上的测试速度如表1所示.

表1 目标检测算法速度

YOLOv5与v4、v3相比拥有较高的精度,和最快的检测速度.同时Yolov5 按照神经网络的体量大小分为 Yolov5s、Yolov5m、Yolov5l、Yolov5x网络,4种网络的结构完全一致,方便研究者根据需求灵活使用.本设计为了跟踪系统实时化的需求,采用了检测速度较快,同时保证一定精度的Yolov5m作为使用模型.

YOLOv5的结构分为4个部分:输入端,Backbone,Neck和prediction.其中输入端YOLOv5采用了 Mosaic 的数据增强方法,该方法原理是将图片随机的进行调用,使其大小、角度随机分布生成,使其堆叠,该技术可以极大地扩充数据集数据量,从而使模型学习到更多的目标特征信息,提升模型的识别能力.YOLOv5的输入端使用了并行度的设计,使YOLOv5可以同时计算4张输入图片,变相的提升了mini-batch的参数值,这样可以优化算法对计算资源和内存的使用.YOLOv5同样引入了聚类算法,可以使用聚类来设计anchor的值,在算法训练的过程中还可以从训练集中计算出新的anchor值.算法在预测过程中会对图片的大小进行自适应调整,将图片的黑边减少,以减少多余的计算量,从而加快预测速度.Backbone中YOLOv5采用了Focus 结构和 CSP 结构,Neck中采用了FPN+PAN的结构,FPN是一种使用上采样对数据信息进行融合的自顶向下的方法,可以获得预测数据的特征图.而PAN相反采用的是自底向上的特征金字塔形式,将浅表层的定位信息传递至更深的层次当中,加强多个尺度的定位能力.最后的prediction层包含损失函数和非极大值抑制(NMS)YOLOv5采用的GIOU损失函数可以有效地解决边界问题.同时NMS可以处理同一目标上的多个目标框重合问题,选出最优解.

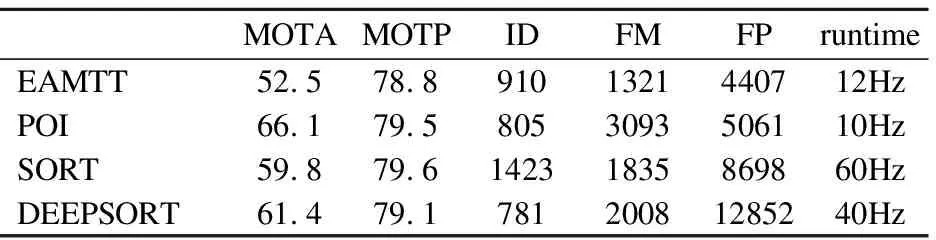

2.3 基于卡尔曼滤波和匈牙利方法的跟踪算法改进

本设计采用两段式目标跟踪,在视频流数据通过YOLOv5处理后,会进入跟踪算法的处理阶段.跟踪算法使用的是Wojke N[15]等人提出的设计思想为卡尔曼滤波和匈牙利方法结合的Deepsort跟踪框架,是一种可以处理在线实时目标跟踪的算法.Deepsort算法是根据Sort算法进行改进,在mot16数据集上Deepsort算法和其他在线目标跟踪算法的效果如表2所示.EAMTT和POI算法速度太慢不满足跟踪系统的实时性要求.Deepsort与Sort算法相比,拥有更高的跟踪精度,并且在对遮挡目标的追踪效果有更好的优势,速度仍旧可以满足实时的要求.

表2 在线跟踪算法参数

该方法使用(u,v,r,h,u′,v′,r′,h′)这8种参数来表示待跟踪目标的运动状态信息(u,v)用来确定检测框的中心坐标,r为检测框的长和宽的比值,h为检测框的高度,(u′,v′,r′,h′)这4个变量描述的是对应参数的移动速度信息.过程为在目标检测算法检测到目标当前帧所在的坐标时,会使用卡尔曼滤波的方法预测目标下一帧的位置信息,预测模型是线性和时匀速的.接下来算法将会使用预测得来的目标框和实际得到的下一帧的目标框之间的马氏距离来作为二者是否为同一目标的度量标准.

使用马氏距离作为度量标准可能会导致轨迹匹配的不稳定性.尤其是在多目标跟踪或者目标密集的场景下,马氏距离往往会失去作为度量标准的效力,目标的身份ID号转变会变得更加的频繁.因此除了预测框和目标框之间的马氏距离,Deepsort算法创新式的在每个目标当中加入了通过深度神经网络提取而来的外观特征向量,对确定的目标算法会建立一个基于该目标独有的特征集.针对目标的运动变化,速度与角度的改变使得目标的外观特征逐渐改变,算法通过计算外观特征向量集与检测到的每一个目标外观特征向量集的最小余弦距离来判断轨迹是否属于同一目标.

Deepsort算法在匹配检测框和预测框的时候,采用的是基于匈牙利方法的级联匹配模式.使用级联匹配方法可以优先匹配更加频繁出现的轨迹,使遮挡时间短的轨迹优先与现有的检测框进行匹配,有效解决因为目标发生遮挡期间使得卡尔曼滤波对丢失的轨迹不再进行持续预测而导致的跟踪失败问题.为了对抗遮挡问题,本设计还对算法进行一些调整,在匹配过程中,优化TLOST参数.当目标通过匈牙利算法对检测框的移动数据和深度学习进行初步轨迹匹配之后,确定匹配成功的,将会更新轨迹信息,如果出现未匹配成功的情况,会对未匹配的轨迹和其他未匹配的检测框进行二次匹配,在经过TLOST帧后仍未有检测框与之匹配,系统将会判断该轨迹已经终止,可以通过增大TLOST帧数值来有效解决短时间内的目标遮挡问题,但会因为算法待机等待时间的增加而产生多余计算量.

在原Deepsort算法完成级联匹配时,有部分没有进行匹配的轨迹是因为遮挡产生的,而遮挡极有可能是因为目标之间的重合产生的,可以假设至少有一个已完成级联匹配的目标与其他目标发生了重叠,导致目标被遮挡,无法完成轨迹的更新.此时可以计算所有匹配成功目标和未匹配成功目标的交并比,设定一个阈值,当其中两个目标的交并比大于此阈值,就可以认定目标之间发生重叠遮挡现象,之后将发生重叠的未匹配成功目标的预测轨迹视为该目标的实际位置,继续完成匹配,这样可以减少因为目标重叠而产生的遮挡问题而导致的跟踪失败.

3 整体设计

3.1 整体框架

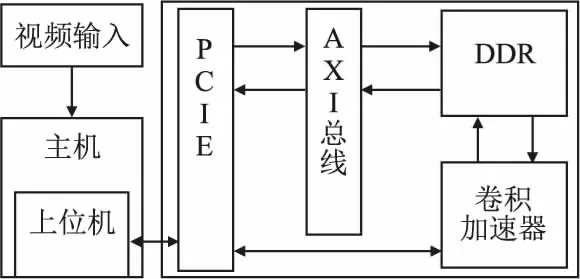

根据两段式目标跟踪的特点,本设计采取了软硬件协同设计的优化方法.为了满足实时性和最大资源利用率的需求,将系统任务划分成控制和运算两大部分,控制部分包含配置,通信,串行逻辑等,本次设计将此部分任务划分给主机端使用CPU实现,CPU适用于串行和多线程多任务处理.运算部分主要是YOLO目标检测的向前推断部分,包含大量并行的乘除法,通过FPGA中高并行度的可编程逻辑来实现,主机端和FPGA板卡通过PCIE接口进行通信,系统的整体结构如图2所示.

图2 整体架构

输入端负责视频数据的采集,并将视频流传送回主机,主机负责将视频流初始化,进行分帧操作,再通过上位机将每一帧的图像通过PCIE接口传入FPGA板卡,FPGA板卡内数据通过AXI总线进行数据交互,通过AXI Lite进行指令交互.图像数据会暂存在DDR中,经由上位机发送指令进行卷积计算加速,再将处理后的结果送回DDR,再由AXI总线经过PCIE接口将数据传送回主机,完成加速处理操作.最后主机将数据进行YOLO后处理,执行跟踪算法,流程结束.

3.2 计算模块设计

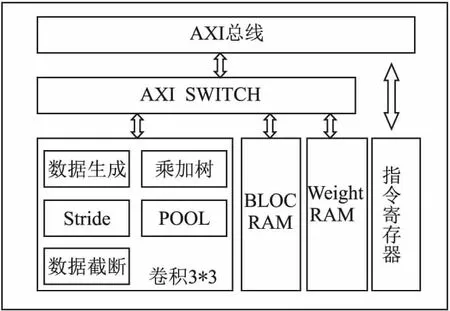

在目标检测向前推断阶段,包含大量的卷积运算,卷积运算包含大量的乘法和加法.为了更高效的进行卷积运算,本文设计了由多个并行计算单元组成的卷积加速模块,如图3所示.

图3 计算模块设计

每一个并行计算单元可以根据不同的计算任务需求来调整计算单元的类别,来完成3*3卷积,1*1卷积或者reshape操作.计算单元通过一个控制寄存器来进行操控,使用者通过上位机发送指令,经过AXI Lite总线传递指令,计算单元通过解析控制寄存器里的指令来完成复位、计算、数据传输等操作.计算所需的图片数据和权重将会由AXI总线进行传输,在开始计算时数据会通过一组直接存储器访问(Direct Memory Access,DMA)经由AXI总线搬运至计算单元,在计算单元的前后两侧都设置一个AXI switch通路选择器,在计算任务开始时,AXI switch会根据计算任务的需求,将从DDR传入的数据发送给相应的计算单元,当计算任务结束时,数据会传入另一个AXI switch中,再将数据写回DDR相应的地址中.本次设计中有几种不同功能的PE单元,以卷积3*3为例,如图4所示.

图4 3*3卷积计算单元

3*3标准卷积单元由数据生成、FPGA乘加计算资源、用来存储特征图数据和权重的Bram、指令寄存器、控制步长的Stride、减少过拟合的POOL等元素组成.Switch模块用于控制数据通路的选择,指令由PC上位机发出,经过AXI LITE端口进入模块内的指令寄存器当中,通过解析指令可以选择加载权重数据进入Block RAM或加载特征图数据开始计算.数据生成模块是一个将输入的特征图数据经过一些复用操作,变成适用于卷积操作的并行数据,方便和权重一起进入乘加树进行并行计算.Block RAM负责储存一层计算所需要的权重数据,是一块使用资源较大的BRAM,方便后续计算的数据读取,权重数据由上位机发出的控制指令调入.Weight RAM是一块使用资源比较小的RAM负责暂存一次计算使用的权重数据,开始计算时从数据生成模块处理好的并行特征图数据和Weight RAM里暂存的权重数据会进入到乘加树进行模拟卷积操作.指令寄存器是用来储存、解析上位机发出的指令,发出控制信号,控制计算模块进行数据加载和计算.乘加树模块是FPGA里的一些乘法器、加法器、DSP资源,特征图数据和权重数据会进入乘加树模块进行模拟卷积操作.数据截断模块会对乘加树模块计算出来的数据和Weight RAM里的权重进行截断操作,截断操作会将数据的低三位截断,以方便后续的计算.经行截断以后的数据会进入Stride模块,Stride模块会控制数据是否进行步长的跨度操作.最后数据会进入POOL然后截断输出.

3.3 计算优化策略

基于高速设计和最大化资源利用率的原则,在进行卷积运算时,本设计采用了数据复用、权重共享的方法,特此在数据生成模块加入了Padding、四变三、和三变九功能.在卷积运算中,为了更好地对图像的边界信息进行处理,获取更完整的Feature Map,会对输入图像进行Padding操作,实为补零操作.为了更高的效率,本设计将此功能在FPGA中实现,省去上位机处理和传输数据的时间.

在FPGA内部实现Padding操作,需要借助有限状态机(Finite State Machine,FSM),对一张图片进行补零操作,在每一张图片数据进入时需要补一行零,后续还有左补零和右补零操作,在最后一行又需要补一行零才能完成这一复杂的操作.因此需要使用状态机将电路分成不同的操作状态,同时使用上位机指令进行补零的操控.

在进行Padding操作之后,还需要对输入的数据进行一些数据生成操作.在FPGA中,面对大量的流式数据运算,往往将数据暂存在FIFO当中,再将其取出进行计算操作,常规的卷积3*3操作需要一次对需要进行卷积的9个像素点做点乘操作,我们一次将卷积所需的3行数据传入FIFO,再从FIFO当中依次读出进行计算,但这样做一个时钟只能做第1行、第2行、第3行的一个像素点的点乘,完整一次3*3标准卷积需要3个时钟,速度慢,还会增加后续数据的等待时间,有可能造成数据丢失的问题.

针对这些问题,本次设计对进行卷积之前的数据处理进行了优化,首先设计1个四变三模块,该模块使用4个分布式Ram,分别为ram0、ram1、ram2、ram3,对padding操作完成后的数据进行储存,首先将三行数据分别读入ram0,ram1,ram2在3行数据读满之后,开启一次卷积计算,待3行数据计算的同时,将第4行数据读入ram3,计算完毕之后,使用ram1,ram2,ram3当中的3行数据,再次开启一次卷积计算,同时将第5行的数据读入ram0,以此类推,四变三操作的示意图如图5所示.

图5 四变三操作

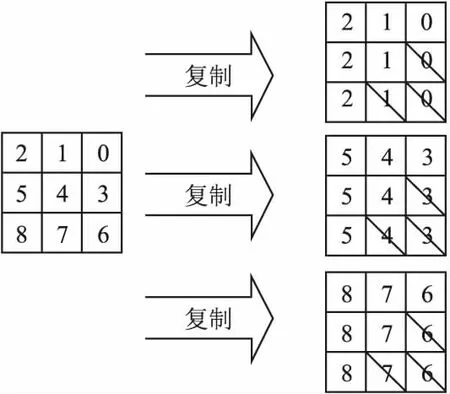

四变三操作增加了数据的复用率,节省了数据准备的时间,极大地加快了卷积运算的效率.经过四变三之后,我们得到了一次卷积计算的三行数据,但是一次3*3卷积计算需要9个像素点方能计算完成,还需要对数据进一步优化处理.为此,本设计采用三变九模块,将传入的每行数据复制3份,在每1行的复制当中,第1次的复制完全保留,第2次的复制去掉第1个数据,第3次的复制去掉前两个数据.三变九模块的示意图如图6所示.

图6 三变九操作

3.4 8bit量化

由于FPGA的电路特性,导致其对浮点数据不能很好地支持.神经网络模型当中绝大部分参数为浮点型,在进行向前推断阶段,会消耗大量的计算资源,不适合使用FPGA进行处理.研究表明,使用8bit,16bit定点数据进行推断,不会损失过多精度,在速度上反而更有优势[16].因此为了更适应FPGA当中部署神经网络,加快模型的推断速度,需要对浮点模型进行数据量化操作.

本次设计采用线性量化,线性量化的公式为:

(1)

其中s是缩放的系数,z代表零点.

XQ=clamp(0,Nl-1,XINT)

(2)

Clamp代表截断操作,Nl由量化所需要的位数决定.在进行卷积运算时,可将原卷积公式转化为下述公式,完成量化操作.

(3)

4 上位机和指令集设计

4.1 上位机流程

本设计的上位机使用Python语言编写,主要涉及视频分帧/抽帧、图像预处理、FPGA数据和计算调度,YOLO后处理和Deepsort跟踪部分.在视频抽帧分帧,图像预处理时,我们会借助OpenCV的函数库来实现,将视频流转化为所需的一帧一帧的图像,再将图像进行一些缩放操作,方便后续计算任务.YOLO后处理包含解码和非极大值抑制等,用来解析检测的结果,消除多余的重叠框.Deepsort算法使用卡尔曼滤波和匈牙利方法对检测结果进行跟踪处理.以上操作均为串行操作,在主机CPU上运行会有极高的效率.

4.2 指令集设计

在FPGA对神经网络进行加速的阶段,FPGA内的数据传输和计算开始、复位等指令,均由上位机发出.为了更方便高效的完成对FPGA的调度,本设计定制了一套精简的AI指令集[17-19].指令集包含对FPGA整体的复位,各个模块的复位、开始信号、数据通路的选择,DMA搬运数据的地址和开始信号,还有一些需要配置的参数如Padding时填零个数,Stride时的步长,都由指令集进行配置.Control寄存器为读写双向,上位机可以通过读写该寄存器,来控制和获得计算模块的当前状态,Switch寄存器为只写寄存器,上位机通过配置该寄存器,可以完成对4种算子的操控,在每层计算开始之前,会配置该寄存器,来选择进行标准卷积、DW、PW、或者是Reshape操作.Config寄存器,为参数寄存器,每次计算所需的特征图数据,和权重数据,都由该寄存器进行配置,该寄存器有四条指令,分别为从DDR中读出的数据数量,读出的数据所在地址,和写入DDR的数据数量,和写入DDR的数据地址.Compute寄存器一共有4组,分别对应12组指令,在每层计算开始之前,会该4组寄存器进行详细配置,计算模块会对计算指令进行解析操作,从而完成计算指令所对应的计算操作,该指令集信息如图7所示.

图7 指令集设计

5 实验结果

5.1 实验设置

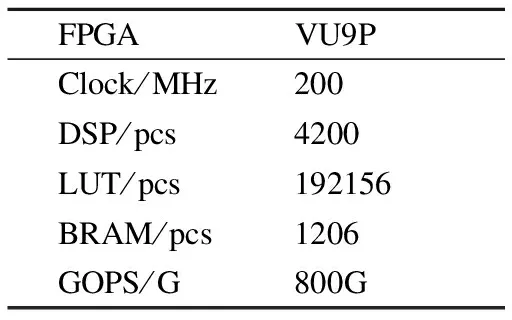

实验使用的目标检测模型为YOLOv5m,数据集为旷世的CrowdHuman数据集[20],硬件方面上,选择Xilinx 的FPGA,芯片为16nm的Virtex UltraScale+VU9P.设计全部采用Verilog HDL语言实现,开发工具为Xilinx 的Vivado 2019.2,计算模块和IP核使用Vivado的block design技术进行连接,并进行综合布线.对照组使用目前主流的GPU NVIDIA GeForce GTX 1080TI和NVIDIA的嵌入式GPU Jetson Xavier.

5.2 资源使用情况

本设计采用的时钟主频为200Mhz,根据YOLOv5m目标检测模型的特点,在FPGA内部实现3*3标准卷积代替YOLOv5m向前推断中的卷积操作,经过优化设计,最终在VU9P板卡中使用的资源情况如表3所示.

表3 VU9P资源使用情况

5.3 YOLOv5m平台性能对比

在两段式目标跟踪系统当中,目标检测的精确度和速度会极大地影响跟踪算法的效果.本文分别在VU9P、GTX 1080TI、Jetson Xavier上使用自己录制的行人视频,在使用CrowdHuman数据集训练好的YOLOv5m模型中,使用480×800的图像输入尺寸进行测试.表4为性能的对比.由于在FPGA当中使用了INT8格式,对比GPU使用的浮点格式,会造成一定的精度损失,但精度仍然只比嵌入式GPU下降3%,但其速度明显快于GTX 1080TI和Jetson Xavier.虽然损失了一定的精确度,但是在部署系的速度和功耗比上,VU9P都要优于GTX 1080TI和Jetson Xavier.

表4 YOLOv5m不同平台性能对比

5.4 跟踪算法性能对比

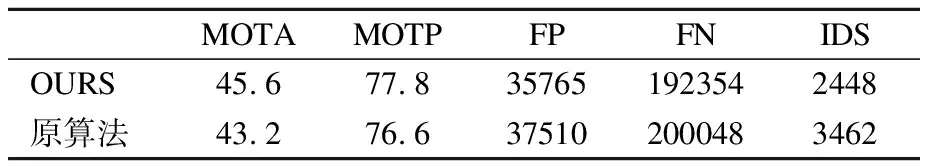

经过YOLOv5m的实验后,继续开发上位机,使系统完善,使用Python复现和改进Deepsort跟踪算法,使用MOT20数据集基于MOT20[21]基准对本跟踪算法进行测试,下载官网数据进行测试.MOT20测试数据集场景多为大量行人,十分拥挤的挑战性测试场景,对跟踪算法的抗遮挡性和目标发生重叠时的处理能力有较大的考察意义.在使用一样的参数和阈值设定下与原Deepsort算法进行对比实验效果如表5所示.

表5 跟踪算法性能对比

通过对比可知,本文经过改进的Deepsort跟踪精度有少量的提升,在轨迹匹配失败时,使用交并比来检测目标是否发生重叠现象,设定阈值,防止目标由于重叠问题发生匹配失败现象,实验结果可知身份编号转变的数值IDS,有较大幅度的降低,证明了本次改进针对遮挡目标和目标消失时的轨迹再匹配有一定程度的改善,避免了部分目标丢失的情况.

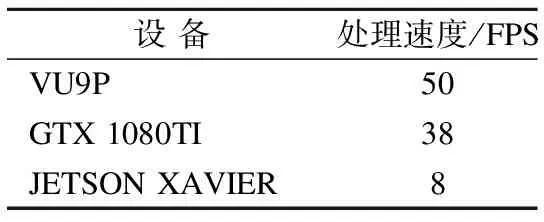

5.5 整体性能对比

对接上位机与改进后的跟踪算法,使异构系统可以完整的运行YOLOv5m+Deepsort.使用自己录制的行人视频进行测试,同时在GTX 1080TI、Jetson Xavier进行同样的实验.测试服务器CPU为Inter I9 7960,图像缩放尺寸为480×800,测试处理结果抛去权重加载,视频图像预处理的时间,只测试设备处理所有视频帧到跟踪算法输出结果的时间.实验结果如表6所示.经测试该系统可以达到实时处理效果.

表6 跟踪系统不同平台性能对比

6 总 结

本文针对目标跟踪部署在资源受限的移动平台中遇到的功耗问题和实时性需求,设计并集成了一种基于FPGA的神经网络异构加速跟踪系统.在硬件层面基于卷积神经网络特点设计卷积加速器结构,可以实现在低功耗条件下进行卷积算法的加速.在算法层面上改进Deepsort跟踪算法达到更好的跟踪效果.在系统层面上创新性的结合了当下流行的目标检测算法YOLOv5和在线目标跟踪框架Deepsort,使用8bit定点数据并根据软硬件协同优化设计的方法合理分配计算任务,完成跟踪算法的异构加速部署,系统处理速度可以达到实时水平,满足在资源受限平台上的部署.