面向安全持久性内存的元数据协同管理方法

魏学亮 杨明顺 冯 丹,2 刘景宁,2 吴 兵 肖仁智 童 薇,2

1(武汉光电国家研究中心(华中科技大学) 武汉 430074) 2(华中科技大学计算机科学与技术学院 武汉 430074)

近年来,新型非易失存储器(non-volatile memory, NVM),例如自旋转移矩磁阻式随机存取存储器(spin-torque transfer RAM, STT-RAM)[1]、相变存储器(phase change memory, PCM)[2]、电阻式随机存取存储器(resistive RAM, ReRAM)[3],受到来自学术界和工业界越来越多的关注.相比传统存储设备,例如机械硬盘(hard disk drive, HDD)和固态硬盘(solid state drive, SSD),NVM具有访问延迟低、字节可寻址的优点.相比传统DRAM内存,NVM具有存储密度高、静态功耗低、非易失的优点.这些优点使得NVM可以被放置在内存总线上作为持久性内存(persistent memory, PM)使用.PM允许应用直接通过访存指令,而不用经过传统存储栈访问持久化数据,从而减少持久化数据访问开销.

目前使用NVM构建高效安全的PM系统依然面临诸多挑战.首先,PM系统需要保证数据的安全性.现有研究工作表明,内存系统容易遭受恶意攻击影响[4-5],例如总线监听、内存窃取、重放攻击.攻击者可以通过未授权读写操作获取或篡改内存中重要数据.为防止攻击者获取内存中的数据,需要对数据进行加密.一种被广泛使用的加密技术为计数器模式加密(counter-mode encryption)[6-9].该加密技术为每个数据块维护1个加密计数器,用于计算加密所需的一次性填充数据(one-time pad, OTP).为防止攻击者篡改内存中数据,需要对数据进行完整性保护.常用的完整性保护技术包括在加密计数器上建立的完整性检测树[5,10],以及根据数据块和计数器生成的消息鉴别码(message authentication code, MAC)[5].

其次,PM系统需要解决NVM写性能和耐久性较差的问题.近期研究工作表明,NVM的写延迟约为读延迟的3~8倍[11],并且耐久性仅为107~108次写操作[12].为了减少写延迟并提升寿命,位级写缩减技术[13-14]被广泛应用于未加密NVM,以减少数据写入NVM时造成的位翻转(即0变1或1变0).然而,由于加密算法的雪崩效应[6,8,11,15],这些位级写缩减技术不适用于加密NVM.因此,近期研究工作提出选择重加密策略[6,8],以优化加密NVM的写操作.这类策略将数据块划分为细粒度的数据片,并为每个数据片维护局部计数器,用于在数据写回NVM时仅重新加密并写入被修改的数据片.

为解决使用NVM构建PM系统的各种挑战,多种元数据被引入到PM系统中,例如加密计数器、完整性检测树、MAC、局部计数器.如果将这些元数据独立存放在NVM中不同区域,则会显著增加NVM访问开销.例如,从NVM读取1个数据块时,不仅需要读取加密计数器和局部计数器对数据块解密,还需要读取完整性检测树和MAC进行完整性验证.为加速元数据的访问,许多研究工作在处理器中添加片上元数据缓存[7,11].然而,元数据缓存只能缓存小部分元数据.当缓存不命中时,依然需要从NVM中读取元数据,从而造成额外的NVM访问开销.因此,近期研究工作提出各类元数据管理方法[7,10,16-17],以减小元数据访问造成的开销.

然而,我们发现现有的元数据管理方法仅考虑部分元数据,依然存在较大的元数据访问开销.例如,MorphCtr[7]未针对写性能和耐久性相关元数据进行优化,使得数据块访问依然需要在关键路径上等待这些元数据的读取.具体地,当其与选择重加密策略Nacre[8]协同工作时,我们通过实验观察到17.3%的性能开销和59.6%的额外NVM访问,并且额外访问中68.4%为对写性能和耐久性相关元数据的访问.此外,我们通过实验还发现,对于不同应用,数据块中不同字节存在不同修改频率,并且修改频率存在一定规律.然而,现有的选择重加密策略采用的静态数据分片策略无法充分利用这些规律,从而在数据块写入NVM时造成额外的位翻转.

为解决上述问题,本文提出一种面向安全PM的元数据协同管理方法(coordinated metadata man-agement for secure PM, COTANA).为减少元数据访问开销,COTANA将相同数据块的写性能和耐久性相关的元数据与加密计数器整合在相同元数据块中,使得元数据缓存未命中时仅需1次额外的NVM访问就可以获取加解密所需的全部元数据.COTANA基于上述元数据块建立完整性检测树,并利用完整性检测树优化策略[7,10]减小存储开销,从而增加元数据缓存命中率,进而减少额外的NVM访问.此外,COTANA采用ECC(error-correcting code)内存架构组织PM,并将MAC存放在ECC芯片中,使MAC访问可以与数据块访问并行执行,从而避免MAC访问造成的延迟.为减少写开销并提升NVM寿命,我们根据数据块中字节修改频率的规律设计一种聚集分片方法.COTANA采用动态数据分片策略,从聚集分片方法和现有的连续分片方法中动态地选择造成位翻转最少的方法,从而减少位翻转.

本文的主要贡献有3个方面:

1) 观察发现真实应用所修改的数据块中,不同字节有着不同修改频率,且修改频率存在规律.根据此规律提出一种聚集分片方法,以减少位翻转.

2) 提出一种面向安全PM的元数据协同管理方法COTANA,通过精心组织各类元数据减少元数据访问开销,通过动态数据分片策略减少写开销并提升NVM寿命.

3) 在Gem5[18]上对COTANA进行实验测试.测试结果显示,与采用最新的元数据管理方法[7]和选择重加密策略[8]的系统相比,COTANA最多能提升13.7%的性能,并减少21.3%的位翻转.

1 背景及动机

1.1 新型非易失存储器

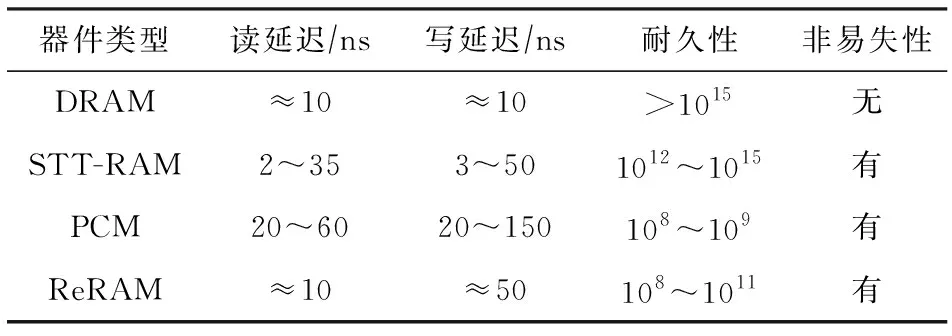

过去几十年以来,DRAM一直是计算机系统内存的首选.然而,近期DRAM的发展面临工艺尺寸难以进一步缩小的难题[19].因此,NVM获得来自学术界和工业界越来越多的关注.表1列举了DRAM和典型NVM器件的主要特征对比.NVM有着非易失性以及接近DRAM的读延迟,但是写延迟远高于读延迟,并且写耐久性远低于DRAM.因此,NVM可以放置在内存总线上作为PM使用,但是需要解决NVM写延迟高和耐久性差的问题.

Table 1 Comparison of Characteristics Between DRAM and NVM Devices[20]

1.2 威胁模型

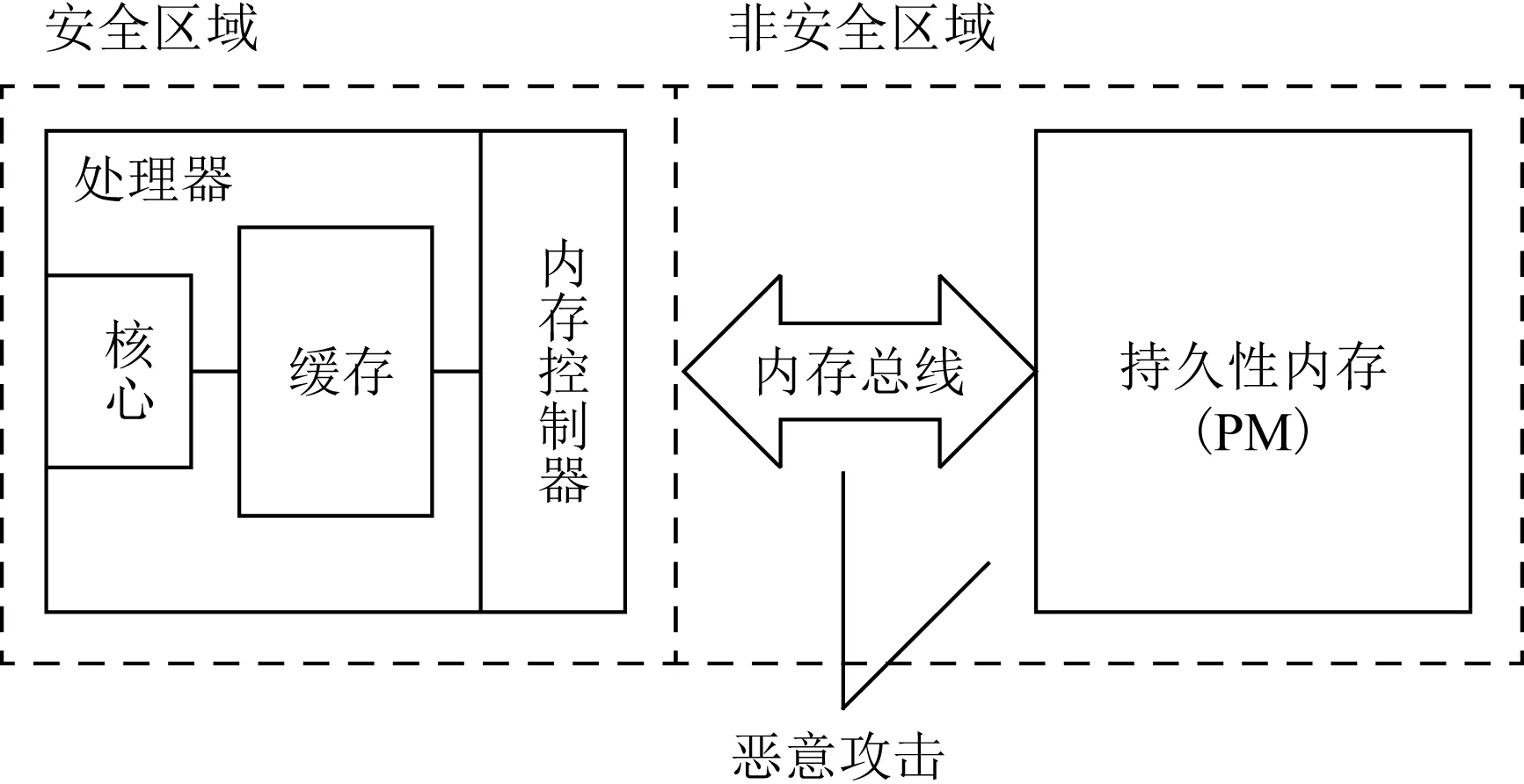

内存系统容易遭受多种恶意攻击的威胁,导致重要数据被攻击者获取或篡改[4-5,21].此外,相比易失的DRAM,PM在系统断电后依然能长时间保存数据,使得PM系统面临着更为严峻的安全问题.

本文基于图1所示的威胁模型研究PM系统的安全问题.该模型已在许多研究工作中被广泛使用[7-11,16,21-23].在该模型中,处理器为可信计算基(trusted computing base, TCB),即所有处理器片上组件(例如核心内的寄存器、缓存、内存控制器)均位于安全区域,无法被攻击者窃取或篡改.而所有的处理器片外资源均位于非安全区域.攻击者可以监听或篡改内存总线上传输的数据,也可以读取或修改PM中的数据.本文不考虑推测执行攻击[24]、侧信道攻击[25]等攻击方式.这些攻击方式可以通过现有研究工作提出的方法[24-25]进行防御,并且这些研究工作与本文是正交的.

Fig. 1 Threat model图1 威胁模型

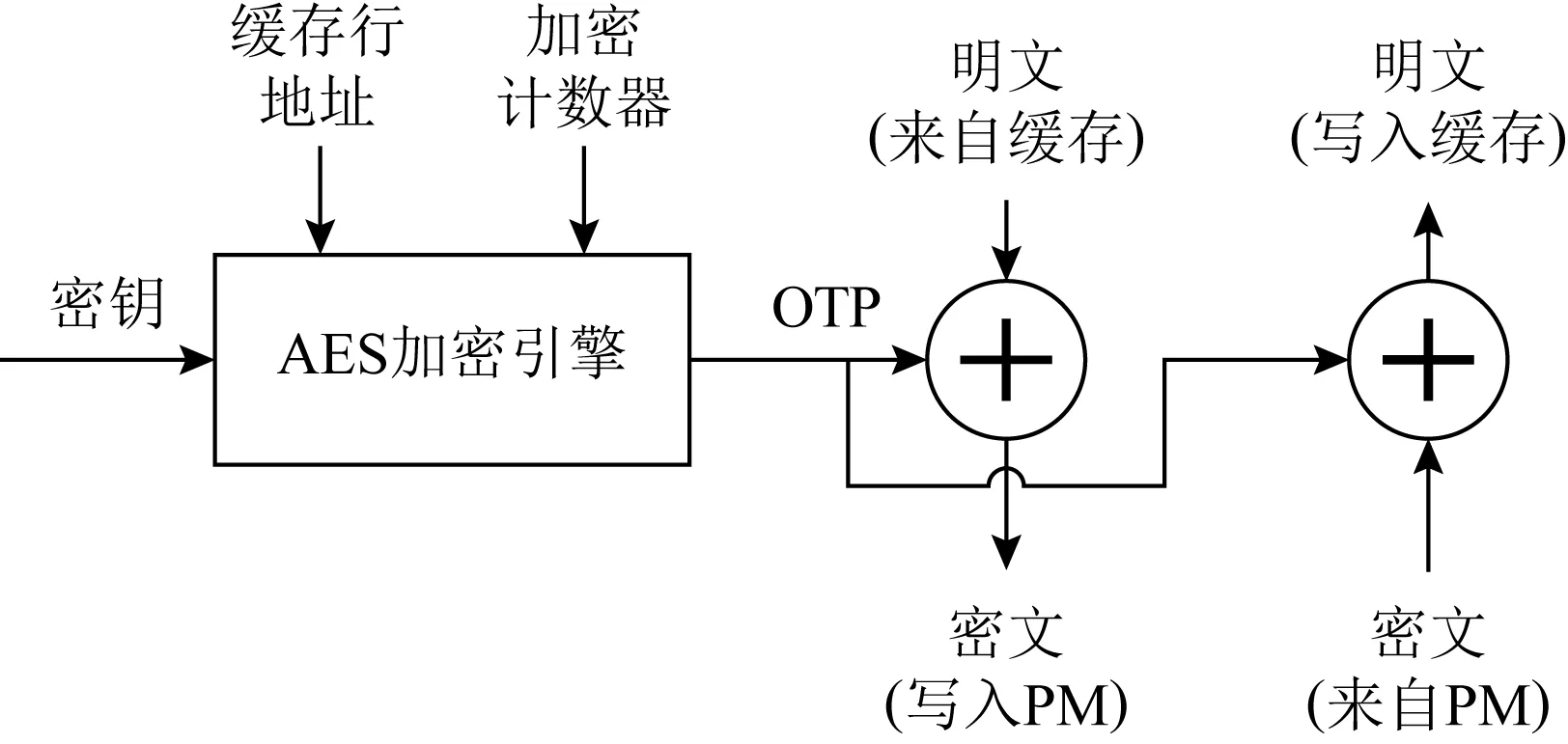

1.3 计数器模式加密

为防止攻击者从内存总线或PM窃取数据,处理器需要在向PM发送数据前对数据进行加密.而计数器模式加密[6-11]是目前被广泛使用的加密技术之一.如图2所示,计数器模式加密在PM中为每个缓存行大小的数据块维护1个加密计数器,并在每次将数据块从缓存写回PM时增加计数器的值.执行加密时,首先将密钥、缓存行地址、加密计数器输入加密引擎,例如高级加密标准(advanced encryption standard, AES)加密引擎;然后,加密引擎根据输入数据生成OTP;最后,将OTP与缓存行异或得到密文,并将密文发送给PM.执行解密时,首先生成OTP并同时从PM中读取密文,再通过将OTP与密文异或得到明文.

Fig. 2 Counter-mode encryption图2 计数器模式加密

1.4 完整性检测

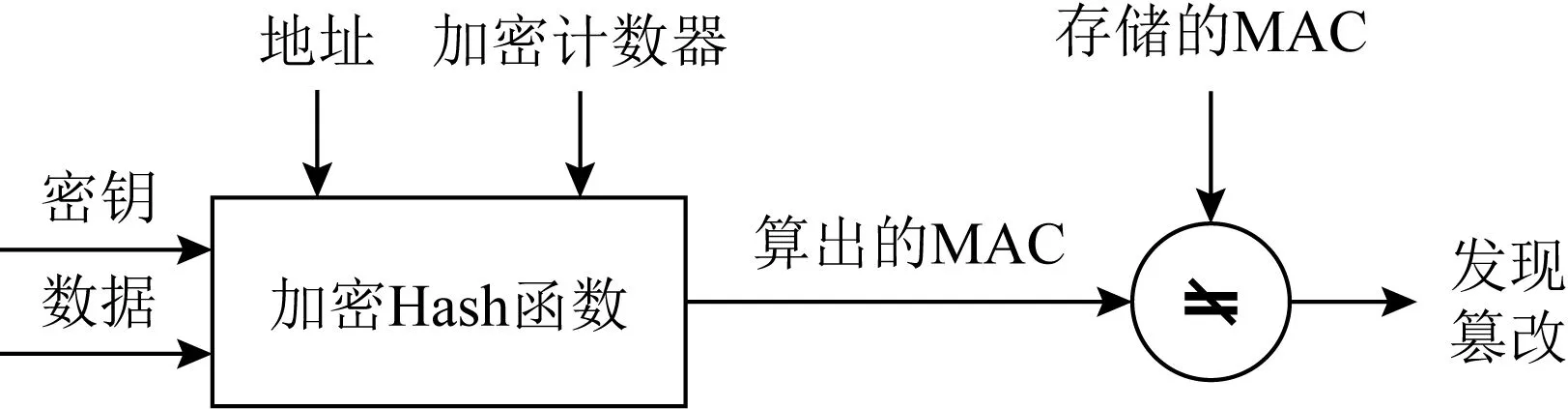

为防止攻击者篡改内存总线上或PM中的数据,需要采用完整性检测技术保证数据的完整性.一种被广泛使用的完整性检测技术是MAC[5,16,21].如图3所示,将数据、密钥、地址、加密计数器作为加密Hash函数(例如AES-GCM[26])的输入可计算得到MAC.当数据写回PM时,算出的MAC和数据一同写回PM.而当数据读出PM时,重新计算MAC,并将算出的MAC和PM中存储的MAC进行比较,如果两者不相同,则数据或加密计数器被篡改.

Fig. 3 Data integrity verification with MAC图3 通过MAC验证数据完整性

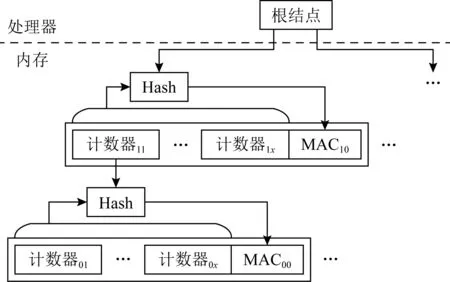

然而,仅靠MAC无法完全保证数据的完整性,攻击者依然可以通过重放攻击等方式篡改数据.例如,假设PM中的初始数据为{数据0,加密计数器0,MAC0},并且正常应用将其更新为{数据1,加密计数器1,MAC1}.如果攻击者将数据替换为{数据0,加密计数器0,MAC0},那么仅通过MAC无法发现数据篡改.为解决此问题,通常将加密计数器所在的块作为叶子结点构建完整性检测树,例如默克尔树[5,27]和SGX风格的完整性检测树(简称为SGX树)[7,10].如图4所示,SGX树的根结点存放在处理器中以防攻击者篡改.每个结点块中包含计数器和MAC.其中,MAC(例如MAC00)由结点块中所有计数器(例如计数器01到计数器0x)以及父结点中的1个计数器(例如计数器11)作为输入通过Hash得到.如果任意非根结点被篡改,则计算得到的MAC与结点块中存放的MAC不匹配,从而发现篡改.

Fig. 4 SGX-style integrity verification tree图4 SGX风格的完整性检测树

1.5 选择重加密

Fig. 5 Avalanche effect of encryption图5 加密的雪崩效应

如表1所示,相比DRAM,NVM有着较差的写延迟和耐久性.为了优化NVM的写性能并提升寿命,位级写缩减技术[13-14]被广泛用于减少数据写入NVM时造成的位翻转,从而增加写并行性并减少存储单元磨损.例如,FNW(flip-n-write)[13]在写操作造成的位翻转超过数据块大小一半时,先对数据块中所有的位进行翻转,再将发生翻转的位写回PM,从而将位翻转减少至数据块大小一半以下.然而,由于加密算法存在雪崩效应[6,8,11,15],这些位级写缩减技术不适用于加密NVM.雪崩效应指,即使只修改明文中的1 b数据也会造成密文中超过半数的位发生变化.例如,如图5所示,对于未加密NVM,数据在经过FNW处理后仅需修改1 b数据.而对于加密NVM,雪崩效应使得无论是否经过FNW处理均需要修改超过1 b数据.

为优化写性能并提升寿命,一些研究工作针对加密NVM提出选择重加密技术[6,8,28].该技术将每个数据块划分为细粒度的数据片,并在数据块写回PM时只将被修改的数据片采用新计数器重新加密并写回.例如,如图6所示,Nacre(8,4)[8]将数据块划分为大小为8 B的数据片并分配4个局部计数器.此外,为每个数据片维护2 b计数器指示器,以指示被用于加密该数据片的局部计数器.当新数据写回PM时,首先对比新旧数据确定被修改的数据片(例如分片1,3,4),然后将新的局部计数器(例如局部计数器1)和加密计数器拼接起来对被修改的数据片进行加密,最后仅将重加密后的数据片写回PM.

Fig. 6 Example of selective reencryption图6 选择重加密示例

1.6 开销分析

为构建高效安全PM系统,加密、完整性检测、选择重加密技术引入多种元数据,例如加密计数器、MAC、完整性检测树、局部计数器.这些元数据分别存放在PM中的不同位置,使得在访问PM中的数据块时需要额外执行多次元数据访问操作.例如,当从PM读取数据块时,需要读取加密计数器和局部计数器对数据块进行解密,还需要读取MAC和完整性检测树来验证完整性.为加速元数据访问,许多研究工作[7,11,17,22]在处理器中添加元数据缓存,并对元数据管理方法进行优化.例如,将每个加密计数器块分为1个主计数器和多个大小可变的从计数器[7],从而增加每个块存放的计数器的数量,使得元数据缓存有更高的命中率.因为SGX树的每个结点中也包含计数器,所以增加每个块的计数器数量还可以降低树的高度和大小,从而减少完整性检测树造成的开销.

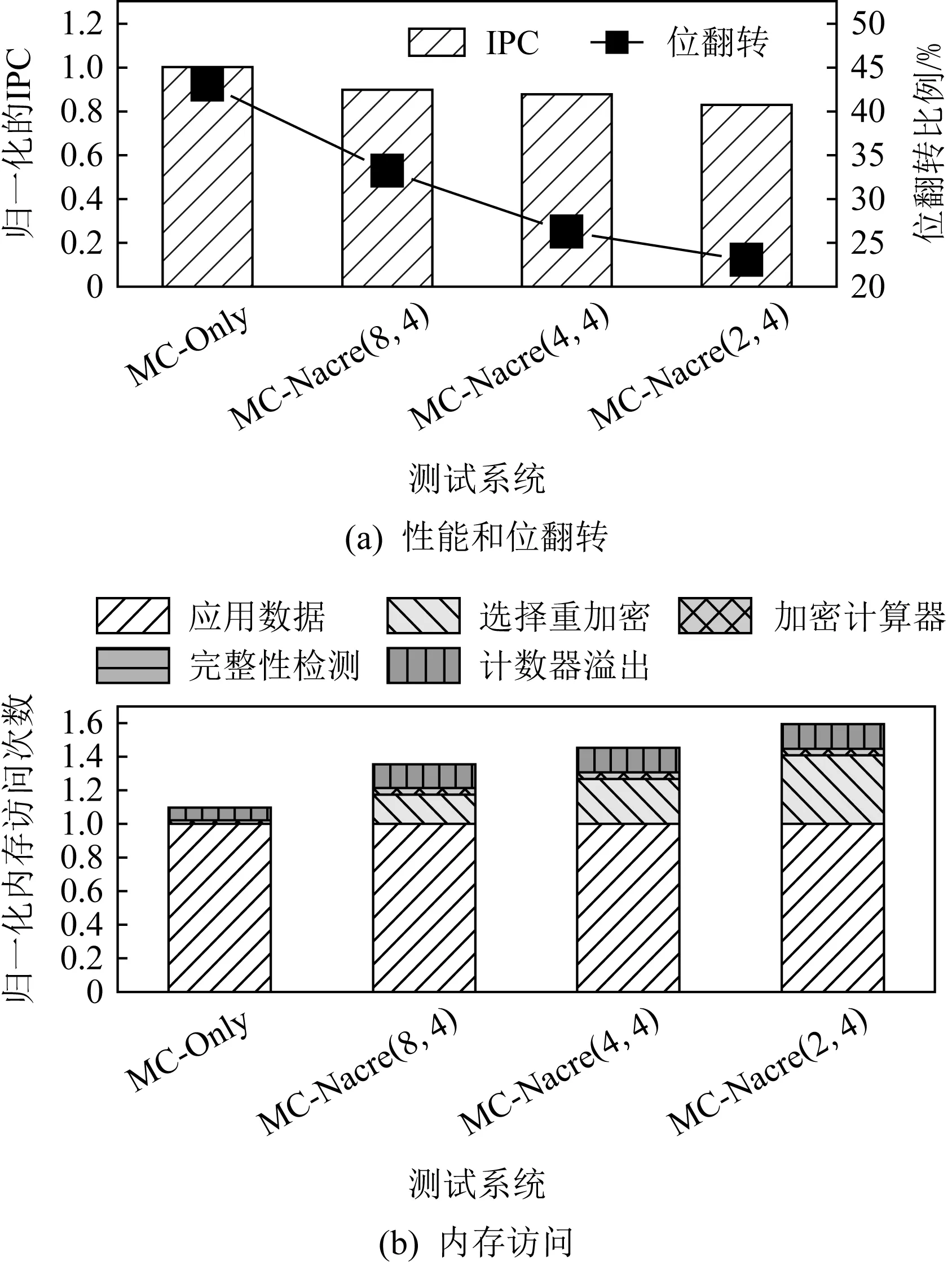

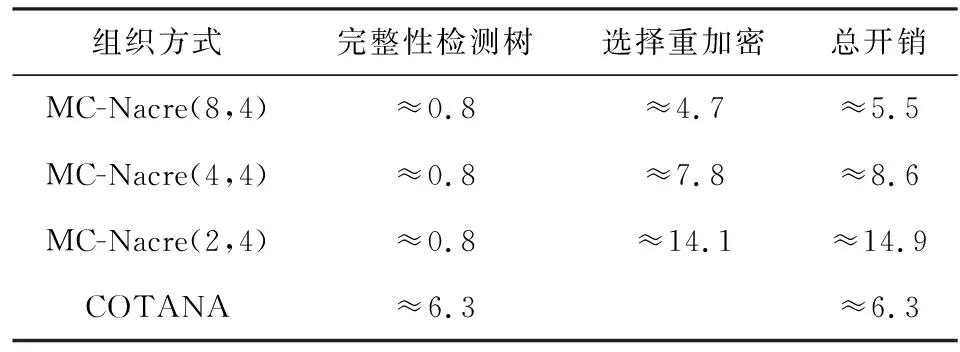

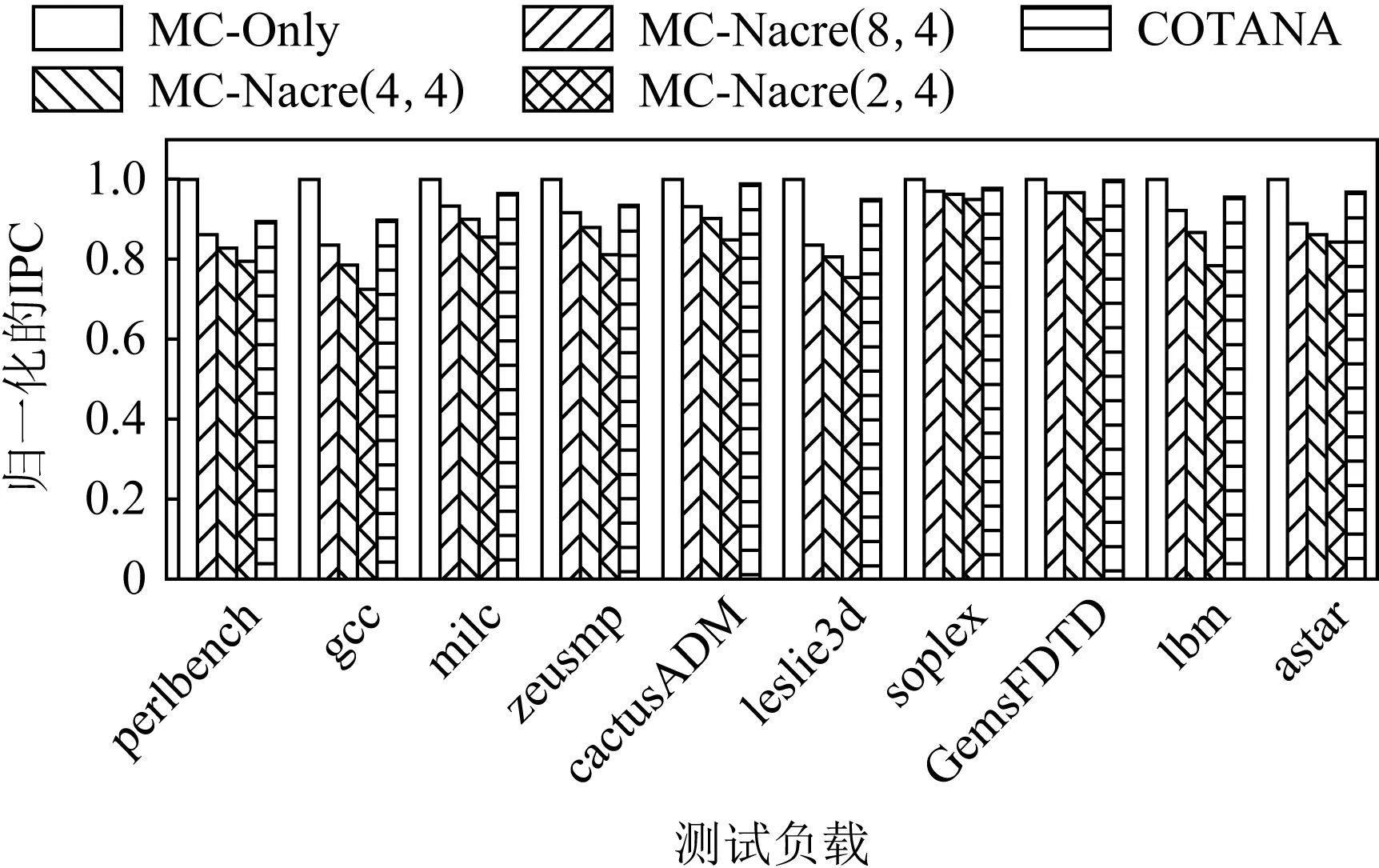

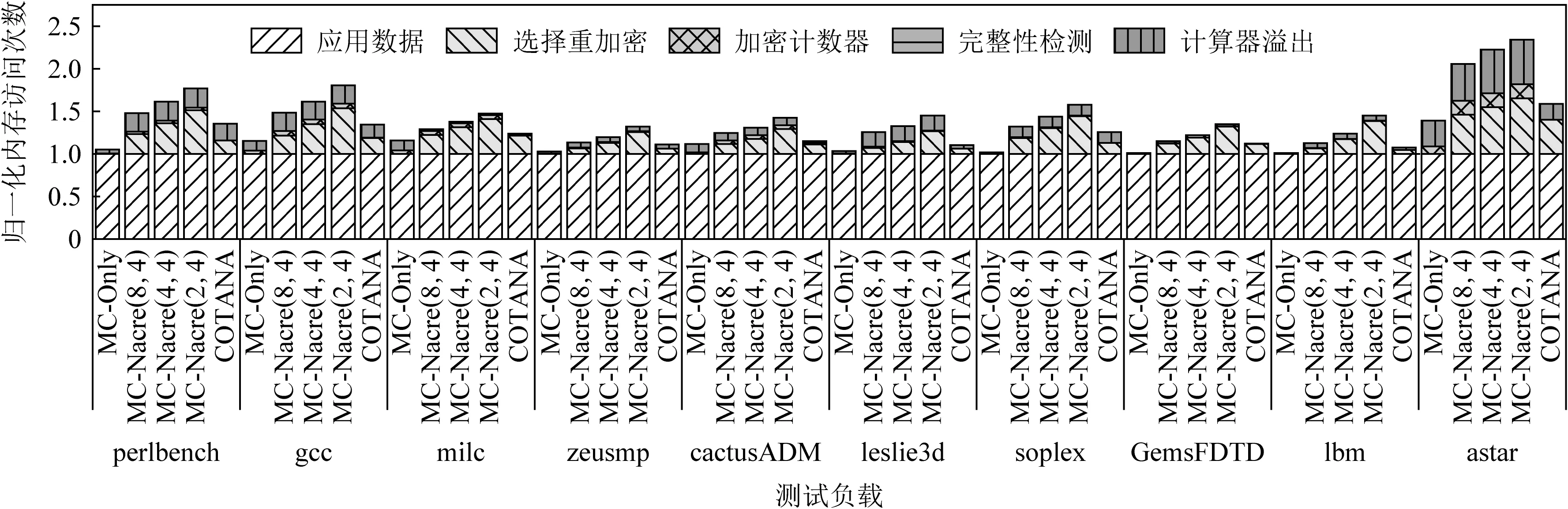

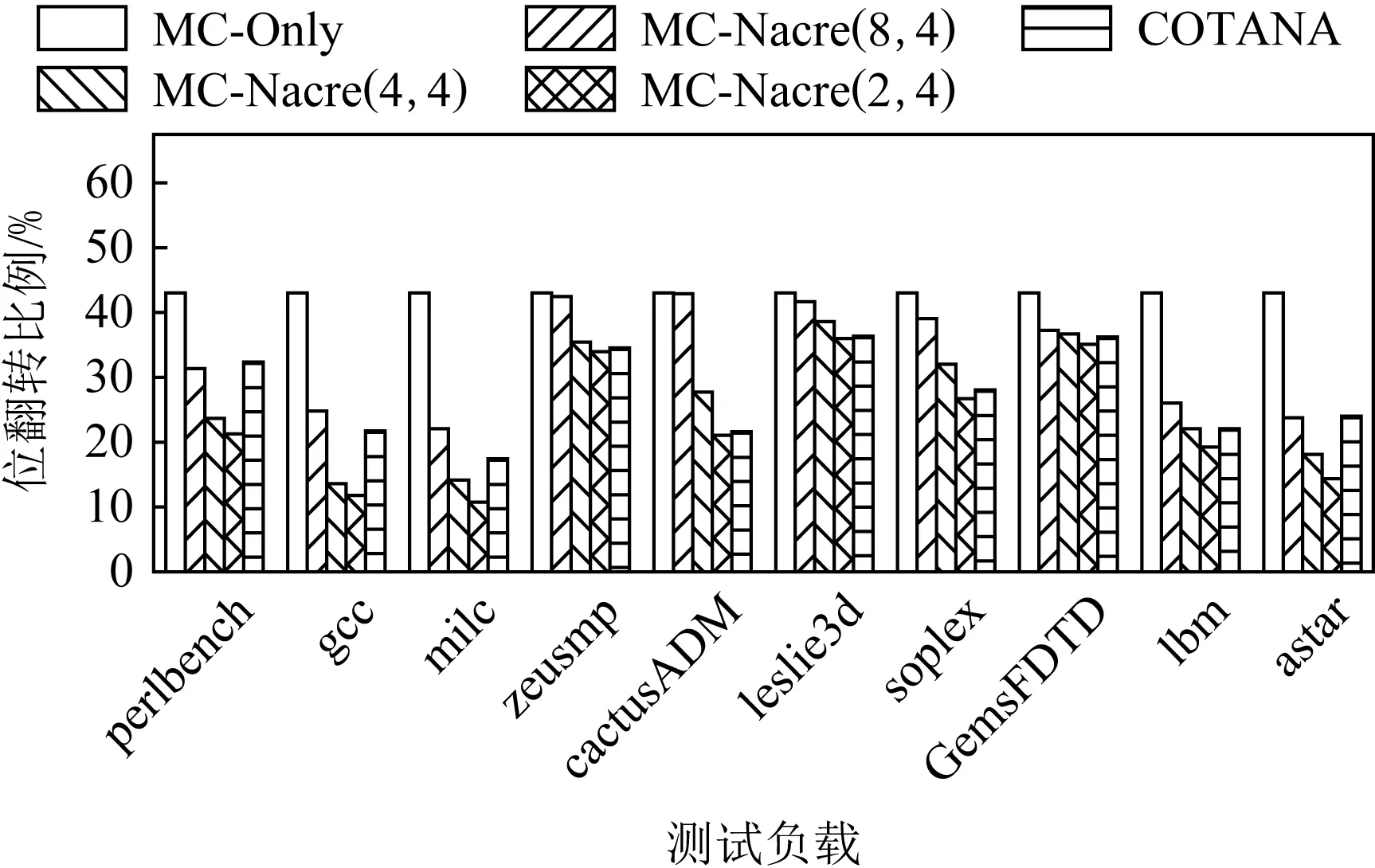

然而,现有的元数据管理优化方法仅考虑部分元数据.使用这些优化方法管理加密、完整性检测、选择重加密技术引入的所有元数据依然存在显著开销.为量化此开销,我们对元数据管理方法MorphCtr[7]和选择重加密技术Nacre[8]进行了实验分析.其中,MorphCtr允许每个块中计数器数量根据负载需求变化,但仅针对加密和完整性检测元数据进行优化.而Nacre将数据分片后使用新的局部计数器对被修改的分片重新加密,如图6所示.实验中我们对4个系统进行对比:MC-Only采用MorphCtr管理元数据,但不执行选择重加密;MC-Nacre(8,4),MC-Nacre(4,4),MC-Nacre(2,4)采用MorphCtr管理元数据,并采用相应的Nacre执行选择重加密.如图7(a)所示,MC-Nacre(8,4),MC-Nacre(4,4),MC-Nacre(2,4)相比MC-Only分别减少9.8%,16.8%,20.0%的位翻转,同时分别造成10.4%,12.4%,17.3%的性能下降.图7(a)的纵轴含义中IPC表示每周期执行的指令数(instruction per cycle, IPC).如图7(b)所示,越细粒度的数据分片方法造成的额外内存访问越多.MC-Nacre(2,4)会造成59.6%的额外内存访问,并且额外内存访问中68.4%为对选择重加密元数据的访问.因此,性能开销主要源于对选择重加密元数据的访问,而现有的元数据管理方法无法高效地管理加密、完整性检测、选择重加密技术引入的全部元数据.

Fig. 7 Analysis of metadata access overhead图7 元数据访问开销分析

2 COTANA元数据协同管理方法

2.1 总体架构

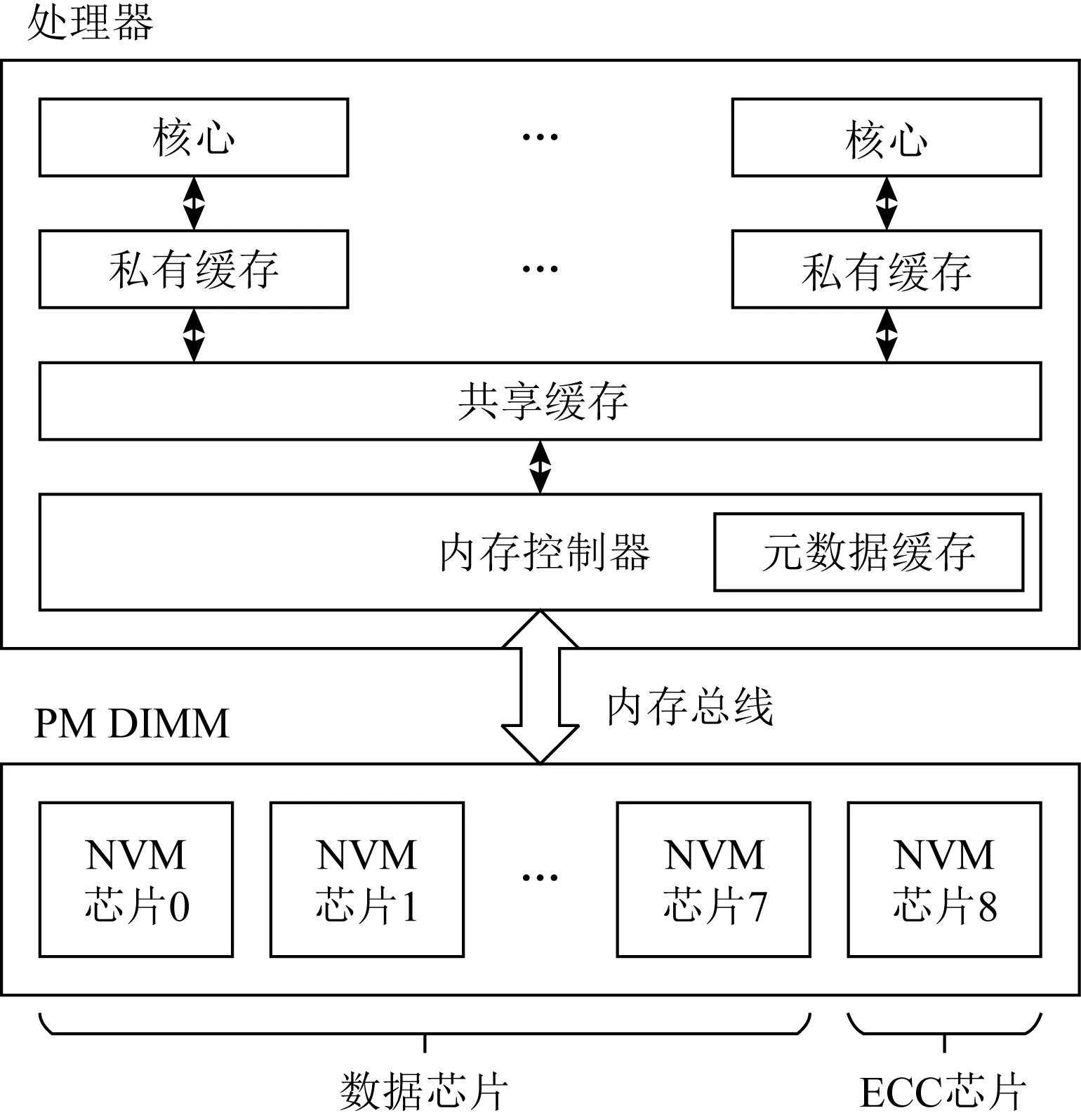

为高效管理加密、完整性检测、选择重加密技术引入的元数据,本文提出一种面向安全PM的元数据协同管理方法COTANA.图8所示为COTANA的硬件架构.其中,NVM芯片以ECC内存架构组织成PM DIMM(dual inline memory module).PM DIMM的每个rank包括9颗可并行访问的NVM芯片,其中8颗为数据芯片和1颗为ECC芯片.处理器通过内存总线与PM相连,并通过内存控制器控制PM执行读写等操作.内存控制器中包含1个元数据缓存.当读写PM中的数据时,内存控制器首先从元数据缓存中读取加密计数器、局部计数器等元数据对数据进行加密或解密.如果元数据缓存未命中,则从PM中读取相应元数据至元数据缓存.从PM中读取任意数据或元数据时,均需要进行完整性检测,故完整性检测相关元数据也需要读取至元数据缓存.

Fig. 8 Hardware architecture of COTANA图8 COTANA硬件架构

2.2 元数据协同管理

基于图8所示的硬件架构,元数据可以存放于数据芯片或ECC芯片.ECC芯片中的元数据可以与数据芯片中的数据并行访问,从而隐藏元数据访问延迟.然而,ECC芯片容量有限,需要确定将哪些元数据存放于ECC芯片才能最小化元数据开销.

假设内存总线宽度为72 b(64 b数据和8 b ECC),且数据块大小为64 B,则读取数据块时可从ECC芯片并行读取64 b元数据.完整性检测树结点因为按照64 B块粒度组织,所以不适合存放于ECC芯片.加密计数器和选择重加密元数据需要在读取数据前缓存在元数据缓存中,使OTP生成与数据读取并行执行以减少解密延迟,故不适合存放于ECC芯片.而MAC的大小通常小于64 b,并且只用于在读取数据后检测完整性,无需与其他元数据竞争元数据缓存.此外,由于MAC相比ECC有更强的检错能力,故可以将MAC放置在ECC芯片中代替ECC进行检错,仅当错误发生时再读取ECC进行纠错.ECC信息可以与MAC一同存放于ECC芯片(54 b MAC和10 b ECC信息)[7],也可以单独放置在数据芯片中(64 b ECC信息)[16].COTANA选择将数据块的MAC和ECC信息一同存放于ECC芯片.

COTANA按照图9所示结构对于加密计数器、完整性检测树、选择重加密元数据进行组织.其中,内部结点采用现有的完整性检测树优化方法[7,10]进行组织,而叶子结点采用分离计数器策略[5]组织加密计数器,以利用计数器访问局部性提高元数据缓存命中率.分离计数器策略在每个元数据块中存放1个主计数器和多个从计数器.每个从计数器对应1个数据块.每当数据块写回内存时,通过主从计数器拼接得到的计数器对数据块进行加密,并且增加对应从计数器的值.当从计数器溢出时,增加主计数器的值并重置该主计数器对应的所有从计数器,同时对所有从计数器对应的块进行重加密.当主计数器溢出时,需要修改加密密钥,并对整个内存进行重加密.为进一步降低元数据访问开销,COTANA将主从计数器与相应的选择重加密元数据放置在相同元数据块中并作为完整性检测树的叶子结点,使得1次访存操作可以获取加解密所需的全部元数据.此外,COTANA将叶子结点的MAC也存放于ECC芯片,从而在每个叶子结点中为选择重加密元数据提供更多存储空间.由于COTANA通过对完整性检测树的叶子结点(即加密计数器所在的元数据块)重新组织来降低元数据访问开销,故COTANA不仅适用于SGX树也适用于叶子结点为加密计数器的默克尔树.

Fig. 9 Metadata management of COTANA图9 COTANA元数据组织方式

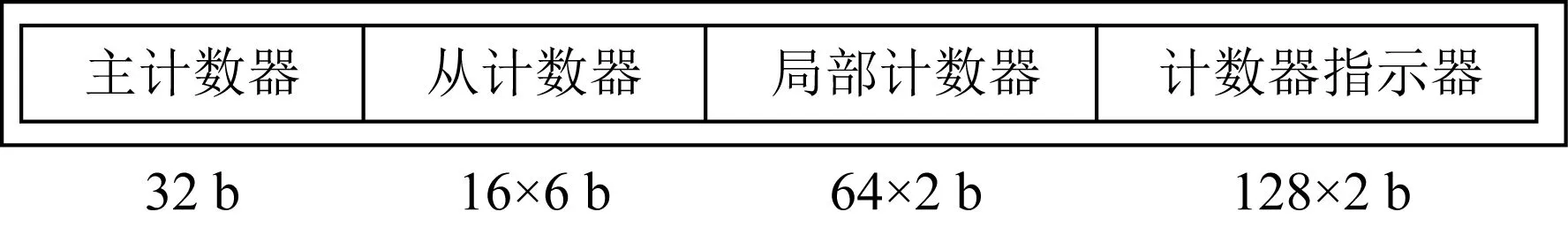

在图9所示的元数据组织方式中,叶子结点的具体实现取决于选择重加密策略.例如,图10所示为采用选择重加密策略Nacre[8]时叶子结点的结构.每个叶子结点包含1个32 b主计数器和16个6 b从计数器,即每个叶子结点对应16个数据块.由于每个数据块被划分为8个数据片,故每个数据块对应8个计数器指示器,而每个叶子结点需要包含16×8=128个计数器指示器.假设每个数据块对应的局部计数器数量为N,则每个计数器指示器的大小为lbN.根据结点中除主从计数器外剩余空间大小,可以为每个数据块分配4个2 b局部计数器,即总共16×4=64个局部计数器,并且每个计数器指示器的大小为2 b.

Fig. 10 Example of leaf nodes with Nacre图10 采用Nacre时的叶子结点示例

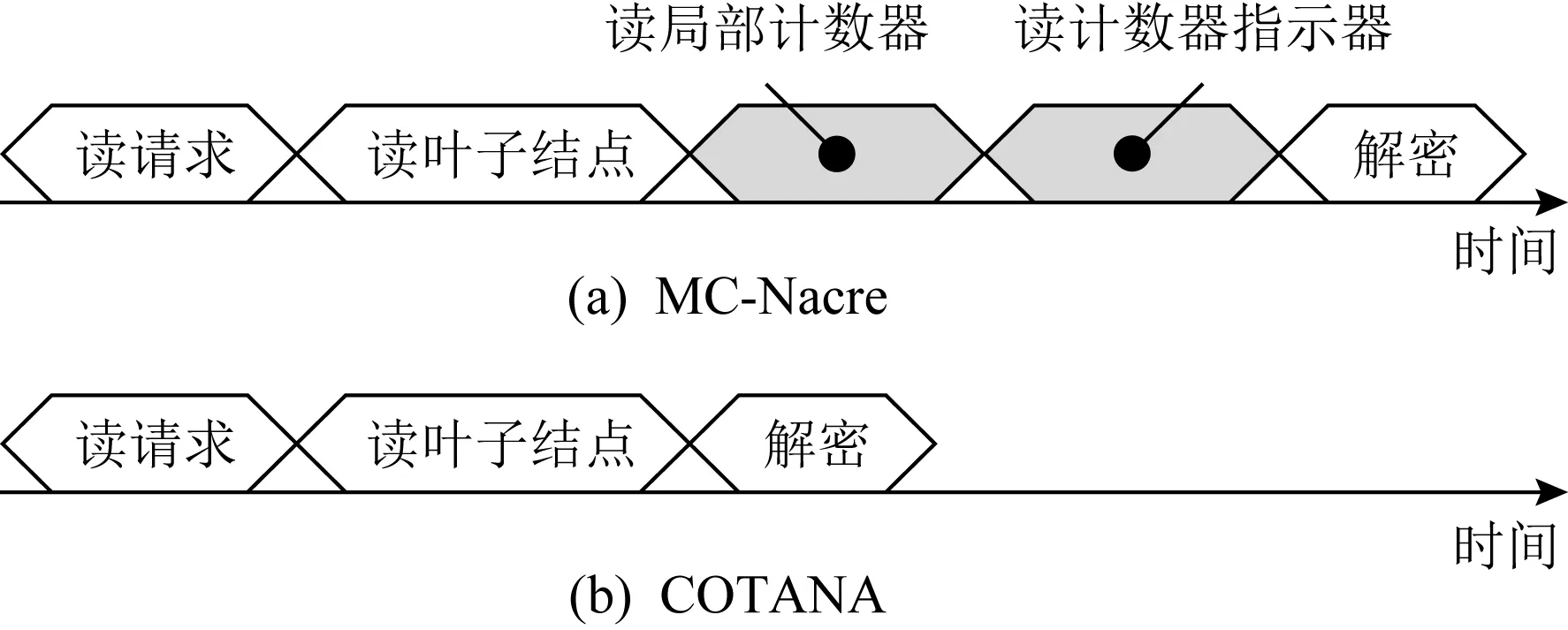

图11所示为采用Nacre[8]作为选择重加密策略时MorphCtr[7](即MC-Nacre)和COTANA的内存读操作执行流程对比.MC-Nacre将加密计数器放置在完整性检测树的叶子结点中,而将局部计数器和计数器指示器分离地存放在内存中.因此,当元数据缓存未命中时,最差情况需要在读操作的关键路径上执行额外3次访存操作,以读取叶子结点、局部计数器、计数器指示器.而COTANA通过元数据协同管理将数据解密所需元数据组织在相同叶子结点中,从而减少额外的访存操作.

Fig. 11 Comparison of read operation processes图11 读操作执行流程对比

2.3 动态数据分片

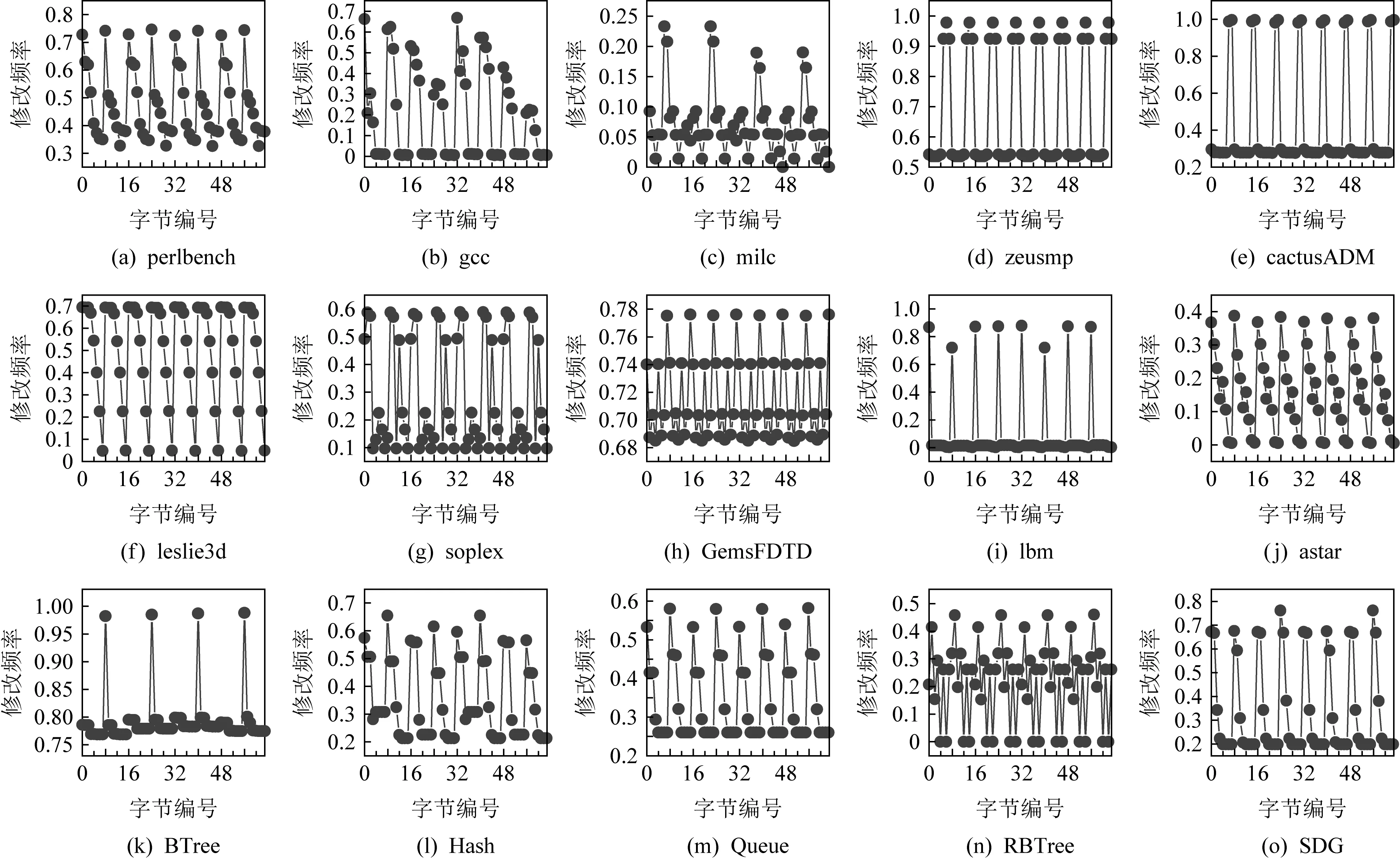

现有选择重加密策略在对数据分片时广泛采用静态的连续分片方法[6,8,28],将地址连续的字节划分至相同数据片.例如,假设数据块大小为64 B,并且将每个字节按照地址从低到高分别记为字节i(i=0,1,…,63).如果将数据块划分为8个数据片,则数据片m(m=0,1,…,7)包含字节8m到字节8m+7.当完成数据片划分后,如果数据片中存在被修改的数据,则需要使用新的计数器对数据片重新进行加密.然而,采用静态数据分片策略时,可能出现每个数据片中仅1 B数据被修改而导致重加密整个数据块的情况.为量化这种情况发生的概率,我们采用SPEC CPU2006负载集[29]和持久性数据结构负载集[30]来统计内存写操作的各个字节的修改频率(字节的修改频率=该字节的修改次数/内存写操作总数).图12所示为不同负载下的测试结果.我们发现如果采用连续分片方法,每个数据片中总是存在部分字节的修改频率显著高于其他字节.因此,连续分片方法会导致未被修改的字节因少部分频繁修改的字节而重加密,从而无法有效地降低加密带来的写性能和耐久性影响.

Fig. 12 Modification frequency of different bytes in data blocks图12 数据块中不同字节的修改频率

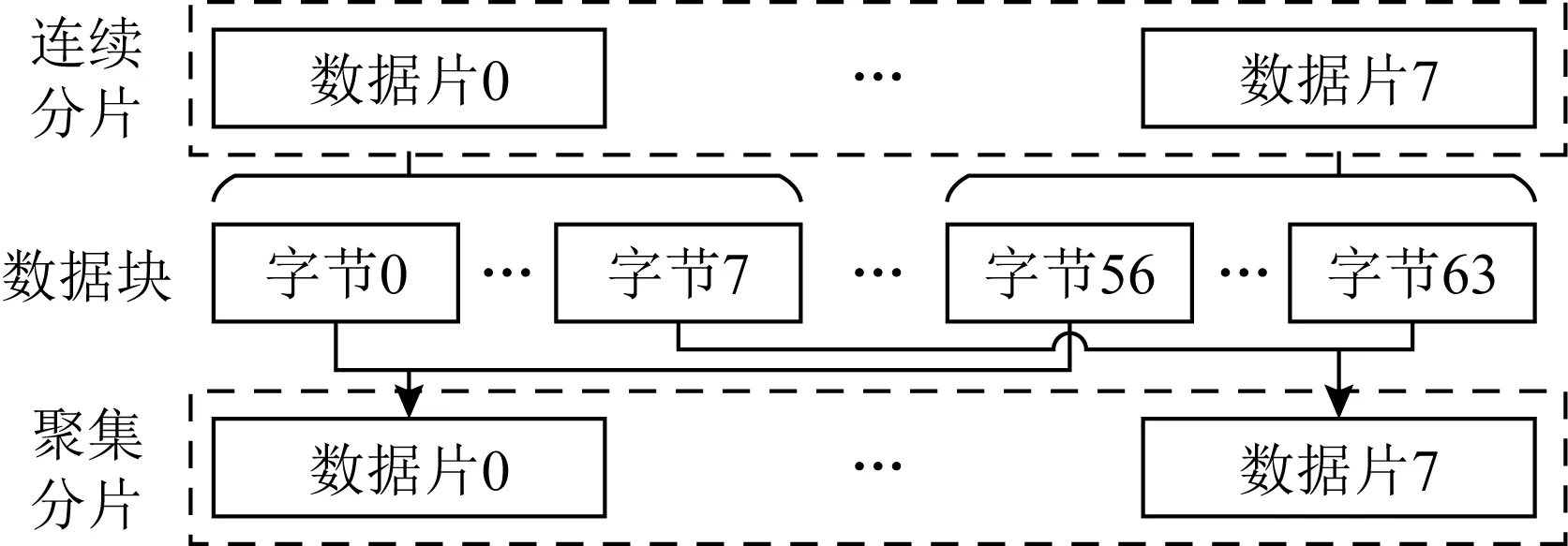

为解决此问题,COTANA采用动态数据分片策略,以从不同的分片方法中动态地选择造成位翻转最少的方法.如图13所示,动态数据分片策略可选的分片方法包括连续分片方法和聚集分片方法.其中,聚集分片方法基于图12所示的字节修改频率规律,即编号差值为8的字节具有相似的修改频率.因此,聚集分片方法将编号差值为8的字节划分至相同数据片,即数据片m(m=0,1,…,7)包含字节8i+m(i=0,1,…,7).通过将相似修改频率的字节聚集在一起,聚集分片方法能够有效降低因部分字节修改而导致重加密整个数据块的概率,从而减少加密数据的写操作带来的位翻转.

Fig. 13 Successive and gathering partition methods of data blocks图13 数据块连续分片方法和聚集分片方法

动态数据分片策略包括2种分片方法.为记录数据块采用何种方法进行分片,COTANA为每个数据块维护1 b类型标记.当执行读操作时,先根据类型标记对数据块进行分片,再根据加密计数器和选择重加密元数据对数据块解密;当执行写操作时,先并行地采用2种分片方法划分数据块并执行重加密,再计算采用不同方法的加密数据造成的位翻转数量.为计算位翻转数量,需要将内存中数据读取至内存控制器中与加密数据进行对比.因此,动态数据分片策略在执行每个写操作时会引入1次额外读操作.由于NVM的读延迟通常低于写延迟,写耐久性差于DRAM,同时动态数据分片策略可以有效地降低加密带来的写性能和耐久性影响,故该策略的额外读操作带来的开销是可接受的.最后,动态数据分片策略动态地选择造成位翻转最少的加密数据写回内存并根据选取的分片方法设置类型标记.为降低维护类型标记的开销,将类型标记也放置在完整性检测树的叶子结点中.例如,每个叶子结点包括1个32 b主计数器、16个5 b从计数器、16个1 b类型标记、64个2 b局部计数器、128个2 b计数器指示器.

2.4 开销分析

COTANA通过对多种元数据协同管理,降低元数据访问开销.但是,由于完整性检测树的每个叶子结点中仅能存放16个从计数器,故有可能增大元数据存储开销.表2所示为COTANA和MC-Nacre[7-8]的存储开销对比.因为COTANA和MC-Nacre均将数据块的MAC放置于ECC芯片,同时将加密计数器放置在叶子结点中,所以表2中只考虑完整性检测树和选择重加密元数据的开销.假设内存大小为4 GB,数据块大小为64 B,则内存中总共有226个数据块.MC-Nacre允许每个完整性检测树结点中至多存放128个从计数器.因此,结点的总数约为219个,总大小约为32 MB.此外,MC-Nacre(8,4),MC-Nacre(4,4),MC-Nacre(2,4)分别为每个数据块维护24 b,40 b,72 b选择重加密元数据,即存储开销分别为192 MB,320 MB,576 MB.此外,MC-Nacre需要在选择重加密元数据上建立额外的完整性检测树,以保障元数据的完整性.相比于MC-Nacre,COTANA虽然在每个叶子结点中仅存放16个从计数器,即完整性检测树总大小约为256 MB,但是无需单独维护重加密元数据及额外的完整性检测树,从而降低元数据开销.

Table 2 Percentage of Memory Size Occupied by Metadata表2 元数据占内存容量的百分比 %

现有的安全PM系统[7,16-17]在ECC内存的内存控制器中集成了加密、完整性检测、选择重加密所需的硬件,包括元数据缓存及计算组件.在现有系统的基础上,COTANA仅需对内存控制器进行小幅修改并添加选择重加密的计算组件,以实现对安全元数据的重新组织,以及并行地采用不同分片方法进行选择重加密并动态选择造成位翻转最少的分片方法.

3 实验评估

3.1 实验配置

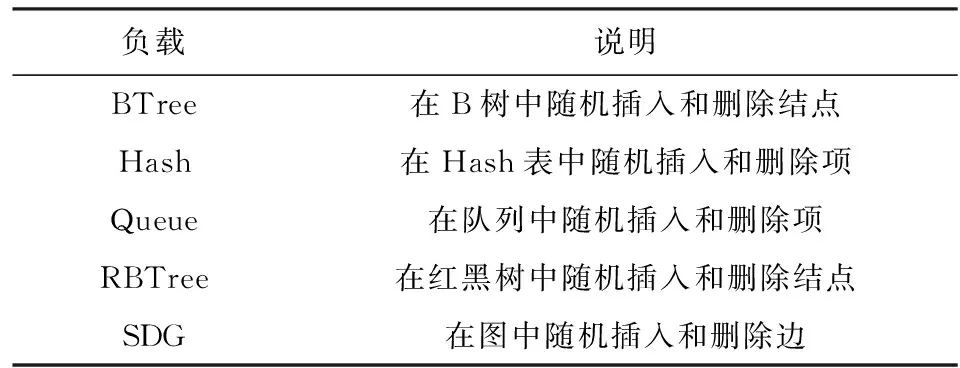

本文将NVM模拟器NVMain[31]与全系统仿真器Gem5[18]进行整合,通过NVMain为Gem5提供高精度PM系统仿真支持,并在此基础上实现COTANA.表3所示为仿真器的参数配置.元数据缓存的默认大小为128 KB.COTANA采用MorphCtr[7]策略管理完整性检测树的内部结点,同时基于Nacre[8]策略实现叶子结点的管理和选择重加密.实验中,COTANA的对照系统包括仅采用MorphCtr的系统MC-Only,以及采用MorphCtr和Nacre但具有不同参数的系统MC-Nacre(8,4),MC-Nacre(4,4),MC-Nacre(2,4).为评估上述系统,我们从标准负载集SPEC CPU2006[29]中选取10个内存密集型负载.在运行每个负载时,先执行5亿条指令对缓存进行预热,再执行20亿条指令以统计实验结果.此外,我们还使用表4所示的持久性数据结构负载[30]对上述系统进行评估.每个负载针对相应的数据结构执行10万个事务操作,每个事务中执行随机查找操作,若未找到数据则插入数据,否则删除已有数据.

Table 3 Simulator Configuration of Parameters表3 仿真器参数配置

Table 4 Persistent Data Structure Workloads表4 持久性数据结构负载

3.2 SPEC CPU2006负载下的实验结果

图14所示为各系统的IPC,实验结果基于MC-Only进行了归一化处理.与MC-Only相比,MC-Nacre(8,4)存在平均10.4%的IPC下降.这是因为在数据加解密的关键路径上可能需要等待从内存中分别读取加密计数器和选择重加密元数据块.由于选择重加密元数据开销随着分片粒度的减小而增加,故采用更细粒度分片的MC-Nacre(4,4)和MC-Nacre(2,4)分别存在12.4%和17.3%的IPC下降,而COTANA仅造成4.6%的IPC下降.相比MC-Nacre(8,4),IPC最高提升了13.7%.这是因为COTANA通过元数据协同管理将数据加解密所需元数据整合在相同数据块中,从而减少关键路径上元数据块的访问.

Fig. 14 Normalized IPC based on MC-Only图14 基于MC-Only归一化的IPC

Fig. 15 Breakdown of number of memory accesses图15 内存访问次数分解

为进一步验证COTANA是否能够有效减少元数据导致的内存访问,我们对各系统在负载运行过程中的所有内存访问进行统计.图15所示为基于应用数据访问次数归一化后的实验结果.在所有元数据导致的内存访问中,选择重加密元数据访问占据较大比例.因为选择重加密元数据总大小随着数据分片粒度减小而增大,所以MC-Nacre(8,4),MC-Nacre(4,4),MC-Nacre(2,4)的内存访问次数依次增加.相比MC-Nacre(8,4),COTANA通过元数据协同管理最多减少了22.9%的内存访问次数.对于部分负载(例如zeusmp),COTANA减少的内存访问相对有限.这是因为这些负载对于内存的访问具有良好的局部性,使得元数据缓存有较高的命中率.对于部分负载(例如astar),COTANA相比于其他系统有更少的计数器溢出造成的内存访问.这是因为虽然COTANA将选择重加密元数据与加密计数器放置在相同元数据块中会提升计数器溢出频率,但是当计数器溢出发生后,在对内存中数据重新加密的过程中,COTANA仅需1次内存访问即可获取重新加密1个数据块所需的加密计数器和选择重加密元数据,而其他系统则需要2次内存访问才能获取相关元数据.

图16所示为加密数据块写入内存时平均每个数据块中存在的位翻转的比例.随着数据分片粒度减小,可以减少因部分字节修改导致整个分片重加密的情况.因此,MC-Nacre(8,4),MC-Nacre(4,4),MC-Nacre(2,4)的位翻转比例依次降低,全部负载的平均值分别为33.2%,26.2%,23.1%.而COTANA的位翻转比例的平均值为27.5%.这是因为动态数据分片策略可以有效减少因部分字节修改导致整个分片重加密的情况.COTANA可以通过与MC-Nacre(8,4)相同的分片粒度同时取得更高的性能和更少的位翻转.而相比MC-Nacre(4,4)和MC-Nacre(2,4),COTANA虽然具有更高的位翻转,但可以避免细粒度分片带来的选择重加密元数据开销和性能下降.

Fig. 16 Averaged percent of bit flips per NVM write图16 NVM写操作平均位翻转比例

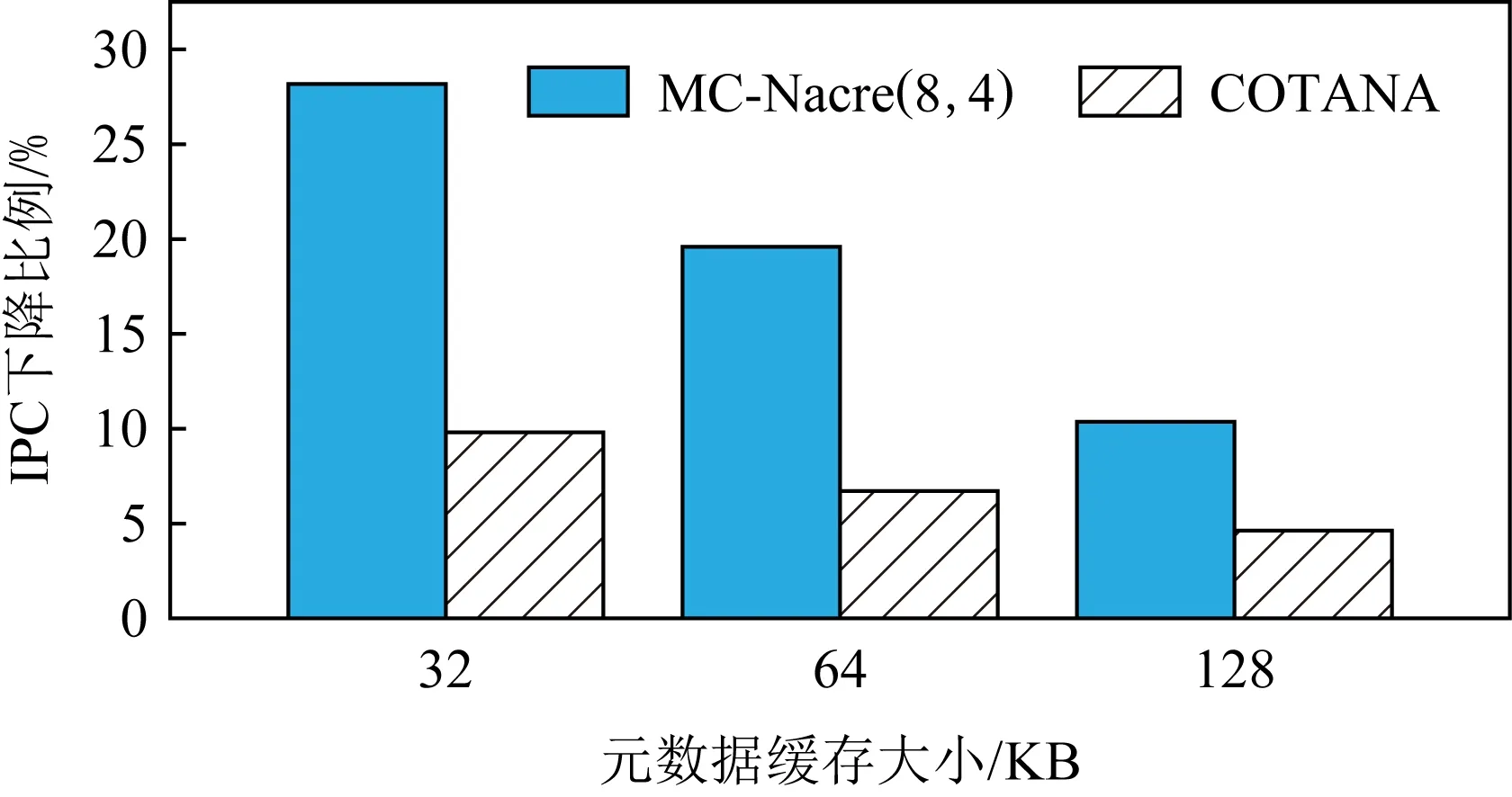

图17所示为不同元数据缓存大小下各系统相对于MC-Only的IPC下降比例.相比MC-Nacre(8,4),COTANA在元数据缓存大小为128 KB,64 KB,32 KB时分别可减少5.8%,12.9%,18.4%的IPC下降比例.这是因为元数据缓存的命中率随着元数据缓存大小减小而降低.而COTANA通过元数据协同管理能够有效降低元数据缓存未命中时访问元数据的开销.

Fig. 17 Percentages of IPC degradation on different metadata cache sizes图17 不同元数据缓存大小下的IPC下降比例

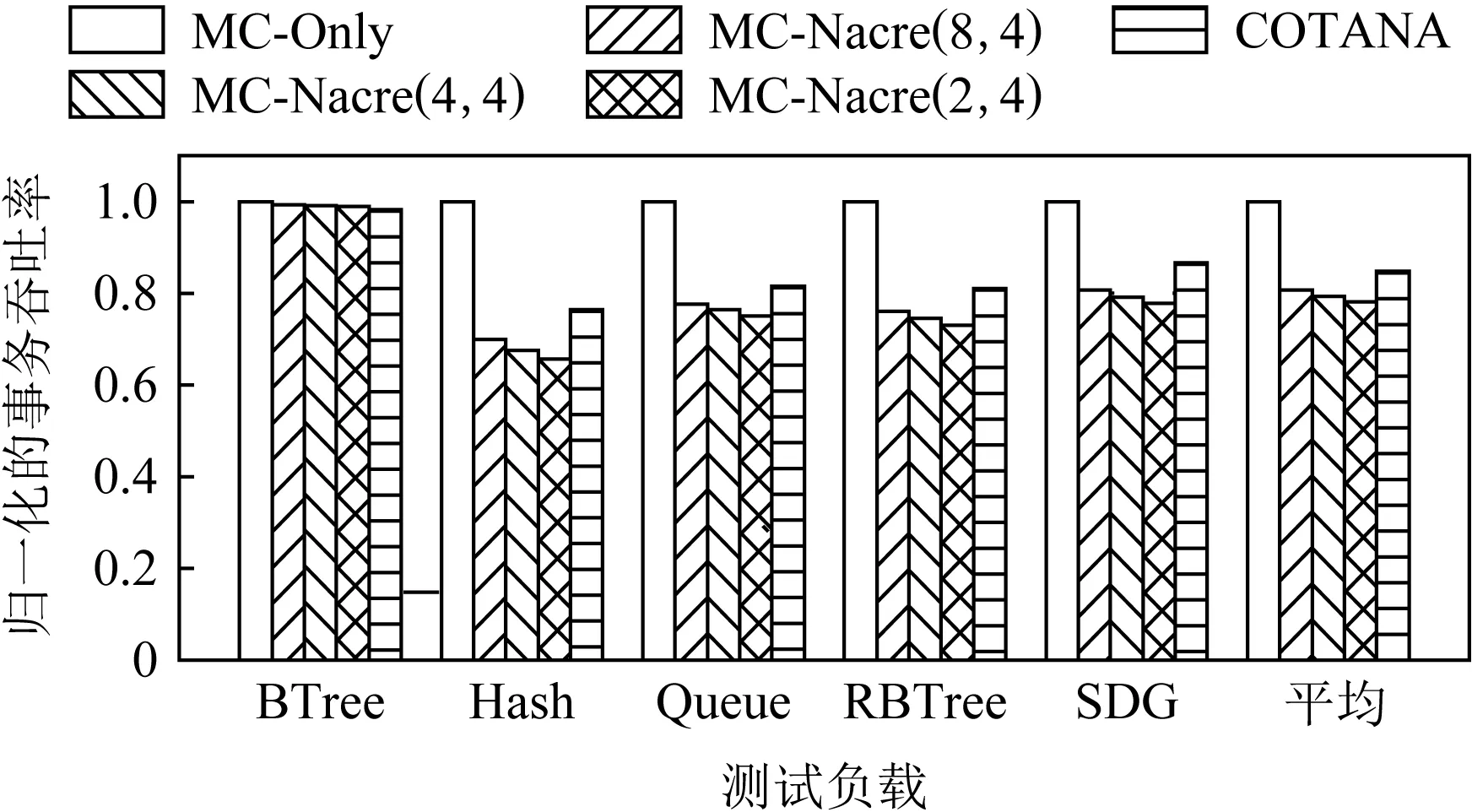

Fig. 18 Transaction throughput normalized to MC-Only图18 基于MC-Only归一化的事务吞吐率

3.3 持久性数据结构负载下的实验结果

图18所示为各系统的事务吞吐率.实验结果基于MC-Only进行了归一化处理.与MC-Only相比,MC-Nacre(8,4),MC-Nacre(4,4),MC-Nacre(2,4)分别存在平均19.3%,20.7%,21.9%的性能下降.而COTANA相比MC-Only仅平均造成15.2%的性能下降,COTANA相比MC-Nacre(8,4)最多提升9.3%的性能.因此,COTANA不仅适用于计算密集型的应用场景,也适用于存储密集型的应用场景.

4 相关研究工作

目前一些研究工作关注于如何高效管理安全元数据.IVEC[21]提出将完整性检测与数据纠错结合,利用MAC检测数据是否存在错误,并通过检查可能出错的位置或校验信息辅助的方式修复数据.在此基础上,SYNERGY[16]进一步提出了数据、MAC、校验信息在内存中的布局方法,将MAC放置在ECC芯片中,而将校验信息放置在内存中其他区域,从而允许数据和MAC并行访问.VAULT[10]根据完整性检测树中层次越高的结点中的计数器增长越快的特性,为高层次结点分配更大的计数器,从而避免频繁的计数器溢出.此外,通过压缩数据块将MAC放置在压缩节省的空间中,使得无需依赖ECC芯片即可同时访问数据和MAC.为减少完整性检测树开销并减少计数器溢出,MorphCtr[7]提出一种可变的完整性检测树结点组织方式,允许完整性检测树根据应用访问特征动态改变每个结点中从计数器大小,使得每个结点最多可存放128个从计数器.现有的安全元数据管理相关的研究工作主要关注于加密、完整性检测引入的元数据,而没有考虑因写优化需求而引入的选择重加密元数据.COTANA则是综合考虑加密、完整性检测、选择重加密元数据的特性,实现各类元数据的协同管理,以降低元数据访问开销.

由于加密算法存在雪崩效应,现有一些研究工作关注于如何降低安全NVM中写操作开销.DEUCE[6]为每个数据块维护领头计数器和跟随计数器.跟随计数器由领头计数器屏蔽低位后计算得到.在数据写入内存时,将数据划分为16b大小的数据片,使用跟随计数器加密未修改数据片,使用领头计数器加密被修改的数据片.Nacre[8]和SECRET[28]为每个数据片维护1个局部计数器,仅当数据片被修改时才更新局部计数器,并对数据片进行重新加密.DeWrite[11]将加密与数据去重结合,以减少写入内存的重复数据.ASSURE[32]将MAC值进行细粒度划分,以避免为未修改的数据片重新计算MAC.现有安全NVM写操作优化相关的工作可以直接与COTANA协同工作,通过元数据协同管理策略降低元数据访问开销,同时通过动态数据分片策略减少位翻转.

系统发生意外崩溃后,仅当安全元数据与NVM中的数据匹配时,才能正确地解密数据并进行完整性检测.因此,部分研究工作[17,22,27,33-36]关注于如何正确并高效地持久化安全元数据.例如,cc-NVM[35]通过基于时段的安全元数据更新方法,在保证安全元数据一致性的同时充分利用元数据缓存,从而显著提升系统性能并减少内存写操作数量.STAR[36]在SGX树中采用54 b的MAC,并将每个结点中节省的10 b空间用于存放父结点中对应计数器的低位,避免在更新SGX树时递归更新至根结点并写回所有更新的结点,从而大幅减少为保证SGX树的崩溃一致性而引入的写操作.与上述这些研究工作相比,COTANA主要关注如何高效组织各类元数据,可以直接使用现有方法实现元数据正确持久化.例如,将COTANA集成至STAR时,仅需修改SGX树叶子结点计数器的组织方式,并在选择重加密时采用动态数据分片策略.此外,COTANA将选择重加密元数据与加密计数器放置在相同数据块中,能够避免单独持久化这2种元数据,从而降低安全元数据一致性保障的开销.

5 总 结

为构建高效安全的PM系统,通常使用加密和完整性检测技术保证数据安全性,以及选择重加密策略降低写操作开销.这些技术引入各类元数据,但目前尚无综合考虑全部元数据特性的元数据管理方法,从而存在较高的元数据开销.此外,我们发现数据块中不同字节存在不同的修改频率,而现有选择重加密策略无法充分利用修改频率特性,从而导致额外的位翻转.为解决上述问题,本文提出一种面向安全PM的元数据协同管理方法COTANA.为减少元数据开销,COTANA将选择重加密元数据与加密元数据放置在相同块中,以减少元数据缓存未命中时所造成的额外内存访问.此外,COTANA利用ECC芯片放置数据块和完整性检测树叶子结点的MAC,以避免MAC访问造成的延迟.为减少位翻转,COTANA采用动态数据分片策略,从现有的连续分片方法和基于修改频率特性设计的聚集分片方法中动态选择造成位翻转最少的方法.实验结果显示,与采用最新的安全元数据管理方法和选择重加密策略的系统相比,COTANA最多能提升13.7%的性能,并减少21.3%的位翻转.

作者贡献声明:魏学亮负责完善本文工作思路,完成部分相关实验,并撰写论文;杨明顺提出本文主要工作思路,并完成其余部分实验;冯丹、刘景宁、童薇对整个工作提出指导意见并修改论文;吴兵和肖仁智对方案设计及论文给出修改意见.