基于MPSoC的Sub-6 GHz频段SDR测试系统设计与实现

黄继业, 谢 辉, 董哲康

(杭州电子科技大学电子信息学院,杭州 310018)

0 引 言

第五代移动通信技术(5G)的加速部署,以及数据吞吐速率、信号带宽的不断提高,对传统射频收发链路的性能提出了更高的要求。此外,由于5G采用更复杂的调制方式、更高的调制阶数、更多的载波聚合以及更高的频段和带宽[1],使得相关通信算法的测试和验证周期变得漫长。软件无线电(Software-Defined Radio,SDR)平台[2]因高度可重构性、较强灵活性、模块化结构以及开放性等众多优势[3],广泛用于无线通信网络框架和算法原型验证平台的搭建。

目前常用的测试验证环境主要包括基于矢量信号发生器(Vector Signal Generator,VSG)和矢量信号分析仪(Vector Signal Analyzer,VSA)的解决方案,以及SDR测试平台两大类。其中,是德科技(Keysight Technologies)基于M8190A超宽带任意波形发生器和N9040B UXA超宽带信号分析仪所构成的解决方案,可进行系统级和软硬件模块的测试和验证,但其存在成本高、工程扩展性欠佳等问题;另一方面,传统SDR平台[4-6]受限于传输带宽或接口速率,大部分均无法达到5G应用场景下的射频链路要求。

本文提出的SDR测试系统以Xilinx MPSoC作为主控芯片,配合宽带收发器,可进行满足4G/5G传输链路要求的高带宽信号收发与测试实验。同时,该系统具备高可重构性,通过预留的软件接口即可进行系统全局控制。

1 SDR测试系统软硬件框架构建

1.1 SDR测试系统整体架构设计

基于对系统应用场景、性能需求、硬件资源和成本的整体考虑,采用Xilinx ZYNQ UltraScale+MPSoC和ADRV9009集成射频收发器进行系统架构搭建[7],如图1所示。

本测试系统(实验平台)主要由基于MPSoC的数字端和基于ADRV9009的射频前端两大部分构成,两者通过JESD204B接口[8-10]进行高速数据传输,PL(Programmable Logic)侧逻辑进行信号处理和数据搬运。MPSoC-PS(Processing System)端运行预编译的、基于Petalinux构建的定制Linux系统[11],允许用户根据自身项目需求,配置相关驱动或加入自定义驱动。

1.2 SDR测试系统PL逻辑设计

系统的PL侧逻辑负责数字基带信号处理和数据流通路的实现,如图2所示。

ZYNQ UltraScale+MPSoC PS部分以IP核的形式出现在PL逻辑设计Block Design中,通过此IP能够较为轻易地控制PS侧外设资源,包括用于数据缓冲的PS侧DDR4、用于控制ADRV9009初始化及配置过程的SPI控制器、用于ARM Linux启动信息和DEBUG信息打印的UART接口等。整个PL侧逻辑大致可分为两大部分——发射通路和接收通路,针对发射通路,数据流起点为DMA(Direct Memory Access)模块,该模块的主要功能是将DDR4中的IQ数据以高速率搬运至TXFIFO(First Input First Output)模块中,进行跨时钟域处理,此外,该DMA模块被挂载在AXI总线上,并配置有Cyclic模式选项,在此模式下,DMA源端数据可由ARM Linux提供,并以循环播放的方式向目的端发送。TXFIFO模块将来自DMA的IQ数据同步至后续逻辑能够处理的较低时钟域,并作为用户定义通信算法IP的输入数据,其输出数据经通道分离、FIR数字滤波操作后,被送入JESD204B Core的4条Lane。同理,对于接收通路,IQ数据经JESD204B链路后,经FIR数字滤波、通道合并后,被RXDMA模块搬运至DDR4中以进行数据缓冲。针对JESD204B链路逻辑,其接收来自ADRV9009板载AD9528时钟管理芯片的两个信号——ref_clk和sysref,用于射频子板与FPGA之间高速串行数据链路的同步,以保证高速率传输下数据的有效性,如图1所示。

1.3 SDR测试系统PS软件设计

系统PS部分的设计整体采用对称多处理器架构。此外,为降低对射频子板上模拟芯片的控制复杂度,使用Linux IIO(Industrial I/O)对上述设备进行读写控制,控制子系统如图3所示。

本系统所使用的libiio一个用于访问IIO设备的开源库,基于该开源库,可轻易通过标准Linux设备访问接口,如sysfs、debugfs、configfs等,对IIO设备进行配置和读写访问,本工程选用sysfs作为用户空间与IIO设备的交互接口。开源libiio库除了具备基本的对/sys/bus/iio/devices/路径下所有IIO设备的IO配置功能和对/dev/iio/iio:deviceX的读写访问功能之外,还提供了便于测试的iio命令行工具,如iio_info、iio_readdev等,允许用户根据自身需求,有选择地编译出相应可执行文件,以获取相应Debug功能。本设计编译了iio_info、iio_attr、iio_reg、iio_readdev、iio_writedev,因而具备对iio设备的信息枚举、寄存器级读写访问等常用功能。

基于libiio开源库定制的High-Level API(Application Programming Interface),被用于用户空间应用层程序的开发,该应用程序代码一般包含两部分,一部分是用于配置板卡参数的代码,如图4所示;另一部分是对数据流控制的代码。其中,stream_cfg类型的结构体,用于存储配置参数,如本振频率lo_hz、通道配置带宽bw_hz和ADDA采样率fs_hz等,cfg_ADRV9009_streaming_ch()函数配合stream_cfg,对IIO设备进行参数加载。

硬件参数配置成功后则进入数据流控制阶段,当DMA模块工作在Cyclic模式时,Linux预存的IQ数据首先被读入用户空间的iio_buffer,然后经内核空间buffer传递给PL逻辑并存储,PL逻辑以特定速率循环播放该段信号,数据流传递示意图如图5所示,通过该方法,可对SDR测试系统的信道可靠性进行验证。

1.4 SDR测试系统基本功能

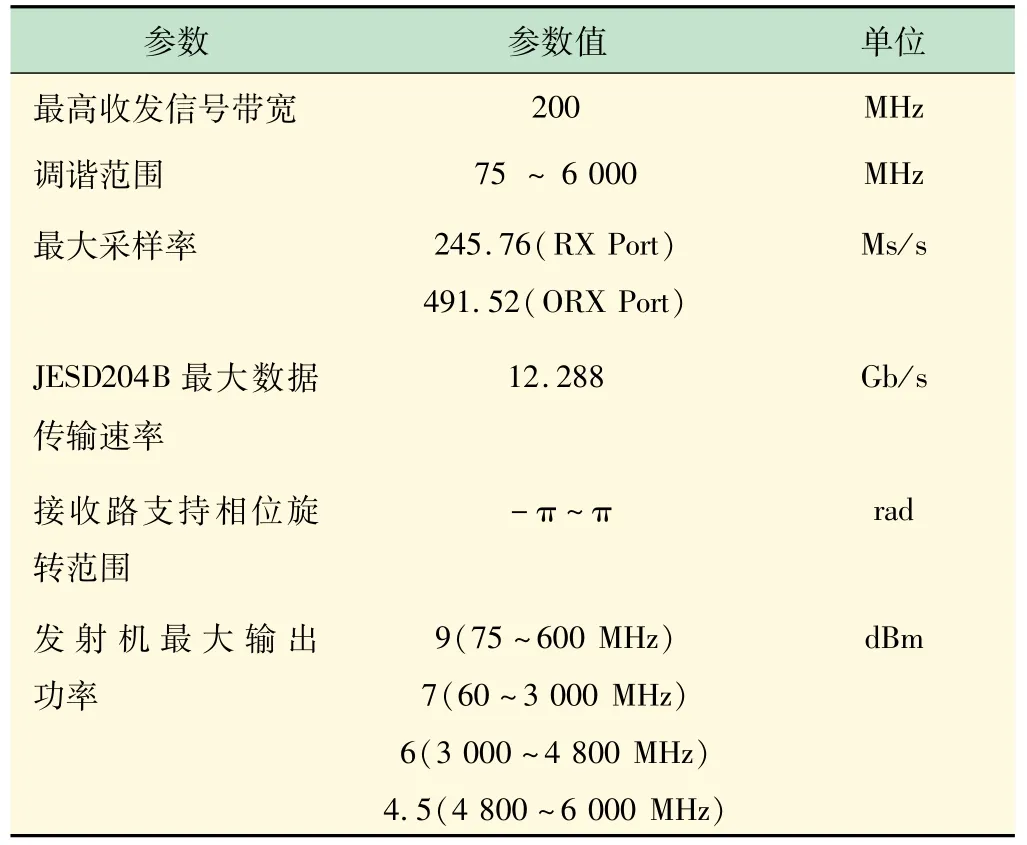

本SDR测试系统的硬件包含MPSoC PL端逻辑硬件和其他板载硬件,可支持单通道最高200 MHz信号的收发,并且,允许用户通过软件配置以达到最高2发2收的MIMO结构,表1为SDR测试系统基本功能参数。

表1 SDR测试系统功能参数

信号接收方面,射频前端拥有两通道接收端口和两通道观察端口,两者复用4个ADC,以两通道接收路为例,首先由ADC对灌入信号进行高速采样,采样获得的数字信号经过数字滤波、信号放大、混频等处理后,以16 bit的IQ信号形式进入射频子板的JESD204B模块,并以最高245.76 MHz的IQ速率经FMC(FPGA Mezzanine Card)接口发送至MPSoC-PL侧JESD204B逻辑模块,后续FPGA逻辑进行相应信号处理与数据存储。

信号发射方面,TXDMA模块作为发射路起点,其源数据既可来自PS侧DDR4中存储的IQ信号数据,也可来自Linux用户空间经sysfs文件接口导入IIO设备的IQ数据,TXDMA模块将信号数据搬运至发射通路,经JESD204B逻辑模块发送至ADRV9009射频子板,并且经过数字滤波、DA转换、模拟滤波、混频、放大等处理后,以射频信号形式发射。

在MPSoC-PL侧发射通路的逻辑设计中,在TXFIFO模块后预留了用户定义IP的嵌入位置,如图2 PL侧逻辑框图所示,预设的数据传输机制为简单的Ready-Valid握手机制,用于与用户定义IP之间数据的有效传输,当然,该握手机制可被轻易转化为符合AXI4-Stream协议规范的信号传输机制,以适应特定场景下高速率数据流的有效传输。

此外,本SDR测试系统允许测试人员通过PC远程登录ARM Linux系统,进行系统全局控制,并且PC与板卡通过以太网相连,测试人员可通过FTP(File Transfer Protocol)进行PC与开发板之间的文件交互,如波形数据文件的传输等。

2 SDR测试系统实验验证

2.1 数据收发实验及其环境搭建

本文将分别使用80 MHz四载波LTE信号和100 MHz 5G NR信号进行数据接收/发送实验,以验证系统的数据收发链路可靠性。通过SMA射频同轴线将ADRV9009收发器上TXPort1与RXPort2相连,并从TX1端口耦合出一路信号接入频谱分析仪,以便观察发射通路一的输出信号频谱。ADRV9009射频收发器与ZCU102开发板通过板载FMC接口进行板级连接,ZCU102与PC之间进行以太网、串口和JTAG连接,以便进行两者之间的文件交互、启动信息打印和命令控制。将开发板拨码开关SW6调节至1110(SD卡启动模式),SD卡中烧录有预编译的LinuxImage、BOOT.BIN和设备树文件。

2.2 数据收发实验结果与数据分析

数据接收方面,使用80 MHz四载波LTE信号验证该SDR测试系统的接收性能。信号源由MATLAB生成,信号采样率为245.76 Ms/s,故在Linux上对ADRV9009的配置代码中,需将stream_cfg结构体中的fs_hz设为245.76,此外,发射带宽bw_hz使用默认的200 MHz即可。数据采样方面,iio_buffer大小设置为65 536,接收机对从RX2端口灌入的信号进行采样并最终以文件形式保存至dataRX.txt文本中。

整个数据接收实验验证流程如下:SDR测试系统上电启动后,JESD204B链路初始化成功,测试人员通过PC登录ARM Linux系统,并且将PC中预先生成的波形数据文件通过FTP发送至ARM Linux,然后编译数据流控制程序源码以生成可执行文件后,运行该可执行文件进行波形数据读取、发送,待信号发送稳定并成功采样保存后,通过FTP将采样数据回传至PC,MATLAB读取采样数据并归一化,再利用Welch法[12-14]画出功率谱,Welch算法部署如下:

假设归一化后数据x(n)为长度N的复数序列,n=0,1,…,N-1,将该序列分为K段,每段包含M个数据,那么第i段数据为

然后将窗函数w()n加到每一个数据段上,并求出每一段的周期图,第i段数据周期图为

式中,U为归一化因子,

将每一段的周期图近似看成互不相关,最后功率谱估计为

图6即为根据零中频接收机的采样数据计算所得功率谱。

数据发送方面,使用5 G NR 100 MHz带宽测试信号进行发射通路可靠性的验证,该5 G信号由MATLAB 5 G Waveform Generator生成[15-16],使用的模型为NR-FR1-TM3.1a,载波空间为满带,调制制式为256QAM(Quadrature Amplitude Modulation),子载波间隙(Sub-CarrierSpacing,SCS)为60 kHz,并进行一定的增益调整。

整个数据发送实验验证流程如下:在上述数据接收实验的基础上,基于本SDR测试系统的高可重构性、高可移植性和模块高复用性优势,可轻易进行数据发送实验。只需从PC通过FTP向ARM Linux重新发送预生成的100 MHz 5 G NR信号数据文件,并在Linux端修改控制程序源码中波形文件名即可,若有需要可通过修改相关结构体变量以修改对射频子板的参数配置,并使用Makefile脚本重新编译可执行文件并运行即可,底层关于JESD204B链路驱动、AD9528时钟芯片驱动等均无需更改。在此次实验中,中心频率lo_hz被设置为1.5 GHz,图7为该信号频谱图。

3 结 语

本文使用Xilinx XCZU9EG MPSoC和ADRV9009射频收发器搭建了一套可用于5 G Sub-6 GHz频段高带宽信号测试的SDR系统,通过Petalinux和libiio开源库的加持,使得测试人员可通过定制的Linux系统对测试系统进行全局控制,具有高可重构性(包括可配置MIMO)、75 MHz~6 GHz超宽调谐范围等技术优势,以及支持最高200 MHz收发信号带宽、可移植性强、成本低、通用性强等平台优势。此外,采用软硬件分离式设计思想,使得系统模块架构清晰。经多载波聚合的80 MHzLTE信号和100 MHz 5 G NR信号的数据收发实验验证,本SDR测试系统可满足4 G/5 G应用场景下的信号收发链路性能要求,信道可靠性较高,可作为5 G SDR实验平台使用,此外,在5 G信号测试和通信算法原型验证方面,也具有一定的应用价值。