星载天海中继通信载荷信号处理单元实现

刘 冕,胡一皓,王晋阳,刘才瑞,梁显锋

(1.中国科学院国家空间科学中心,北京 100190;2.中国科学院大学 电子电气与通信工程学院,北京 100190)

0 引言

低轨互联网卫星网络能够实现广域无缝覆盖,是未来海陆空一体化网络的重要组成部分[1]。目前在海洋研究领域,通信卫星网络能为深远海的海洋观测浮标与岸基站/船基站之间提供实时数据通信。美国铱星系统(Iridium Satellite)、法国Argos系统等低轨通信卫星网络最大能实现128 kb/s的双向数据传输[2];我国天通一号通信卫星网络能够实现384 kb/s速率的数据通信[3],但是数据速率均未超过1 Mb/s[4]。随着海洋水下载荷获取数据量的不断增加,水面通信浮标到船基或岸基数据中心间需要实现高数据传输速率链路。

最近,某单位研制了一台天海中继通信载荷,搭载在低轨卫星上,用于验证海面到船端间高速率中继通信链路试验,实现水面到数据中心间8 Mb/s速率的数据通信链路。天海中继通信载荷主要包括射频单元和数字基带单元。本文完成了天海中继通信载荷中L波段数字基带单元的设计和功能实现。基带单元主要实现通信链路编码调制一体化的技术方案。在FPGA为主的平台上不仅实现里德所罗门卷积级联(Reed-Solomon Convolution Concatenated,RS-CC)编码以及低密度奇偶校验码(Low Density Parity Check Code,LDPC)编码功能,且可自动切换前向链路的2种编码调制方式;反向链路接收方案采用零中频解调将来自水面浮标端的载荷数据进行解调并使用反馈环路校正了链路多普勒频移的影响。文中也叙述了载荷的调试和测试工作。

1 技术分析

1.1 特性分析

天海中继通信载荷主要功能是实现海面浮标经低轨卫星中继,与跨距500 n mile外的船端或陆地数据中心之间的高速率数据通信试验。载荷通信频段为低轨互联网段的L波段,通信链路如图1所示。

图1 通信链路示意Fig.1 Diagram of the communication link

卫星到海面浮标端的通信链路定义为前向链路,初始低码率模式下传星历数据,用于浮标端天线快速跟踪卫星;高码率模式为卫星天海中继通信载荷收到海上浮标端发送的8 Mb/s数据,直接转发下行到跨距500 n mile的船端或岸基端。海面浮标到卫星的固定8 Mb/s高码率通信链路定义为反向链路。

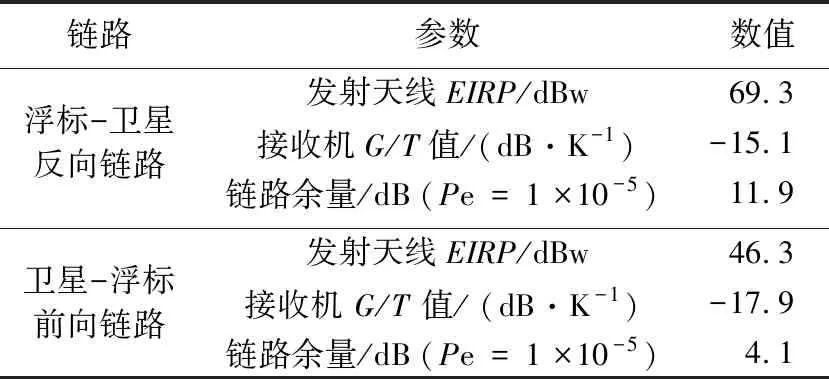

卫星轨道高度500 km,根据链路计算式(1)分别完成了反向链路和前向链路特性计算,结果如表1所示。

表1 海面到卫星链路预算结果Tab.1 Results of sea level to satellite link budget

(1)

式中,C/N0为接收端的载噪比;EIRP为卫星等效全向辐射功率;G/T为接收品质因数;L为链路损耗;k为波尔兹曼常量,k= 228.6 BJ/K。

如前所述,前向链路初始速率为512 kb/s,依据CCSDS132.0-B-2蓝皮书[5]的建议和要求,采用(255,233)RS-CC编码、差分正交相移键控(Differential Quadrature Reference Phase Shift Keying,DQPSK)调制体制。高码率前向链路和反向链路速率为8 Mb/s时,依据CCSDS 732.0-B-2[6]的建议和要求,数据采用 (8 160,7 136)LDPC编码、DQPSK调制体制。由表1所示的链路预算结果可知,链路余量满足通信链路大于最低3 dB的要求[7],且反向链路余量较大,能够确保通信链路的可靠建立。

1.2 技术方案

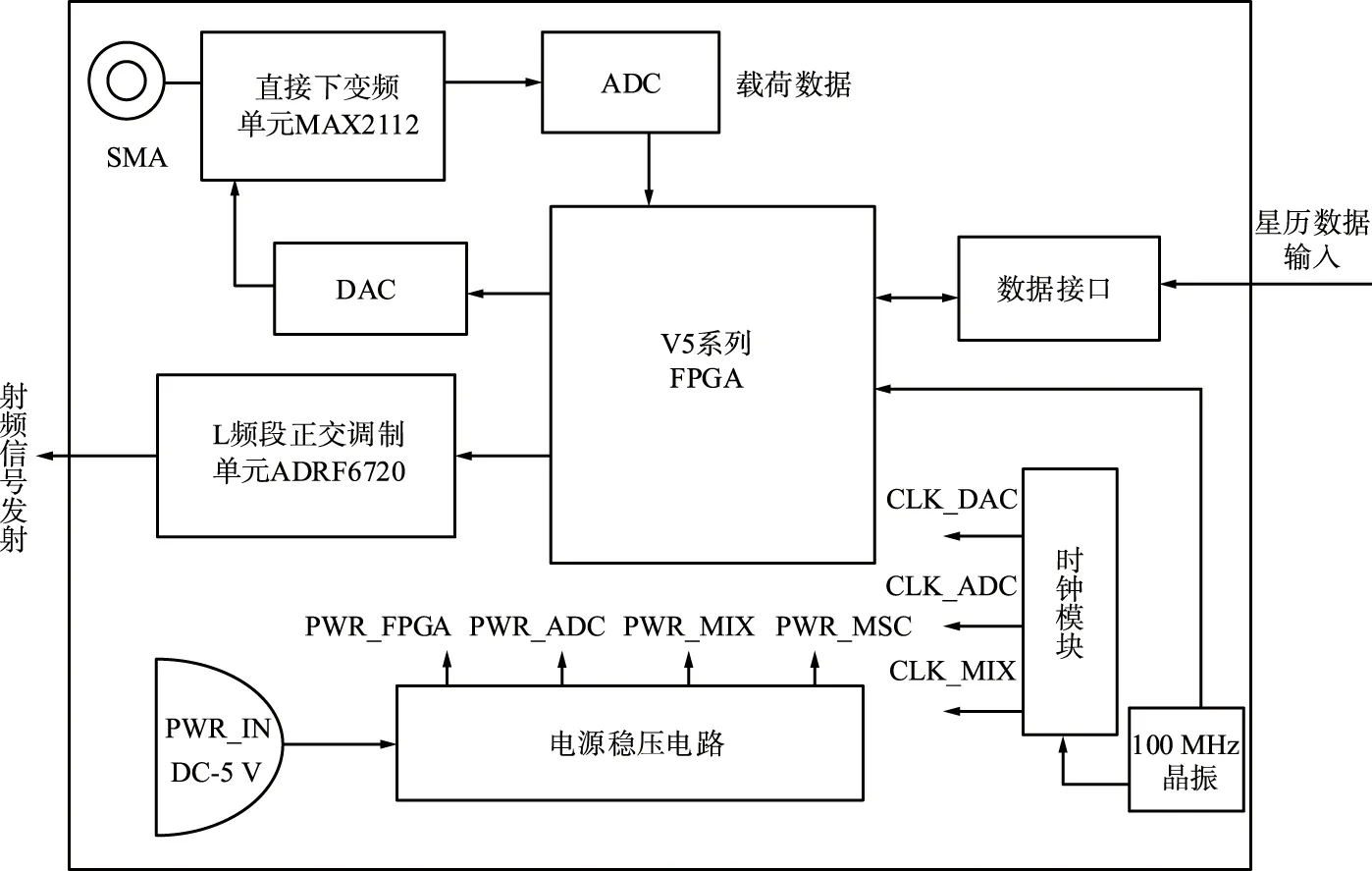

L频段天海通信载荷数字基带电路模块由V5系列FPGA芯片和相关的外围电路组成,系统框图如图2所示。电路包括时钟管理模块、正交调制模块、电源模块、数据接口以及直接下变频等模块。在FPGA内部实现与外部数据的交换、RS编码、LDPC编码、加扰、组帧、调制解调和模式切换等功能。基带板集成了射频正交调制发射模块,基带信号在FPGA内进行差分编码后在调制模块实现L波段QPSK直接调制,即完成数据的DQPSK调制输出到功率放大器。解调模块使用具备直接变频功能的MAX2112芯片[8]实现将射频信号直接变频到基带信号的零中频方案。相比于超外差结构,零中频结构的接收前端没有中频电路,可以减小接收端电路的体积和电路复杂度。零中频输出信号经模数转换芯片AD9284[9]采样后输出到FPGA,该芯片双通道差分输入口可以实现对I,Q两路同时采样。为了实现零中频接收端一定动态范围,利用数模转换芯片AD9744与MAX2112形成回路,用于实现自动电平增益控制(Automatic Gain Control,AGC)。

图2 系统实现框图Fig.2 Block diagram of system implementation

2 关键技术实现

2.1 工作模式切换

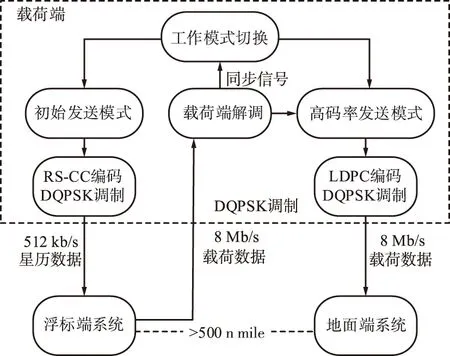

天海中继通信载荷前向链路有2种工作模式:初始模式是对海面发送512 kb/s的星历数据;高码率模式发送8 Mb/s的数据,该数据来自载荷接收的浮标端发送的信息。载荷工作模式的切换示意如图3所示。

图3 工作模式切换示意Fig.3 Diagram of working mode switching

解调模块是否检测到帧同步信号作为载荷模式切换的依据。载荷开机后没有收到来自海面浮标端数据,即反向链路没有建立,初始模式对卫星波束覆盖海面发送512 kb/s星历数据。如果载荷收到浮标端的载荷数据信号,解调模块检测到帧同步信号,FPGA内部将切换到高码率模式,将收到的载荷数据进行LDPC编码调制下发至地面端系统。帧同步信号失锁后切换回低码率初始模式。工业级正交调制芯片ADRF6720[10]可实现将I,Q基带数据直接调制到所需的载波频率。因此,FPGA内实现数据切换只需要将完成编码调制处理后输出的I,Q两路基带信号进行切换,即可实现发射的工作模式切换。具体的切换流程如图4所示。

图4 工作模式切换流程Fig.4 Flowchart of working mode switching

为了确定载荷数据是否发完,在FPGA内使用计数器进行判断。帧同步信号为单脉冲信号,检测到帧头时输出一个脉冲信号。以32 kHz的时钟作为计数器的驱动时钟,在检测到每个帧同步脉冲时将计数器复位,同时将指示信号拉高,工作模式切换为高码率模式;若接收不到帧同步信号时则在时钟的驱动下开始计数,计数器若计到设定的值时仍未检测到帧同步信号则认为已失去同步,此时将指示信号拉低,工作模式切换成初始发送模式。本设计中计数器值设定为96 000,即在3 s内未检测到帧同步信号时切换工作模式。

2.2 低码率数据编码

初始模式发送星历数据时使用级联的RS(223,255)外码、速率适配的(2,1,7)卷积内码实现交织编码。由于星历数据量较小,采用这种实现简单且延时较小的编码技术,能够在满足编码增益需求和带宽限制的同时节省星上资源[11]。

系统时钟为100 MHz外部晶振输入,在FPGA内使用DCM ip核完成分倍频后产生系统功能模块所需要的工作时钟。星历数据编码调制后速率为512 kb/s,FPGA内部所需时钟分别为32,256,512 kHz;同时,时钟产生功能模块输出8 MHz和1 MHz时钟,作为LDPC编码以及后续调制模块的参考时钟。

星务计算机通过异步串口RS422以1 Hz的频率,115 200波特率将83 byte长度的一帧星历数据发送给载荷的数字处理单元,载荷将接收到的数据送入编码调制模块。由于数据接收时钟和后一级RS编码模块的时钟频率不同,使用异步FIFO对数据进行缓存,以解决跨时钟域可能产生的亚稳态问题。输入数据长度和编码所需的255 byte长度不一致,故使用状态机控制FIFO的读写状态,确保在一帧星历数据写入FIFO后再进入读数据状态。星历数据具体编码流程如图5所示。

图5 星历数据编码流程Fig.5 Ephemeris data encoding process

编码后完整的数据帧包含4 byte帧头,共259 byte,以8 bit并行传送,同时输出帧头指示信号。加扰模块根据帧头指示信号选择性加扰,对除同步帧头以外的传输帧数据加扰。卷积编码模块对加扰后的信号进行卷积操作,将其码率倍增到512 kb/s。

2.3 高码率数据编码

卫星星上资源有限,星上载荷在尺寸、质量和功耗等方面均有限制[12],设备发射功率不可能无限制提升,因此选择优异的信道编码方案来获得可观的信道增益,有效降低信号解调门限[13]。

前向链路高码率模式时,受限于卫星端搭载天线的发射功率和带宽等因素,高码速率模式的反向链路和前向链路中选取高编码增益、低误码及译码性能逼近香农限的LDPC编码[14]。

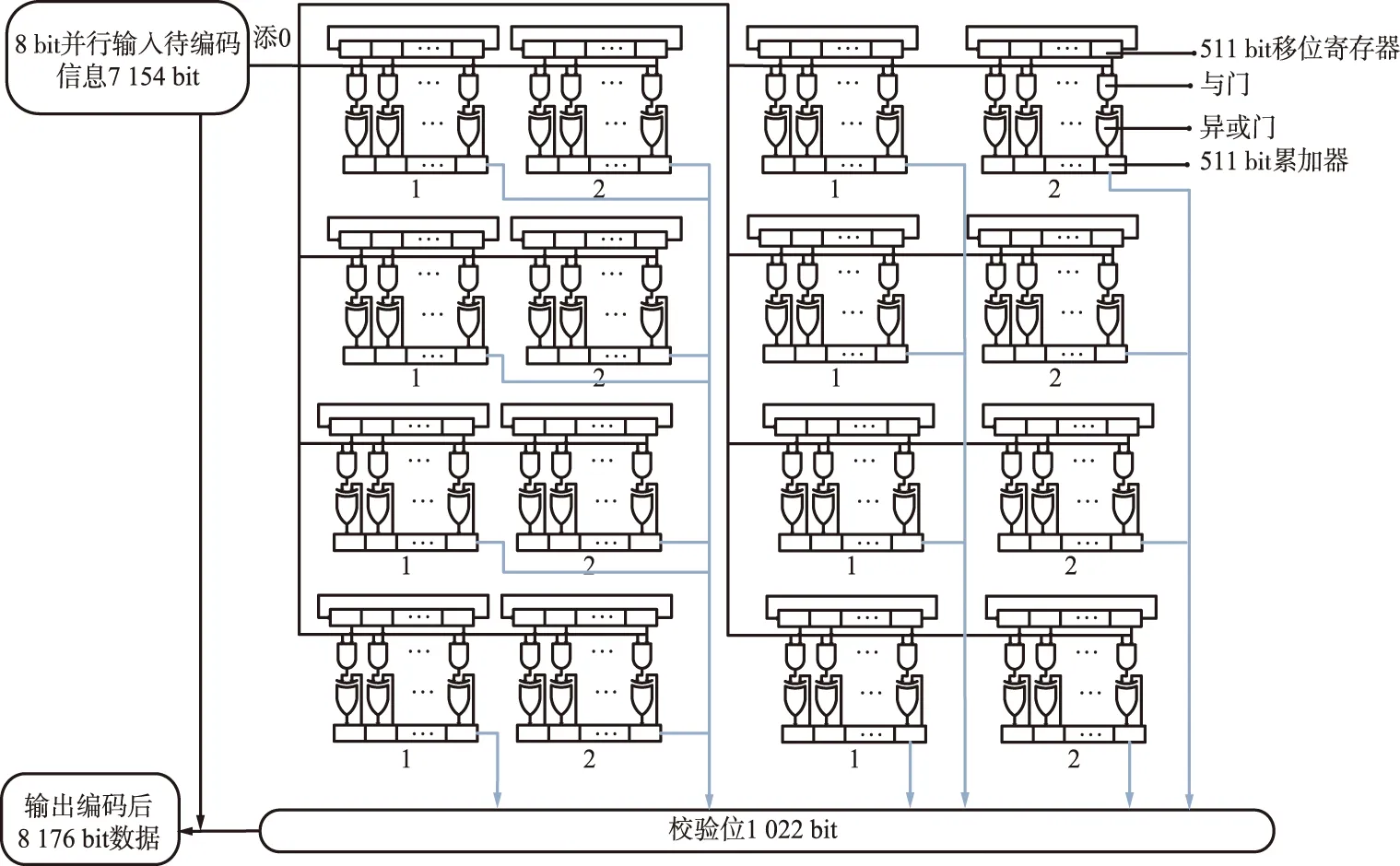

数据传输时使用7/8码率的(8 160,7 136)LDPC编码方案。该方案推荐使用的校验矩阵H的第一大行和第二大行均属于准循环低密度奇偶校验码(Quasi-Cyslic LDPC,QC-LDPC)[15],采用简单的移位寄存器即可实现编码计算,有利于硬件电路的实现。

LDPC编码单元由6个功能单元组成,如图6所示,包括时钟单元、帧头检测单元、数据预处理单元、LDPC编码单元和输出处理单元。其中,帧头检测单元检测数据帧格式是否符合设计要求,该模块检测到帧头1ACFFC1D后给出使能信号控制下一级数据预处理模块开始工作。数据预处理单元完成对数据的并串转换以及填充等处理,使码字长度符合生成矩阵的基矩阵格式后,再送入编码核心单元进行编码。

图6 载荷数据编码流程Fig.6 Payload data coding process

编码单元通过信息位码元求出校验位码元。由文献[16]中对LDPC编码算法原理的推导可知,计算校验位即计算信息位码元序列与生成矩阵的非单位阵部分做矩阵乘法运算的结果,G矩阵为系统码矩阵,G=[IkQ]生成码字C表示为C=q·G,q为待编码数据。

在实际设计中使用移位寄存器累加(Shift Register Adder Accumulator,SRAA)编码电路来实现运算。在综合比较了串行编码和并行编码的优缺点后,本文采用了改进结构的8位并行编码方案,在提高编码速率的前提下减少了资源的消耗。具体设计的并行编码结构如图7所示。

图7 8位并行编码结构Fig.7 8-bit parallel coding structure

编码完成后,使用Cortex高码率接收机(High Data Rate Receiver,HDR)对编码调制后信号的误码率进行测试。在Eb/N0>4.0 dB时,误码率小于10-6,满足设计需求。

2.4 DQPSK调制解调

调制部分采用DQPSK体制,利用前后相邻2个码元的相位差传递数据,以解决解调过程中的相位模糊、相位翻转的问题。在FPGA内将原始绝对码经过差分编码后变成相对码,再将差分编码后的I,Q两路基带信号送入正交调制单元完成载波调制。在FPGA内通过SPI通信配置射频调制芯片ADRF6720内部寄存器,使输出增益达1 dBm,载波中心频率为1 521.5 MHz。

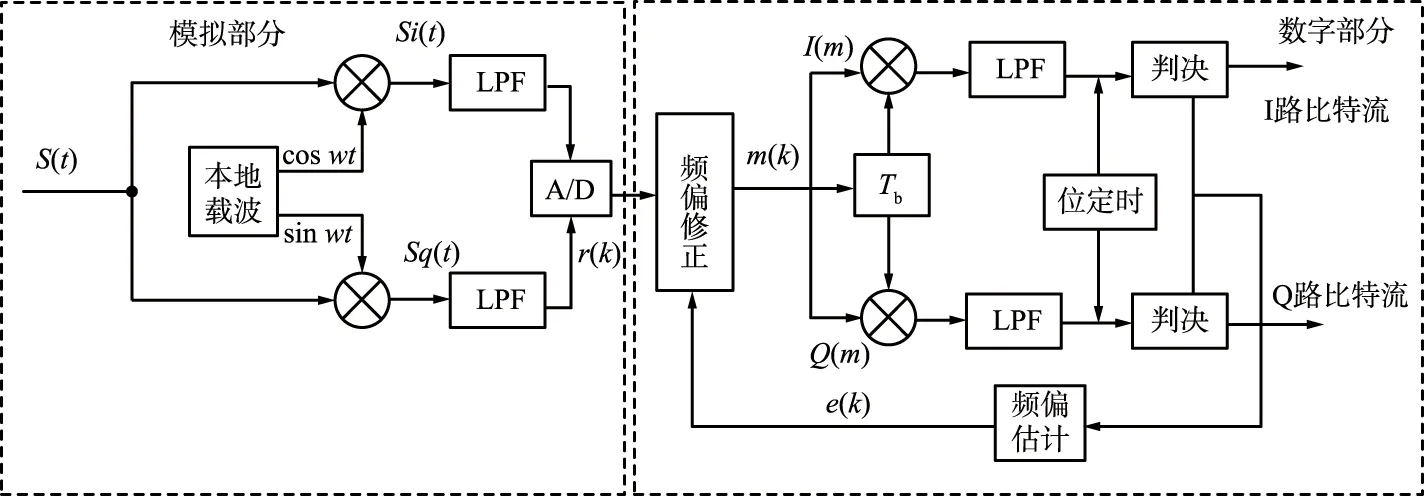

解调部分采用非相干解调以克服信号衰落变化大、频移特性变化大的缺陷[17]。零中频解调的结构如图8所示。

图8 零中频解调结构Fig.8 Homodyne IF demodulation structure

模拟部分中MAX2112对载波下变频后输出16 MHz中频信号,经模数转换芯片采样后得到I,Q两路信号,送入FPGA进行非相干解调。数字解调模块中的延时处理使用移位寄存器实现,对滤波后的输出信号延时一个符号周期16个采样点。将AD采集的输入信号I路经Hillbert滤波器后变为相位差π/2的2路信号I(m)与Q(m),分别与延时Tb后的信号相乘,相乘后的信号经低通滤波器后再进行后续位同步判决过程,完成非相干解调。

低轨卫星与地面之间存在高速的相对运动,因此在解调时需要考虑多普勒效应导致的频率相位偏移的影响。根据计算,可得500 km处该卫星过境时,多普勒频移约为±50 kHz,为了避免多普勒效应导致的接收信号相位差的错判[18],接收端采用反馈环路进行修正的算法对多普勒频偏实现补偿。如图8的数字部分结构所示。

不考虑噪声影响,未校正前的r(k)=A(k)exp[j(φk+θk)],在解调模块中与延时一个周期后的信号相乘得到:

D(k)=r(k)·r(k-Ts)=As(k)exp[j(Δφ+Δθk)],

(2)

式中,Δφ为在发送端相距Ts时刻的调制信号的相位差信息;Δθk为相距Ts时刻之间的信息由频偏引起的相位偏差,Δθk=2π·Δf/fs。

(3)

将e(k)送回频偏修正模块与未校正的信号相乘,得到修正后的m(k):

m(k)=r(k)·e(k)=A(k)exp(jφk)。

(4)

此时多普勒频偏的影响被消除。该方法能够消除的最大频偏由硬判决Δφ估计值精度决定,实际测试表明,本设计完成修正后能够正确解调±100 kHz频偏的信号。

3 测试结果

基带单元所有编码、调制、解调及和卫星系统间的通信接口等功能均在FPGA芯片的XC5VSX50T-2FFG1136I 中完成。

整个收发系统有较高集成度,系统采用整板SMT的封装结构。基带信号处理电路照片如图9所示。

图9 数字信号处理板照片Fig.9 Digital signal processing board

射频接收与发射模块采用介电常数稳定的微波板材制成独立模块再焊接到信号处理单元母板上,以隔离射频模拟电路和数字电路之间的干扰。

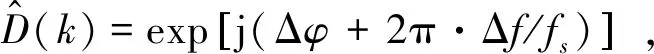

基带电路输出特性的测试结果如表2所示。

表2 基带电路输出特性Tab.2 Baseband circuit output characteristics

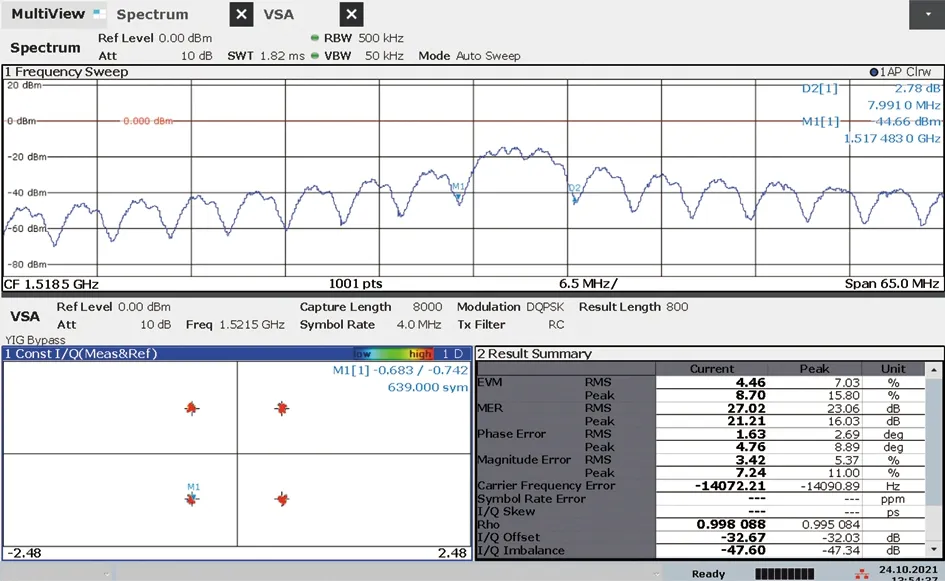

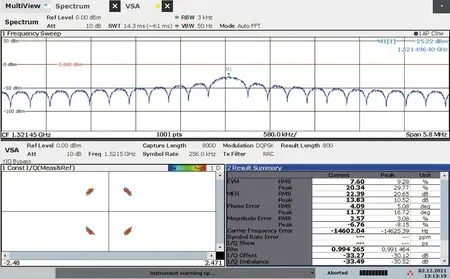

8 Mb/s和512 kb/s码率的DQPSK调制信号星座图和矢量误差幅度(EVM)如图10和图11所示。

图10 8 Mb/s LDPC+DQPSK调制频谱及星座图Fig.10 8 Mb/s LDPC+DQPSK modulation spectrum and constellation diagram

图11 512 kb/s RS-CC+DQPSK调制频谱及星座图Fig.11 512 kb/s RS-CC+DQPSK modulation spectrum and constellation diagram

EVM分别为4.5%和7.6%,满足应用性能指标,幅度误差分别为3.42%(0.29 dB)和2.57%(0.22 dB),相位不平衡度分别为1.63°和4.09°,完全满足CCSDS的幅度误差(小于0.5 dB)和相位不平衡度(小于5°)要求。误码率测试借助运行在电脑端的模拟数据发送软件和数据解帧软件完成,通过对比统计编码调制前的发送数据和解调解码后的数据,计算出前向和反向链路的误码率。实际通信测试中,前向链路实测误码率稳定在1.2×10-6~1.5×10-6,此时接收信号的Eb/N0约为13 dB;反向链路实测误码率为10-7~10-6,均小于CCSDS标准规定的10-5,满足通信链路的可靠性要求。

数字板的零中频接收模块通过数模转换芯片AD9744实现AGC,FPGA内对ADC采样的输出进行峰峰值检测,再由软件设定判决,实时输出增益控制字控制AD9744的输出电压幅值实现AGC,最终动态增益范围可达79 dB。对射频信号接收灵敏度进行测试,在Eb/N0为18 dB时,接收灵敏度为-80 dBm。整板功耗为8 W左右,满足低功耗设计需求。

4 结束语

本文实现了天海中继载荷数字基带电路单元的设计。根据实际需求完成了硬件电路研制和软件程序的测试。研究了载荷前向链路在不同工作模式下的信道编码及调制解调功能,根据数据链路特点实现了工作模式的自动切换。根据信道特点,优化了LDPC编码算法以及对解调过程中的多普勒频移进行了校正。测试结果表明,基带电路单元能够满足低轨卫星通信前向和反向链路的工程应用需求。设计的数字基带处理单元仅支持固定码速率的数据传输,在后续的研究中,将结合可变编码调制(Variable Coding Modulation,VCM)技术进一步提高信号的传输效率。