基于PowerPC的数据存储及回放系统实现

常旷博,刘文魁,孟景涛,王 涛,冀云成

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.中国人民解放军61768部队,海南 三亚 572099;3.中国人民解放军63769部队,陕西 西安 710032)

0 引言

在当前的测控系统中,对数据和信号处理的能力需求不断攀升,传统的数字信号处理系统渐渐不能满足实时高速的数据与信号处理需求。因此设计了一种基于PowerPC的数据存储及回放系统,结合可擦除存储(Flash)芯片和现场可编程门阵列(FPGA)芯片,实现了AD采样数据的实时存储和转发,同时,可以将存储的采样数据通过DA进行回放,以满足不同情况下对数据及信号处理的要求[1]。

1 概述

1.1 PowerPC

PowerPC处理器是摩托罗拉和IBM共同研发的精简指令集计算机(Reduced Instruction Set Computer,RISC)体系结构的处理器,它具有速度高、功耗低、计算能力强的特点。目前Freescale(飞思卡尔,摩托罗拉半导体)的PowerPC占据的嵌入式处理器市场最大,在军品市场中最受青睐。本系统采用Freescale公司生成的MPC8349E处理器[2]。

1.2 VxWorks

VxWorks是美国WindRiver公司开发的一款嵌入式实时操作系统,其良好的持续发展能力、高性能的内核、开放的体系结构、友好的用户开发环境以及对工业标准的支持,使它在嵌入式实时操作系统领域占据重要的一席之地,也使它成为目前世界上最先进的高性能实时操作系统之一[3]。VxWorks 的主要优点是多任务抢占调度、快速上下文切换、低中断延迟和快速灵活的通信机制;而且,其内核可根据需要进行裁减,并支持多处理器通信机制,使得多节点间通信容易编程[4]。

1.3 国内外研究现状

目前,国内有关PowerPC处理器方面的研究大多体现在信号处理、PCI总线相关技术等方面,多应用于国防领域和通信领域。基于PowerPC架构的存储系统已经有所应用,如基于PowerPC架构的信号处理与存储嵌入式系统等。国外对于此方面的技术开发已经走在了前端,但由于PowerPC的开发资源并不丰富,开发仍然具有一定的难度,国内基于PowerPC的应用技术仍需要进一步的提升和完善。

1.4 方法的先进性

基于PowerPC的数据存储及回放系统,通过FPGA进行阵列管理的存储方案,其先进性在于:

① 硬件架构易于实现;

② 具有高速串行数据总线接口,可实现高传输带宽;

③ 在FPGA中对数据进行分路并行存储到多个Flash矩阵中,可实现数据横向位宽的提升和纵向数据容量的提高,从而实现高速数据与信号的处理[5]。

2 系统设计

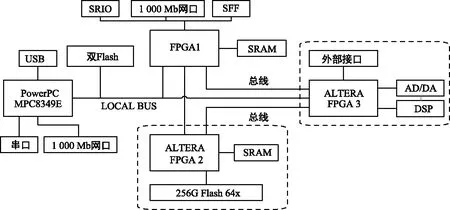

整个系统由PowerPC模块、Flash存储模块、AD/DA模块、通信模块等组成。其中,PowerPC模块运行VxWorks实时操作系统,负责管理Flash存储系统,控制数据的写入和读取,同时利用以太网接口将数据传输给上位机。Flash存储模块用于记录上位机传输的数据或AD采集的数据,也可以读取数据并利用DA进行数据的回放;AD/DA模块用于采集和回放数据;通信模块利用以太网口将数据传输给其他设备或系统。

系统的整体原理图如图1所示,使用了MPC8349E处理器、2个256 MB Flash芯片、3个FPGA芯片,以及由64片4 GB Flash芯片组成256 GB的存储阵列。其中AD/DA模块、通信模块与以往的数字信号处理系统差别不大,主要进行PowerPC子系统和Flash存储子系统的设计。

图1 系统原理图

3 PowerPC子系统

3.1 修改BSP

在以MPC8349E处理器为基础的硬件板上运行VxWorks操作系统,需要编写与硬件对应的板级支持包(BSP)。BSP的主要功能在于配置系统硬件使其工作于正常的状态,以及完成硬件与软件之间的数据交互,为操作系统及上层应用程序提供一个与硬件无关的软件平台[6]。

本系统采用的PowerPC型号为MPC8349E,因此以ADS834X评估板的BSP为基础,根据本系统的实际硬件情况进行修改,主要修改的内容如下:

① 系统内存的相关配置参数:内存大小、时钟相位、内存起始地址等;

② 系统的Flash大小;

③ 添加所需外设设备的驱动程序,主要包括:串口、以太网口、USB等接口;

④ TFFS文件系统的相关驱动。

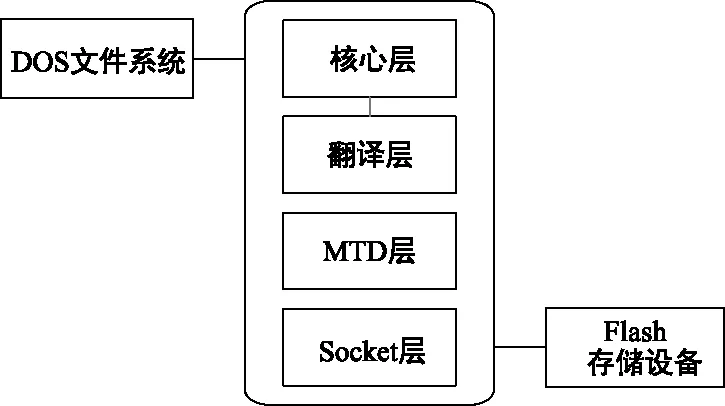

闪存文件系统(True Flash File System,TFFS)是和VxWorks兼容的一种M-Systems Flite实现方式,可以在系统Flash存储设备上构造一个基于DOS的文件系统,从而使文件操作方式像MS-DOS文件系统一样。TFFS 由核心层和3个功能层(翻译层、MTD层、Socket层)组成,如图2所示。

图2 TFFS文件系统结构图

翻译层主要实现TFFS和dosFs之间的高级交互功能,根据Flash芯片类型,本系统采用了NAND-based技术的翻译层[7]。在BSP文件中包含sysTffs.c文件,同时修改其内容如下:

#define INCLUDE_MTD_CFISCS

/ * CFI/SCS */

#define INCLUDE_TL_FTL

/ * FTL translation layer */

#define INCLUDE_TFFS_BOOT_IMAGE

/ * include tffsBootImagePut() */

BSP文件修改完成后,编译生成Bootrom映像文件,通过WindRiver ICE2仿真器将该映像文件写入板卡上的Flash芯片中存储,MPC8349E处理器上电启动后,执行Flash芯片上的Bootrom启动程序,初始化硬件板卡的CPU、内存、串口、以太网口等硬件设备,为接下来加载VxWorks操作系统做必要的准备。

3.2 生成系统映像

VxWorks操作系统启动时的工作流程如图3所示,其中标注了每项任务所需用到的BSP文件名称[8]。

图3 操作系统启动顺序图

图3中,usrAppInit()函数用于用户编写自己的应用程序,在本系统中该函数主要实现了以下任务:

① Task_Command_Receive():建立TCP服务器,等待上位机连接,连接成功后接收上位机的控制命令并根据命令调用相应的函数,包括Flash操作等;

② Task_Status_Info():建立TCP服务器,等待上位机连接,连接成功后将该Socket用于发送VxWorks系统的状态及应用数据;

③ HK_Flash_Main():控制FPGA对Flash进行各种操作,包括读写数据、获取Flash状态、Flash擦除等。

用户应用程序任务编写完成后,使用WindRiver公司的workbench集成开发环境对添加了用户应用程序的操作系统进行编译,生成一个带符号表的相应的VxWorks操作系统镜像文件,这个操作系统运行之后会自动处理用户事先定义好的任务。

3.3 操作系统加载

VxWorks操作系统有3种加载方式:

① 由Bootrom 引导通过网口或串口将操作系统映像下载到RAM;

② 将操作系统映像直接烧入ROM,运行时将映像拷入RAM 中运行;

③ 操作系统映像的指令部分驻留在ROM 中运行,仅将数据段部分拷入RAM。

在本系统中,采用第一种方式加载操作系统,使用网络加载的方式进行操作系统加载,这种加载方式需要在生成BSP文件时,将config.h文件中的DEFAULT_BOOT_LINE定义如下:

"mottsec(0,0)host:vxWorks

h=192.168.1.1

e=192.168.1.12

u=8349

pw=1234

tn=mpc8349"

连接一个串口线至上位机,将上位机的文件服务器按上述参数进行配置,同时启动超级终端。硬件设备加电后,Bootroom输出上述代码中的提示信息,显示在超级终端上,然后通过超级终端使用命令行配置网络信息及VxWorks操作系统映像文件的网络路径,就可以通过网络直接上载操作系统映像文件,从而完成操作系统的加载与启动[9]。

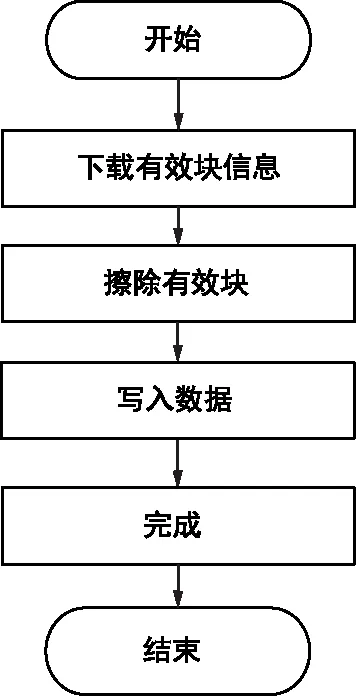

4 存储子系统

存储子系统由FPGA和64片4G容量的Flash芯片组成。VxWorks操作系统使用TFFS文件系统来进行管理,由FPGA控制具体的操作,如读取数据、擦除块、写入数据等。Flash阵列的组织结构如图4所示[10]。整个Flash芯片阵列的建立、管理、使用过程描述如下。

图4 Flash阵列组织结构

4.1 建立坏块表

对于每一片Flash芯片,其出厂时都存在坏块,根据Flash的硬件特性,在写入数据前需要先擦除对应的块,然后才能向该块写入数据[11]。坏块是可以被擦除的,但是不能被写入数据,因此,需要将Flash存储阵列里的每一个Flash芯片的坏块找到,在管理存储数据时跳过这些坏块,避免存储数据写入错误[12]。

从Flash芯片中确定坏块的位置是由FPGA具体实现的。结合Flash存储阵列的连线方式和芯片手册中关于坏块的确定方法,具体流程如图5所示。获取了所有坏块数据之后,将坏块数据写入文件形成坏块表[13]。

图5 坏块表建立流程图

4.2 建立老化表

老化表表示Flash存储阵列中每个Flash芯片的块的属性,由于每片Flash由8 192个块组成,因此老化表由8 192个块的属性表组成。建立如下的结构体表示老化表:

typedef struct wom

{ unsigned int used:1;

unsigned int bad:1;

unsigned int erasetime:30;

}wom_t;

typedef struct wom_col

{ wom_t Wom[8192];

}wom_col_t;

typedef struct wom_row

{ wom_col_t Wom_Col[col];

}wom_row_t;

typedef struct wom_table

{ wom_row_t Wom_Row[row];

}wom_table_t;

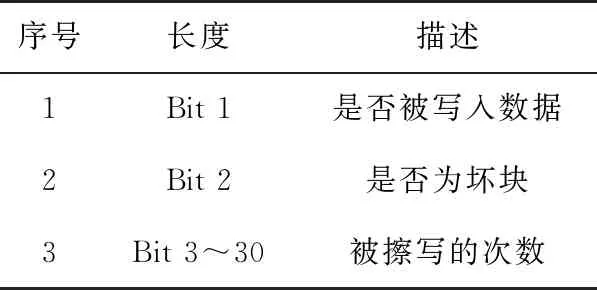

老化表建立完成后,读取坏块表的块信息初始化老化表,确定整个Flash存储阵列中的坏块与好块,为接下来选择有效块做准备。老化表块属性如表1所示。

表1 老化表块属性

4.3 建立有效块

为了提高系统的性能,Flash存储阵列采用并行流水线操作,每次操作都是一个片选所对应的有效块[14]。通过建立坏块表和老化表,在选择有效块时可以从0~8 192顺序选择,同时考虑到块的好坏、是否已经被写入数据以及擦写的次数(延长使用寿命)等因素进行有效块的选择。

有效块的数据结构如下:

typedef struct blkinfo

{ unsigned int row:8;

unsigned int col:8;

unsigned int blkaddr:16;

}blkinfo_t;

typedef struct blk_col

{ blkinfo_t Blkifo[16];

}blk_col_t;

typedef struct blk_row

{ blk_col_t Blk_Col[16];

}blk_row_t;

typedef struct blk_table

{ blk_row_t Blk_Table[2];

}blk_table_t;

4.4 数据管理

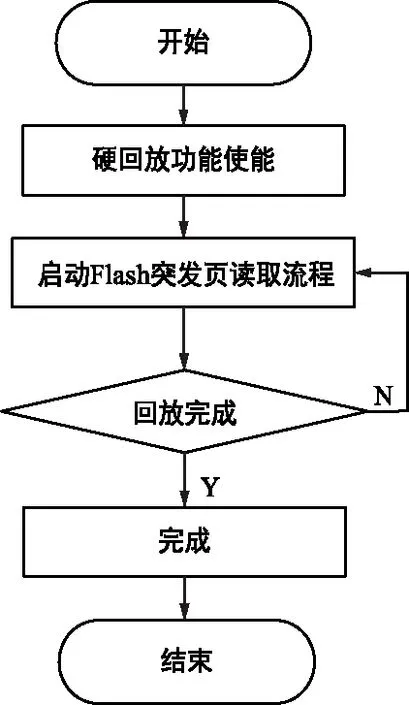

数据记录到Flash存储阵列中的流程如图6所示。存储的采样数据进行回放的流程如图7所示。数据转储的流程如图8所示。

图6 数据写入流程

图7 数据实时回放流程

图8 数据转储流程

5 实验验证

基于PowerPC的数据存储及回放系统已经应用于网络交换板解决方案中,形成了相关的数据采集记录回放系统产品,在多个嵌入式实时信息处理系统中得到应用。网络交换板接口主要有:DDR配置、Flash文件系统、千兆以太网接口、万兆光模块、RS232调试串口、LED接口、光模块、温度监控模块以及电压监测模块等。实现的功能有:存储器容量2 GB DDR3,数据总线宽度为64 bit,Flash共有256 MB,支持两路千兆网络自动备缓功能,支持两路万兆网络自动备缓功能。调试串口为用户提供每通道1路RS232调试接口,通过PC机上的超级终端来调试用户程序,支持LED运行状态指示,提供温度和电压监测功能。该网络交换板可以支持巨型帧协议(64 kB),网络时延<10 ms,后端RJ45为10/100/1 000 MB自适应,后端光纤网络1 000/10 000 MB自适应,能检测板卡电流、电压、温度等信息,并通过SPI口上报给K7等,满足各项技术指标要求,累计供货数量超过1 000块,产品整体质量稳定,得到了顾客的充分认可,证明了本系统的正确性和有效性。

6 结束语

基于PowerPC的数据存储及回放系统,结合Flash芯片和FPGA芯片,构建了一种具有强实时性、以标准文件系统进行存储管理的大容量高速率数据存储及回放系统。其创新在于具有标准硬件架构、稳定可靠,具有标准的文件系统进行存储,数据访问、数据转发简单易行。此外,采用VxWorks嵌入式实时操作系统,软件实时性也能得到保证。本文实现了AD采样数据的实时存储和转发,可以将存储的采样数据通过DA进行回放,满足了测控系统中,实时高速的数据与信号处理需求,有效提升了测控系统的数据和信号处理能力[15-18]。

——信号处理