SiC MOSFET 器件单粒子烧毁仿真分析

李林欢,曹荣幸,黄 鑫,孟 洋,刘 洋,韩 丹,李红霞,郑 澍,曾祥华,薛玉雄

(扬州大学 电气与能源动力工程学院,扬州 225127)

0 引言

更高效率以及更高功率密度的功率器件是半导体技术发展的重要方向之一。近年来,新兴的宽禁带半导体材料以其优越的特性为半导体功率器件技术领域带来了新的发展动力,其中SiC 的禁带宽度是Si 的2 倍以上,击穿场强是Si 的10 倍多,导热系数约是Si 的2.5 倍,饱和电子漂移速度是Si 的2 倍。这些特性使得SiC MOSFET 器件具有耐高压、高频率、高功率密度等优势,在一些应用领域开始逐步取代Si 基功率器件。

在航天、核工业领域的应用中,SiC MOSFET器件(文中简称“器件”)会受到辐射环境的影响。相比Si 基器件,SiC MOSFET 器件具有较强的抗总剂量能力。但是,SiC MOSFET 器件对单粒子效应比较敏感,尤其是在截止态时由于粒子入射导致的大电流,器件可能发生导致永久性破坏的单粒子烧毁(SEB)。地面单粒子试验是研究器件单粒子效应的常用技术手段,可以较为精准地评估器件的单粒子效应阈值电压,但是试验资源及成本限制常导致辐照条件及器件偏置等数据点数量有限。而采用TCAD 并结合试验结果验证优化的单粒子效应建模仿真可以灵活调节辐照条件和器件偏置条件等参数,获得更为全面的器件安全工作区域,且能从载流子浓度、电流密度、电势、电场等综合电参数分布方面系统研究单粒子烧毁机理,从而便捷地开展单粒子效应防护设计及验证。

自2000 年以来,国内外基于重离子试验和仿真手段开展了SiC 基MOSFET 器件单粒子效应的研究,建立了器件SEB 的试验方法与仿真模型,并于近十年根据试验结果和半导体工艺器件仿真(TCAD)测试了其安全工作电压以及SEB 截面,初步揭示了SiC MOSFET 的SEB 规律。但是在器件SEB 机理解释方面缺少对器件内部电参数微观变化的分析,不利于揭示器件SEB 的损伤物理机制。

本文基于有利于揭示器件内部电参数微观变化的TCAD 平台,开展SiC MOSFET 器件单粒子烧毁仿真分析,研究器件内部SEB 的敏感区域、安全电压范围及器件发生SEB 时电参数的分布,基于模拟仿真结果进一步研究器件SEB 的防护方法。

1 器件模型构建及仿真参数设置

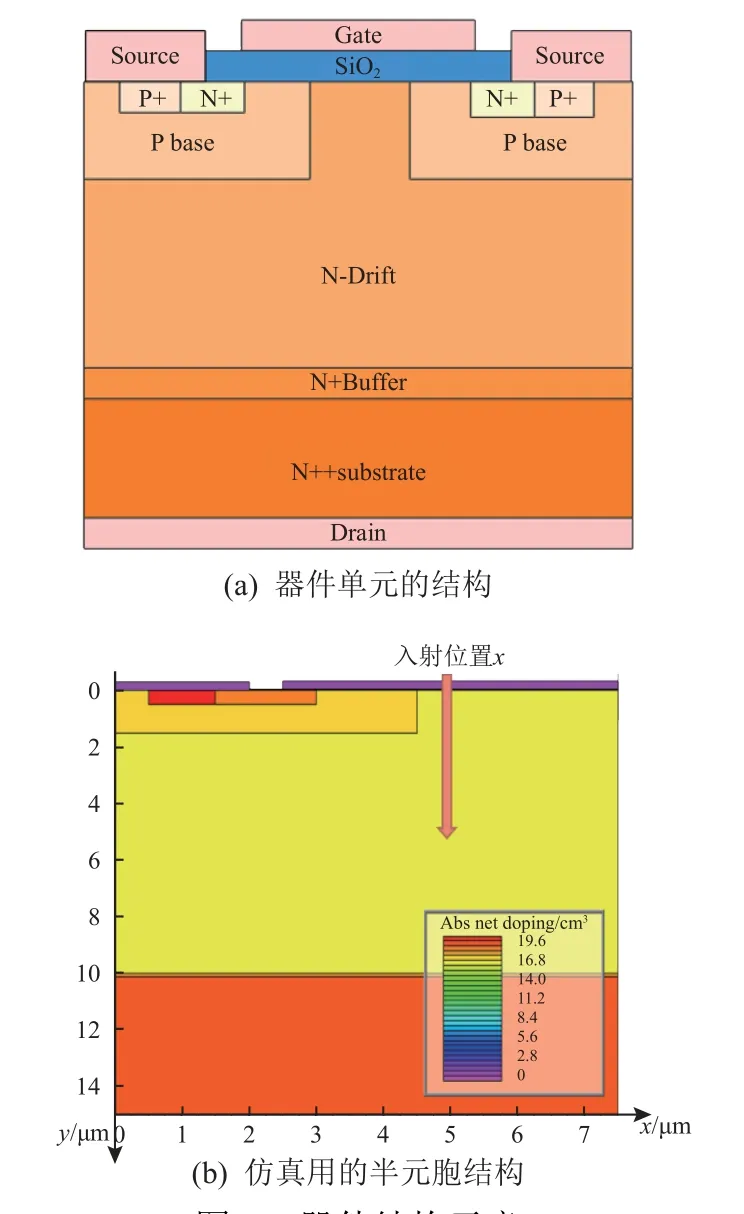

参考国内某厂商典型的1200 V SiC MOSFET建立器件的工艺结构模型,其中:功率器件工艺结构为垂直结构,其栅极和源极位于器件的顶部,而其漏极位于器件的底部,如图1(a)所示;电学仿真时所使用的半元胞结构的横向宽度为7.5 μm,纵向高度为15 μm,栅氧化层的厚度为0.06 μm,在衬底与漂移区之间有一个缓冲层,厚度为0.1 μm,其余各区域的尺寸及掺杂浓度范围等信息如图1(b)所示。

图1 器件结构示意Fig. 1 Schematic diagram of the device structure

本文仿真所选用的物理模型有SRH 复合模型、Auger 复合模型、CVT 集成模型、Fermi-Dirac 载流子统计模型、BGN 模型和碰撞离化模型。

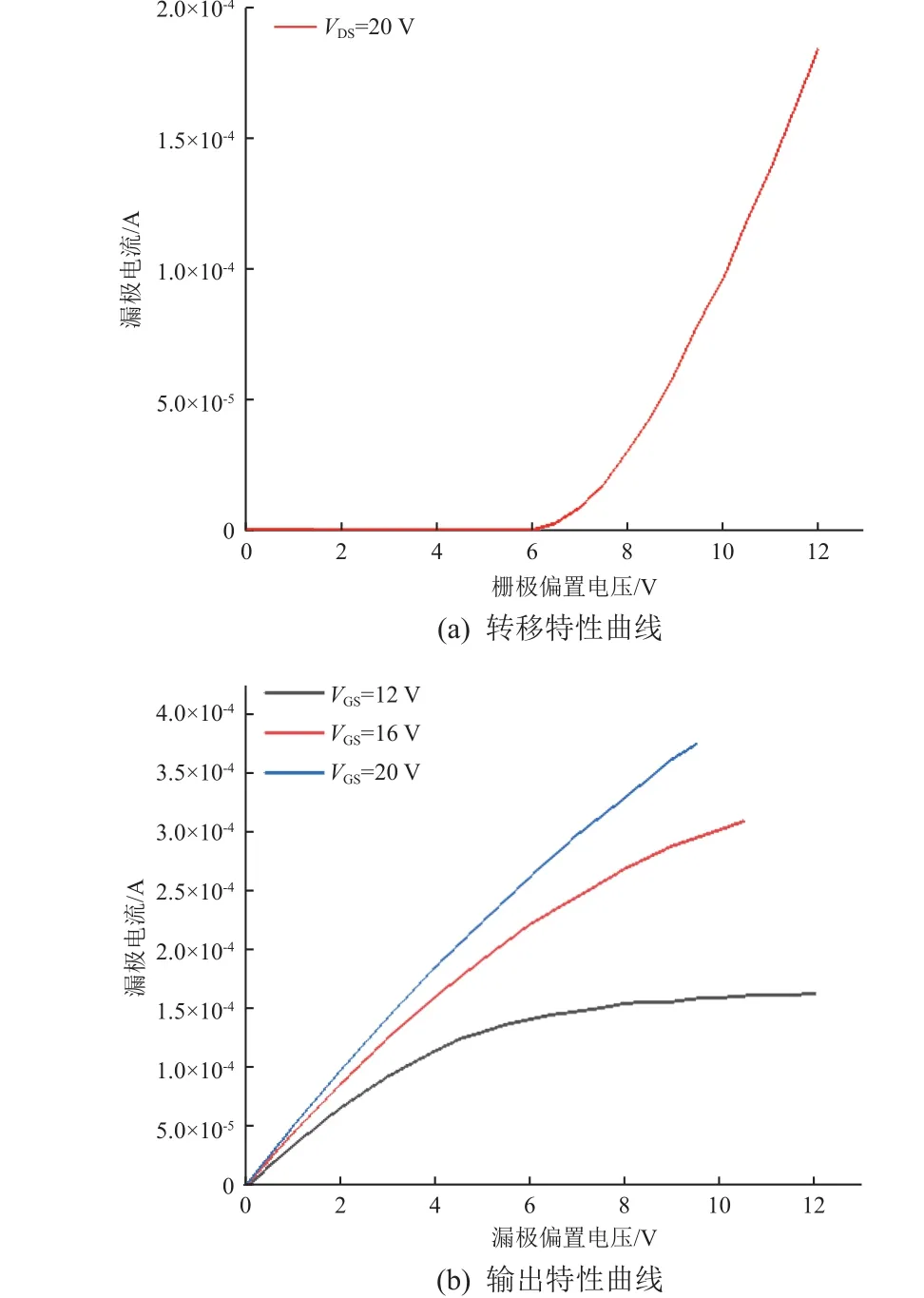

根据上述典型物理方程和器件电学模型,对器件进行电学特性仿真,得到漏极偏置电压=20 V时的转移特性曲线(见图2(a))和栅极偏置电压分别为12 V、16 V 和20 V 时的输出特性曲线(见图2(b)),其中阈值电压约为6 V。

图2 器件电学仿真特性Fig. 2 Electrical characteristics obtained by TCAD simulation of the device

在单粒子烧毁仿真中,入射粒子为垂直入射,入射位置为图1(b)横坐标。入射粒子和产生电荷脉冲基本参数的选取参考SiC MOSFET 典型数值,具体为:粒子入射产生的电荷径迹半径为0.05 μm,入射深度为15 μm;LET 值75 MeV·cm/mg;电荷生成脉冲的峰值时刻为4 ps;电荷生成的脉冲宽度为4 ps。这些参数是依据SiC 器件中常用数值设置的初始值,后续可根据单粒子试验结果进行验证和优化。

2 器件单粒子烧毁仿真结果与分析

2.1 阈值电压及敏感区域分析

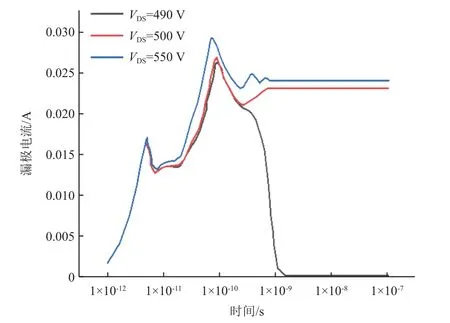

器件SEB 的漏极电流随时间变化的仿真结果如图3 所示,此图对应的仿真器件结构中栅极偏置电压=0 V(器件处于截止态)、漏极偏置电压分别为490 V、500 V 和550 V,以及入射位置=5 μm、入射粒子LET=75 MeV·cm/mg 的条件下。粒子入射后,在一定的漏极电压下,若漏极电流能够恢复至粒子入射之前的水平,则意味着器件未发生SEB;若漏极电流增大并维持在一个较高数值,则意味着发生SEB 失效。从图3 可以看出:当漏极电压为490 V 时,漏极电流最终降到0;当漏极电压为500 V 时,电流值最终保持在一常数值,表明器件发生了SEB;随着漏极电压的增大,漏极电流的最终数值也在增大。因此该器件发生SEB的阈值电压约为500 V。

图3 器件发生SEB 前后漏极电流随时间的变化Fig. 3 The drain current in the device before and after SEB

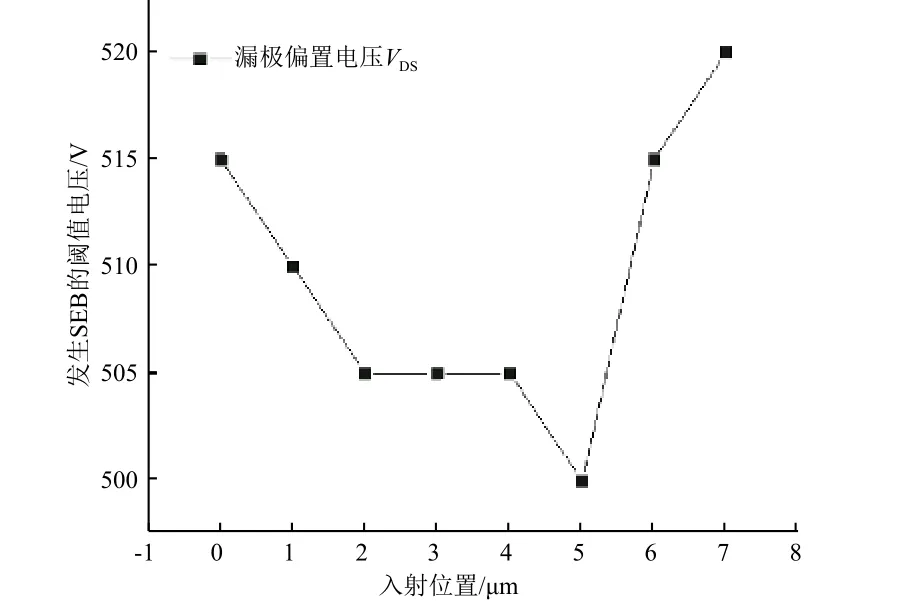

为了进一步研究器件发生SEB 的敏感位置,在=0 V(器件处于截止态)、入射粒子LET=75 MeV·cm/mg 的条件下,对不同入射位置下器件的烧毁特性进行了仿真,结果如图4 所示。

图4 不同入射位置的SEB 阈值电压Fig. 4 SEB threshold voltage in different incident positions

可以看出,器件内部SEB 的敏感性不一样,并且当入射位置=5 μm 时,器件发生SEB 的阈值电压最低,说明在该位置(Pbase 基区附近),器件更容易发生SEB。这是因为当粒子入射器件后产生的空穴会向源极漂移,使得Pbase 基区的电压增加,距离Pbase 基区越远,产生的空穴漂移到源极就要经过更远的距离,相比其他入射位置会产生更大的压降,使得寄生双极结型晶体管(BJT)更加容易导通;另一方面,当粒子入射器件后,如果入射径迹靠近器件内部寄生BJT 所在的位置,则会使粒子入射所产生的空穴在外部电场的作用下更快地向源极漂移,由空穴的漂移运动所产生的瞬态电流会在Pbase 基区产生更大的压降,也会使得寄生BJT 更加容易导通。

2.2 器件单粒子烧毁特性及机理分析

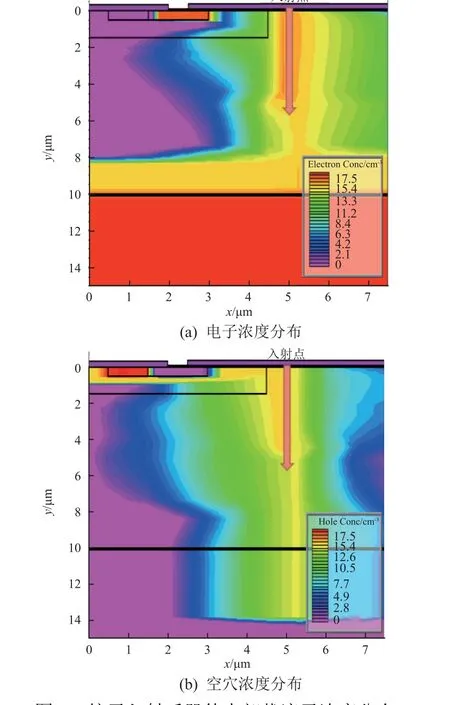

在器件单粒子烧毁敏感性研究的基础上,进一步研究了器件单粒子烧毁的机理。图5 所示为粒子入射后器件内部电子浓度分布和空穴浓度分布。经分析:当器件处于关闭态时(=0 V),高能带电粒子入射器件后,会在粒子入射径迹上沉积能量,从而产生电子-空穴对;当漏极加正向偏置电压后,器件内部产生的电场方向由漏极指向源极,电离产生的载流子在电场作用下发生漂移运动,产生瞬态脉冲电流;电子沿着电场相反方向向漏极漂移,因此电子在衬底和缓冲层附近有较高的浓度(图5(a));空穴沿着电场方向穿过Pbase 基区向源极和P+源区漂移,因此空穴在源极和P+源区附近有较高的浓度(图5(b))。

图5 粒子入射后器件内部载流子浓度分布Fig. 5 Distributions of carrier concentration inside the device after incidence of particles

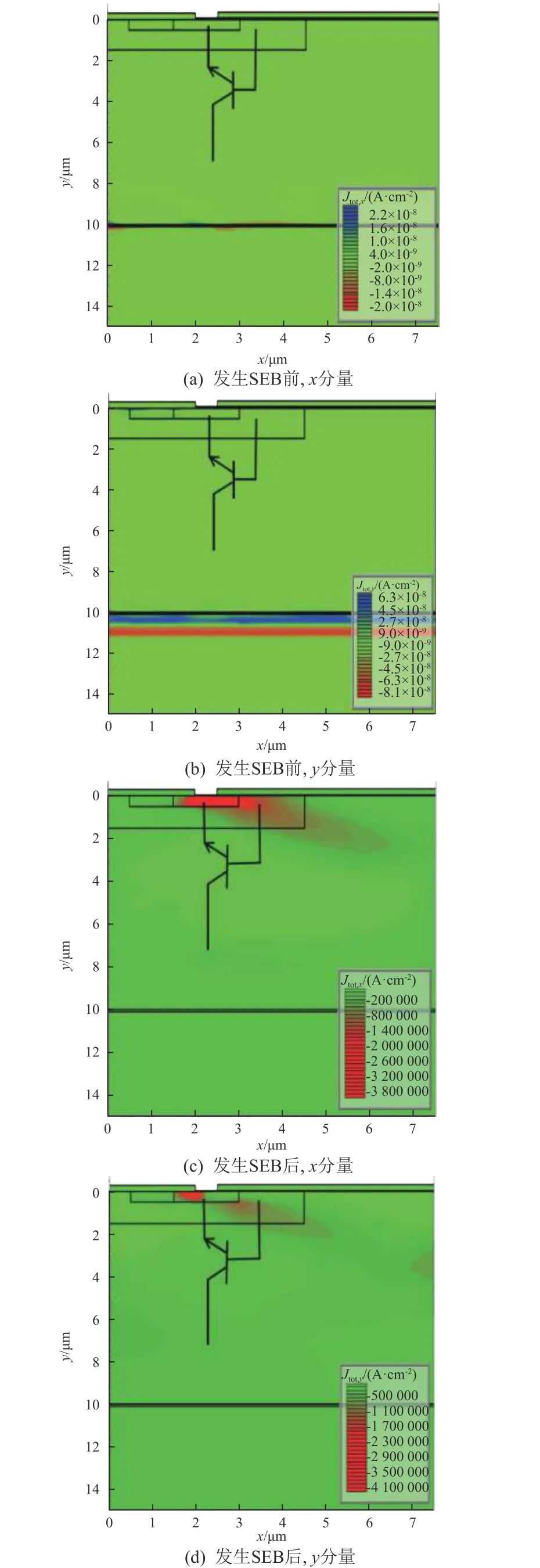

分析在=0 V(器件处于截止态)、=500 V条件下器件发生SEB 前后的电流变化特性,结果如图6 所示。

图6 器件发生SEB 前后的电流密度分布(VDS=500 V)Fig. 6 Distributions of current density in the device before and after SEB (VDS=500 V)

SiC MOSFET 器件结构中本身就存在一个寄生BJT,器件的N+源区、Pbase 基区和N-漂移区分别对应寄生BJT 的发射极、基极和集电极。在器件正常工作时N+源区和Pbase 基区是短接的,所以寄生BJT 处于关闭状态,衬底缓冲层附近会有10A/cm数量级的漏电流,电流密度、分量分别如图6(a)和图6(b)所示。当器件关断且漏极电压较高时,如果有高能带电粒子入射器件,由于寄生BJT 的放大效应,产生的正反馈作用使寄生BJT的发射极(N+源区)电流密度倍增,达到10A/cm数量级,电流密度、分量分别如图6(c)和图6(d)所示,导致漏极电流急剧增大,直至烧毁器件。

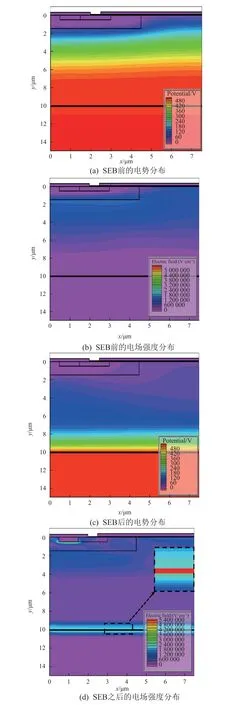

分析了器件截止状态下(=0 V)发生SEB 过程中的内部电势和电场强度的变化特性,结果如图7 所示。在=500 V 时,纵向电势是缓变分布的(图7(a)),寄生BJT 集电极的空间电荷区边界在Pbase 基区处,可以看出电场强度分布集中在此区域附近(图7(b))。当高能粒子入射器件之后,器件内部沿粒子径迹产生大量的电子-空穴对,在这些载流子的漂移电流的作用下器件纵向的电势不再是缓变分布,而是在N+缓冲层和N-漂移区界面处发生了突变(图7(c))。这一突变是由于N-漂移区浅掺杂,寄生BJT 集电极的空间电荷区边界会扩展到N+缓冲层的边缘,因而在N+缓冲层的边缘处形成了一个很大的电场,所以这个界面处的电场强度极高;随着寄生BJT 双极放大作用与缓冲层电场强度增大形成的正反馈使电流加大,这一界面处的电场强度也随之上升(图7(d)),最终发生了雪崩倍增效应,导致器件烧毁。从图7(d)可以看出,在N+缓冲层附近电场强度较大,约为5.4 MV/cm,在P+源区/Pbase 基区的电场强度也很大,约为4.2 MV/cm,这是由于当漏极加较高的偏置电压(=500 V)时,在粒子入射后,空穴沿着电场方向穿过Pbase 基区快速向源极和P+源区漂移,使得P+源区/Pbase 基区附近载流子迁移率较大,所以此处的电场强度也很高。上述两个位置的电场强度均超过了SiC 材料的击穿场强(3 MV/cm),因此这两个区域也就是发生SEB 的敏感区域,其中N+缓冲层具有最高的场强,是决定器件SEB 敏感性的关键区域。

图7 器件发生SEB 前后的电势电场分布图(VDS=500 V)Fig. 7 The electric potential and electric field distribution in the device before and after SEB (VDS=500 V)

3 器件防护设计分析

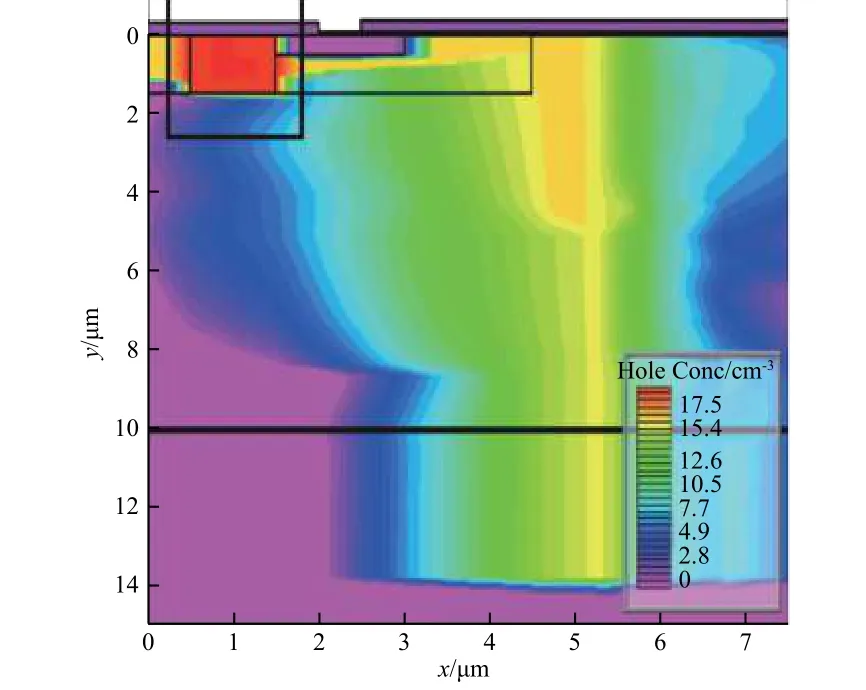

通过2.2 节器件中SEB 的机理分析,为提高器件发生SEB 的阈值电压,借鉴Si 基器件中的防护设计方法,本文提出一种防护设计思路:将P+源区向下延伸至Pbase 基区。对此防护结构的器件进行了SEB 的仿真分析,结果如图8 所示。

图8 P+源区扩展后,空穴浓度的分布特性Fig. 8 Distributions of hole concentration when the P+ source region is extended

由图8 可见,将P+源区向Pbase 基区延伸后,带电粒子入射后产生的空穴可以快速从P+源区漂移到源极,空穴在P+源区附近有较高浓度分布。因此这一结构可以有效减少空穴向寄生BJT 敏感区域漂移的数目。由于当重掺杂的P+源区向下延伸到Pbase 基区时降低了寄生BJT 基区的电阻,使瞬态电流通过寄生BJT 基区时在Pbase 基区产生的压降变小,所以抑制了寄生BJT 的导通。在=0 V(器件处于截止态)、入射粒子LET 值为75 MeV·cm/mg的条件下,对加入防护设计后的结构进行了仿真,结果如图9 所示。

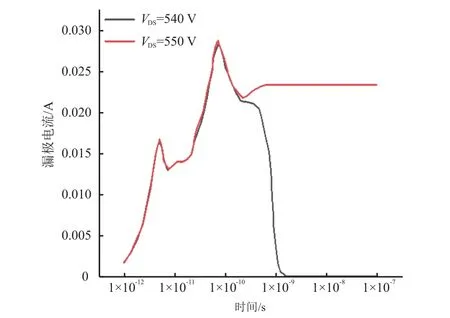

图9 P+源区扩展后,器件发生SEB 前后的漏极电流随时间变化Fig. 9 The variation of the drain current against time before and after SEB when the P+ source region is extended

由图9 可见,器件的漏极电压在540 V 时未发生SEB,在550 V 时才发生SEB,而防护设计前的器件在=500 V 时就发生了SEB。由此可见,经过这样的防护设计后,SEB 的阈值电压提高了近50 V。对这种防护设计后的结构进行了电学特性仿真,发现其转移特性和输出特性均保持不变,表明防护设计前后的电学特性是一致的,且可以通过提高离子注入能量实现P+源区扩展,具备器件工艺设计可行性。

4 结束语

本文利用TCAD 对SiC MOSFET 器件进行了单粒子烧毁仿真分析,发现粒子入射最敏感位置时器件发生SEB 的阈值电压在500 V,与文献报道的SEB 阈值电压典型试验值400~600 V 相符合,表明本文的仿真模型具有较高的精度。同时,仿真获得了器件的电子-空穴浓度分布、电流密度分布、电势及电场分布特性,模拟结果表明器件发生SEB 的原因是寄生晶体管的正反馈作用导致缓冲层和基区的电场强度(5.4 MV/cm 和4.2 MV/cm)超过SiC 材料击穿场强(3 MV/cm)。此外,模拟发现将P+源区的深度向下延伸至Pbase 基区底部时,器件发生SEB 的阈值电压从500 V 提高到近550 V。后续将从工艺试验层面对此防护设计进行验证。