高性能众核处理器芯片时钟网络设计

马永飞,高成振,黄金明,李 研

(上海高性能集成电路设计中心,上海 201204)

0 概述

目前,主流高性能微处理器基于同步时钟系统进行设计开发。时钟信号为芯片内同步系统提供参考时间,是同步时序逻辑运行的基础[1-3]。时钟信号通常是芯片中扇出最大、负载最重、传输距离和覆盖面最广的信号。时钟偏斜对时序逻辑电路正确运行性能具有重要的制约作用。在通常情况下,时钟网络的偏斜由设计及工艺与应用环境两方面因素影响决定。设计因素包括各时钟节点负载平衡性以及从时钟源端输出的传输距离、传输级数与布线方式。工艺与应用环境因素包括工艺角、片上工艺偏差、工作电压与温度[4-5]。为保证芯片内同步时序逻辑在各种不同的工艺角下均能正常稳定工作,在传统的高性能处理器设计中,设计人员通常致力于开发时钟偏斜更小、抗工艺偏差能力更强的平衡时钟网络,以获得较高的工作频率[6-8]。

高性能众核处理器芯片中通常包含多个不同的时钟域,且随着系统对性能要求的日益提高,高性能众核处理器芯片规模不断提高,时钟网络规模越来越大,使得芯片时序收敛及功耗优化的压力日益凸显[9-11]。如何降低芯片时钟网络功耗并克服时钟网络分布受片上偏差(On-Chip Variation,OCV)影响而导致的时钟偏斜(clock skew)问题,从而加速设计时序收敛,成为高性能众核处理器芯片设计中的重要研究方向[12-13]。本文在传统时钟网络结构及混合时钟网络结构的基础上,构建一种新型的多源时钟树综合(Multi-Root Clock Tree Synthesize,MRCTS)结构,并通过实验探究MRCTS 设计对时钟系统的功耗优化作用。

1 相关研究

1.1 传统时钟网络结构

根据时钟网络的结构特点,传统的时钟网络设计主要有树状和网状两种结构。

常见的时钟树结构包括:H-Tree,Fanout Balance Tree,Binary Tree 和Fishbone[14-16]。H-Tree 时钟树的skew 小,抗OCV 能力强,但设计要求严格,通常作为芯片核心高频时钟的全局互连[17]。基于EDA 工具时钟树综合(Clock Tree Synthesis,CTS)的时钟树通常为Fanout Balance Tree 结构,其作为芯片内模块级时钟互连。Binary Tree 时钟树相比H-Tree 时钟树的设计要求低,但仍存在较为严格的负载平衡要求,通常作为芯片时钟的全局互连。Fishbone 时钟树的长度短、延时小,受OCV影响小,通常作为芯片内模块级时钟互连。图1为4 种常见的时钟树结构。

图1 常见的时钟树结构Fig.1 Common clock tree structure

一个完整的时钟网状结构(MESH)包含前驱层、短接层以及负载层,如图2 所示。MESH 时钟结构与时钟树结构的根本区别在于存在时钟短接层。通过前驱层所有驱动单元的输出短接以及大量冗余的时钟连线,MESH 时钟结构确保了负载层的各负载单元可以就近连接到短接层MESH 网,有效降低了时钟网络的延时偏差,消除了时钟传播的延时奇异点。然而,为了有效控制MESH 网的时钟延时,必须提供充足甚至远超负载规模需要的前驱层驱动器和驱动点,同时为保证短接层的时钟MESH 网的平衡与完整,需要添加大量冗余的时钟线,这会造成布线资源浪费的同时增加时钟网络的负载和时钟功耗,此外前驱层驱动器间的延时偏差带来的短路直通同样会带来大量的时钟功耗损失。

图2 MESH 时钟结构Fig.2 MESH clock structure

1.2 H-Tree+MESH 混合时钟网络结构

随着集成电路设计规模的不断提高,片上时钟网络规模、时钟类型和复杂的时钟结构使得单一网络结构的时钟设计遇到了严峻挑战,设计人员开始寻求在性能、功耗等方面进行折中,提出了混合结构的时钟设计方法[18-19]。在借鉴树状和网状两种时钟网络结构特点的基础上,根据芯片不同时钟域的特点与设计需要,构建多种不同的混合时钟网络结构以应对特定的设计需求。以FINFET 工艺下,ChipA众核处理器芯片为例,其运算核心SCORE(约含88 000 个触发器)的时钟网络设计采用H-Tree+MESH 混合时钟网络结构。

在该芯片设计中,SCORE 采用层次化设计方案,包含3 个综合子模块(ES、MUX、EMDIS)及2 个定制SRAM 阵列(LDM、L1IC)。核心时钟域SClk 分两层实现:第一层是SCORE 上层的H-Tree 及类H-Tree 的多级时钟树;等二层是模块内的MESH 时钟网。采用MESH时钟结构,保证了运算部件内的时钟延时平衡,利用具有高度一致性的H-Tree及类H-Tree时钟树兼顾运算核心簇内和簇间的时钟网络偏斜,并最终确保SCORE 乃至芯片内SClk 时钟域的整个时钟网络具有较高的抗工艺波动与片上工艺偏差的能力,为时序收敛设计及芯片稳定运行提供重要支撑。

在MESH 时钟网络设计中,针对相关时钟驱动点(Tap)至时钟驱动单元(Gater)输入端以及Gater单元输出至负载触发器(或Latch)时钟端的延时分别制定设计目标,并通过对时钟网络进行Hspice 仿真分析验证时钟树设计是否达到预期指标要求。SCORE 最终设计结果显示,虽然部分Tap 点至Gater 驱动的延时略有超标,但整个时钟网络的设计质量高于既定指标要求,Tap 点输入至负载单元的最大延时仅为85.8 ps,时钟延时偏差少于12 ps(仅占时钟周期的2.5%)。

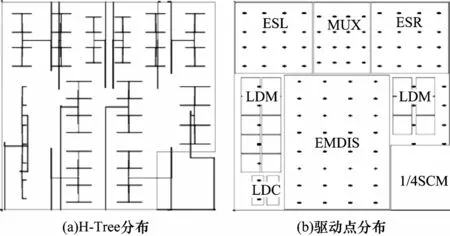

图3 为SCORE 上层最后一级H-Tree 时钟树以及相关时钟驱动点的分布情况。图4 为SCORE 综合子模块内部门控时钟的MESH 网络分布情况。虽然基于MESH 的模块级时钟网络设计可以实现极低的时钟偏差,具有极高的抗工艺偏差的能力,但是各主流EDA 工具对于MESH 时钟网络的设计支持度不够,需要精细的人工定制设计,耗费大量的人力和时间。定制化时钟树设计方法难以适应芯片设计周期的需要,更无法有效利用useful skew 实现对关键路径的优化。此外,随着集成电路设计工艺提高,为追求更高的性能,片上集成度进一步提升,芯片时钟网络规模进一步增加。仿真结果显示,模块级时钟树设计面临布线资源需求大幅增加的严峻挑战。为满足项目进度、布线资源、时序及功耗优化等多方面的需求,亟需研究新型时钟网络结构。

图3 SCORE 上层H-Tree 及时钟驱动点分布Fig.3 H-Tree and clock driver point distribution above SCORE

图4 SCORE 中的MESH 时钟网络Fig.4 MESH clock network in SCORE

2 新型时钟网络设计

Synopsys 公司的布局布线工具ICC2 针对FINFET工艺下的时钟网络设计多源时钟树结构(Multi-Source Clock Tree Structure,MSCTS)[20-21],如图5 所示。全局(Global)网络包含全定制实现的H-Tree 时钟树、全局Tap 驱动器及其驱动的MESH 网,局部(Local)时钟树包含与MESH 相连的各子模块的Tap 点及其驱动的标准CTS 时钟树。相比于传统的CTS 时钟树结构,多源时钟树结构具有更高的抗片上工艺偏差能力并可实现更高的时钟性能。

图5 MSCTS 时钟网络结构Fig.5 MSCTS clock network structure

在MSCTS 中,以MESH 时钟结构作为全局与各子模块时钟的互连通道,为提供较为充足与分布合理的Tap驱动点,全局时钟上MESH结构的密集度要求较高,占用较多的高层金属资源,大幅压缩了各综合子模块的布线资源,降低了模块的设计绕通性。同时,大量冗余的MESH 时钟网络极大地提高了时钟网络的负载,产生了较大的时钟功耗。本文在H-Tree+MESH 混合时钟网络结构设计的基础上,通过对标准多源时钟树设计策略的深入研究,结合新一代众核处理器芯片面积大、核心时钟网络分布广的特点,对多源时钟树结构进行改进,改进的时钟网络结构如图6 所示。

图6 MRCTS 时钟网络结构Fig.6 MRCTS clock network structure

改进的时钟网络结构同样分为全局和局部两个部分:全局网络包含全定制实现的H-Tree 时钟树及全局Tap 驱动器;局部时钟树基于MSCTS 流程以各子模块Tap 点为时钟输入源进行多源时钟树综合。将改进后的网络结构称为多源时钟树综合(MRCTS)结构,其与MSCTS 的显著区别在于取消了全局时钟网络末端的MESH 时钟,局部时钟与全局时钟通过Tap 点直接相连。在设计时可以根据不同底层模块的规模大小和各自特征,确定各自模块Tap 点的数量和分布位置,从而达到控制局部时钟树的规模,实现各局部时钟树的延时基本相当,达到控制整个时钟网络skew 的目的。

采用改进的网络结构可以降低中间的MESH 网带来的大量时钟功耗和对布线资源的额外占用,同时仍保有MSCTS 时钟结构的优点:全局的H-Tree 时钟树保证了全芯片不同区域间clock skew 稳定可控,局部的CTS 时钟树可以合理利用useful skew 进行关键路径的时序优化,实现时序收敛。全局和局部设计者的分工更加明确,在保证质量的同时,有利于缩短设计迭代周期,提高设计效率。

3 实验设计与结果分析

3.1 基于MRCTS 时钟结构的实验设计

为探究MRCTS 时钟结构的可行性及其对时钟网络的影响,基于SCORE 的设计代码、布局规划和Tap 点分布,采用MRCTS 时钟树设计策略,分别进行3 个子模块的综合实验。在采用MRCTS 时钟树设计策略进行SCORE 的时钟树综合设计时,首先设置时钟树的主体级数,然后根据模块中利用useful skew 进行时序收敛的需要,对不同的时序分组分别调整时钟树的目标级数,在合理利用useful skew 的同时实现对时钟树延时和级数的有效控制。表1 为SCORE 中子模块采用MRCTS 时钟设计的基本数据。

表1 SCORE 时钟网络基本数据设置Table 1 Setting of basic data of SCORE clock network

图7为SCORE中基于MRCTS的时钟树布线规划,其中从每个Tap 点发出的放射状线条表示每个Tap 点到对应负载端(包括触发器、Latch、定制Latch 阵列时钟端)的连接关系。图8 为SCORE 中的MRCTS 时钟网络,可以看出与图4中的MESH时钟网络相比,MRCTS时钟网络对布线资源的占用大幅减少。

图7 SCORE 中基于MRCTS 的时钟树布线规划Fig.7 Clock tree route planning based on MRCTS in SCORE

图8 SCORE 中的MRCTS 时钟网络Fig.8 MRCTS clock network in SCORE

3.2 功耗分析结果

时钟网络的功耗由静态功耗、短路功耗和翻转功耗三部分组成[22],分别来自时钟驱动单元、时钟互连线以及时钟负载三方面,而影响时钟网络功耗的因素包含电源电压、时钟频率、时钟信号的跳变时间、门控方案、门控单元插入位置、时钟网络负载等。表2 对比了SCORE signoff 版(MESH 结构)与综合实验版(MRCTS 结构)时钟网络负载情况。

表2 时钟网络负载统计Table 2 Clock network load statistics

考虑到时钟网络功耗主要由动态功耗组成,而动态功耗的主体是开关功耗(Pswitch)。Pswitch计算公式如下:

其中:α为翻转率;Cload为负载电容;VDD为电源电压;f为时钟频率。开关功耗与时钟网络的负载电容、时钟频率成正比,与电源电压的平方成正比,即在电源电压和时钟频率相同时,时钟网络的功耗与时钟网络负载电容成正相关。

由此可以看出,基于相同代码与布局规划进行MRCTS 时钟树设计后,SCORE 时钟网络的总负载下降约11%,根据式(1)可以简单推算出,SClk 时钟域的模块级时钟网络功耗可以获得约11%的优化。

3.3 功耗实测结果

新一代ChipB 芯片设计采用更先进的第二代FINFET 工艺,同时为获得更优的能效,在SCORE 的设计中应用了MRCTS 时钟结构。相比于ChipA,SCORE的有效晶体管数由2.58×107增至3.33×107,增长了约28.9%,触发器数由8.77×104增至10.80×104,增长了约23.3%。为验证新型时钟网络设计对功耗优化的效果,分别选取5 颗ChipA 和ChipB 芯片进行时钟功耗测试,并将电源电压与时钟频率进行一致性折算,对比结果如表3 所示。从表3 数据分析结果可以看出,在触发器总量增加23.3%的情况下,采用MRCTS 时钟结构,SCORE 时钟网络功耗约降低了22.15%(折算相同电源电压和时钟频率)。

表3 ChipA 与ChipB 的SCORE 时钟网络功耗对比Table 3 Comparison of clock network power consumption of SCORE between ChipA and ChipB

4 结束语

本文分析高性能众核处理器芯片设计中的H-Tree+MESH 混合时钟网络结构,构建新型多源时钟树综合(MRCTS)结构并研究其对模块时钟网络功耗的优化作用。两款处理器芯片实测功耗的对比结果显示,在相同电源电压和时钟频率条件下,基于MRCTS的ChipB运算部件SCORE 的时钟网络功耗较ChipA 下降约22.15%。但由于新型MRCTS 时钟树结构中Tap 点的位置受限于H-Tree 时钟树结构,分布一般比较均匀且位置相对固定,Tap点位置调整对全局布线的影响较大,然而在实际设计中时序单元的分布不均匀,受逻辑设计和物理布局规划影响,相对分布均匀的Tap 点会导致各Tap 点驱动的Local 时钟网络负载不均衡,在部分情况下可能会严重影响最终的时钟树设计及模块时序收敛,因此后续将通过实时分析与调整Tap 点的分布和数量进一步优化时钟网络设计。