相干光接收机时钟恢复算法的FPGA实现*

金 鑫,杨 奇,敖学渊,张深茂

相干光接收机时钟恢复算法的FPGA实现*

金 鑫,杨 奇,敖学渊,张深茂

(华中科技大学光学与电子信息学院 武汉 430074)

低轨小卫星在进行相干激光通信时,需要实时解决发射端与相干光接收机之间存在的时钟偏差问题。分析了时钟偏差对相干光接收机性能的影响,设计了一种基于Gardner算法的并行化时钟恢复反馈环路来对时钟的偏差进行纠正,对各组成部分的原理进行了说明,并在现场可编程逻辑门阵列FPGA上实现了该算法,将5 GSa/s的采样信号在FPGA中以156.25 MHz主频,分为并行32路完成时钟同步处理,且实时时钟同步算法仅占用FPGA的590个自适应逻辑块和4个乘法器单元。同时,采用自研的集成化相干光通信模块,演示了10 Gb/s偏振复用正交相移键控PM-QPSK相干光通信系统实验。实验结果证明该方案能稳定地补偿本地采样时钟的频率和相位偏移带来的采样定时误差。以7%开销硬判决前向纠错码HD-FEC(Hard Decision Forward Error Correction)为门限,系统的灵敏度优于–51 dBm。

相干接收机;时钟恢复;Gardner算法;FPGA

引 言

近年来,传统的光通信网络飞速发展并且日渐成熟,“平面化”的通信网络结构开始向“立体化、多面化”的方向扩展。卫星通信网能够为地面通信网络无法覆盖的地区提供全天候的通信服务,已逐渐成为了全球通信网络中的重要组成部分。其中,相较于微波通信,卫星激光通信以其安全性高、抗干扰能力强、传输速率高和使用频带不受限制等优点,在低轨道小卫星构成的星座系统中得到了重要应用[1]。国内外的卫星光通信组网项目中,多采用BPSK、QPSK、16QAM等相干光通信的调制格式,通信速率在10 Mb/s~10 Gb/s[2]。

在实时相干光通信系统的接收端,平衡探测器输出的电信号经过模数转换器ADC(Analog to Digital Converter)采样,得到的数字序列进入现场可编程门阵列FPGA(Field Programmable Gate Array,)进行数字信号处理。其中,由于相干光接收机在完成ADC采样时,虽然收发端两个时钟的标称频率相同,但不是同一个晶振源,二者仍然存在一定的时钟偏差,这将导致ADC无法在最佳采样点进行信号采样,直接影响相干接收机的性能,从而导致信号无法正常恢复。因此,研究相干光通信系统中时钟恢复算法的FPGA实现,对高速相干光接收机来说是必不可少的。晏蕾[3]等人在FPGA上实现了基于Gardner定时误差算法和基于Farrow结构的内插滤波器构成的定时同步环路,并在符号速率为660 kbps的BPSK解调系统上进行了仿真,但是信号速率不满足小卫星的需求,而且未在FPGA上实现。KIKUCHI[4]提出自适应有限冲激响应滤波器,能够恢复突发模式下的时钟不匹配,然而它需要大量的抽头计算,使硬件实现复杂化。LIN[5]等人实现了并行匹配滤波和频域定时同步,但在实现中需要大量乘法器和加法器资源来设计并行傅里叶变换结构。周娴[6]等人提出了一种可大规模并行运算的全数字时钟同步方案并进行了仿真验证。赵亮[7]等人克服了传统Gardner算法只适用于二电平数字基带调制的局限性,提出了一种改进的定时误差检测和内插滤波器结构,实现了四电平全数字16QAM接收机的定时同步。邵子金[8]等人设计了一种基于Gardner算法的并行化时钟同步环路,但仅使用MATLAB进行了仿真,尚未在实时系统中实现以评估算法的性能。王利军[9]用FPGA实现了适用于突发通信的前馈时定时同步算法,该方案采用平方定时误差算法,并使用插值算法完成定时同步,但是需要ADC实现4倍过采样,限制了在更高速通信系统上的应用。AMADO S B[10]等人搭建了1.25 Gbit/s的QPSK相干光通信系统,并在FPGA上实时实现了并行化的时钟恢复算法和载波均衡算法,但是插值滤波器的实现需要的乘法器数量4倍于时钟误差检测模块,复杂度高。A. Josten[11]等人在FPGA上使用改进的Godard算法,在频率域实现了定时恢复,该算法仅需ADC达到8/7倍过采样率。ZHAO Shaohua[12]等人在频域上进行定时误差检测,在时域上调整采样点,并将定时调整分为整数和分数两部分,搭建了仿真平台对多种调制格式下的定时误差进行测试。HU[13]等人对Gardner算法进行了改进,用中间采样点的符号代替具体采样值,将设计的并行时钟同步算法在FPGA上实现后,在Modelsim中进行了仿真。HAO[14]等人提出了一种基于指数相关重排的并行先入先出FIFO(First Input First Output)存储器和串行数字时钟同步双反馈环路构成的联合方案,并在FPGA上实现了对20 Gb/s 16QAM系统的时钟同步。

实时系统中,时钟同步算法的实现主要考虑ADC采样率和算法的计算复杂度两个因素。如上所述,对于时钟同步的算法及其FPGA实现,有许多研究成果。但是对基于FPGA的实时相干光通信系统,自适应滤波器或者傅里叶变换实现复杂;在全数字时钟同步算法的并行化结构中,每条支路都需要一个数控振荡器与插值滤波器,这极大增加了硬件资源的消耗。因此,本文基于Gardner时钟误差检测算法在FPGA上实现了并行化的数模混合型时钟恢复方案,ADC只需达到2倍过采样率,用模拟器件压控振荡器VCO(Voltage Controlled Oscillator)代替数字插值滤波器和数控振荡器从而降低了FPGA实现难度和资源消耗。另外一方面,为了适应卫星光通信终端的小型化和集成化需求,本文自行研发的收发一体相干光通信电路板集成了FPGA芯片、ADC芯片、双偏振IQ调制器和集成相干接收机等器件,并在此基础上通过实验演示了一个10 Gb/s PM-QPSK(Polarization Multiplexed Quadrature Phase Shift Keying)相干光通信系统。实验结果表明,该方案能够稳定地补偿由于收发两端的时钟不同步带来的定时误差。

1 时钟恢复原理与方案设计

在相干光通信系统中,接收的信号需要经过ADC采样。由于接收端和发射端的时钟源是相互独立的,即二者的时钟频率和时钟相位一般不同,因此接收端的ADC无法保证在最佳采样点上进行采样,再加上本地时钟源自身的非理想性,会导致得到的异步序列存在相位误差,且不断累积,最终系统误码率BER(Bit Error Ratio)恶化,无法正常工作。

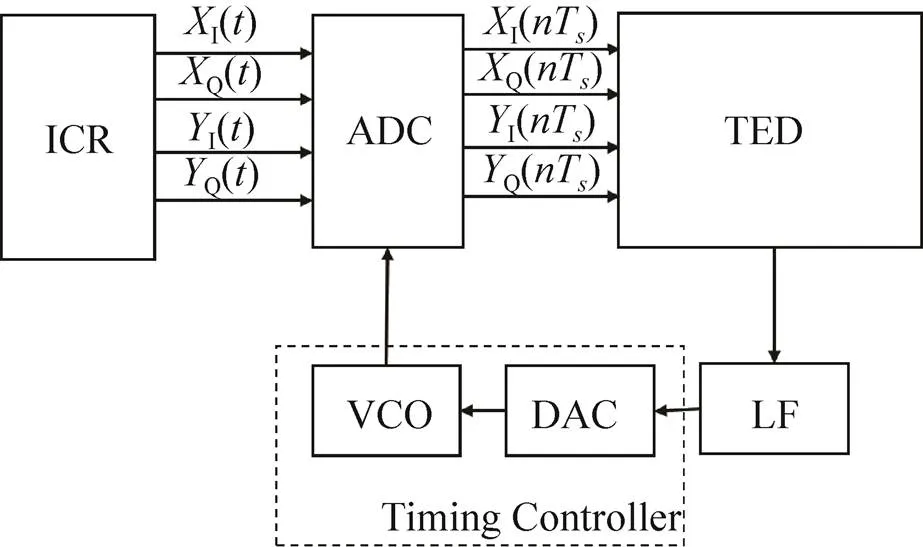

图1 数模混合型时钟恢复算法反馈环路

1.1 时钟误差检测器TED

常见的反馈式时钟误差估计算法有Mueller算法[15]、早迟门算法[16]、数字滤波平方算法[17]和Gardner算法[18]等,其中Gardner算法只需要ADC达到2倍过采样率,且具有结构简单、实现复杂度低和对于载波相位不敏感的优点而得到广泛的应用。本文采用的正是Gardner算法。

图2 并行化Gardner定时误差检测结构图

1.2 环路滤波器LF

信道和系统中的各种噪声会造成结果的抖动,因此得到时钟误差后,需要环路滤波器LF(Loop Filter)滤除噪声,得到平稳分量。本文采用比例-积分环路滤波器[19]跟踪频率和相位偏差。其中,比例环路LP(Loop Proportional)、积分环路LI(Loop Integral)和LF的输出分别如式(4)、(5)、(6)所示:

1.3 定时控制器Timing Controller

在全数字Gardner定时同步环路中,定时误差的校正采用插值滤波的方法实现,然而在FPGA芯片中对高速数据流进行插值滤波复杂度较高。因此,本文使用集成在FPGA开发板上的模拟器件VCO,并通过一个DAC驱动来改变本地时钟振荡频率,从而和数字域的时钟误差检测器以及环路滤波器构成数模混合型反馈环路。

2 实验装置

本文设计了一套PM-QPSK相干光通信系统,系统结构如图3所示。收发两端选用的FPGA芯片均为Altera Stratix Ⅴ系列的5SGSMD8K2F40C3。其中发射端用于调制的PRBS信号以及接收端的实时化时钟恢复算法都在FPGA中完成。图4(a)为实验平台的实物图。图4(b)展示了本文使用的自研集成数字相干模块。其中1为FPGA,2:为双偏振IQ调制器,3为集成相干接收机,4为模数转换器在系统的发射端,采用TSP-1000多通道可调谐光源作为载波光源,线宽小于100 kHz,产生波长为1550 nm的信号光和本振光。FPGA工作在频率为156.25 MHz的时钟下,产生64 bit的PRBS23序列,以电信号的形式通过4路IO口并经过功率放大器放大后,送入双偏振IQ调制器进行电光调制,其中4条支路上信号速率均为2.5 Gb/s。

图3 PM-QPSK相干光通信系统框图

图4 实物图

3 实验结果与分析

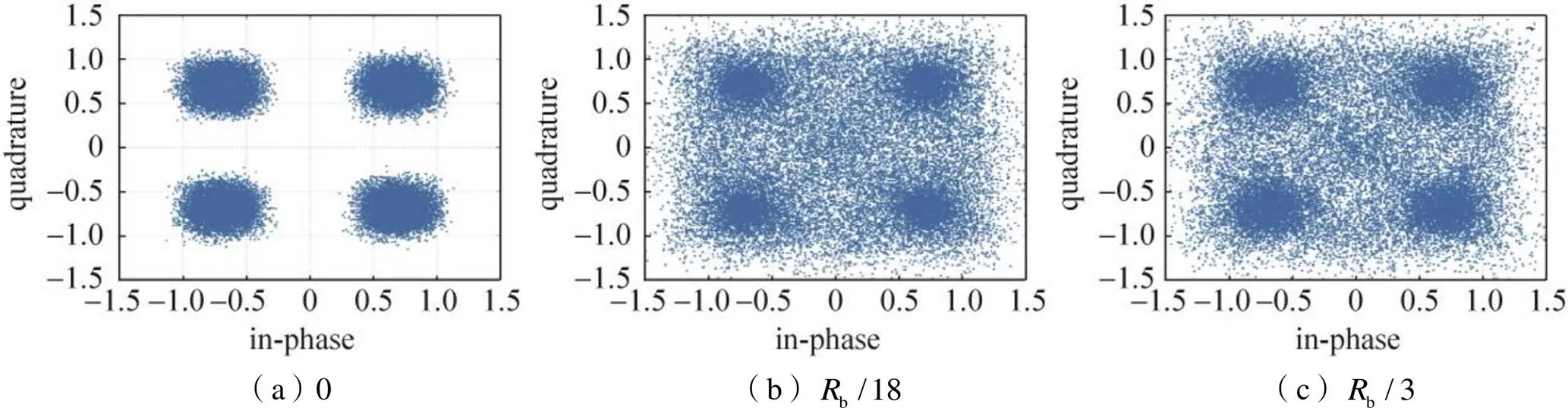

本文首先通过MATLAB仿真研究了时钟偏差对相干光通信系统性能的影响,图5和图6分别为采样时钟与相干发射机时钟存在固定相位差和固定频率差时的QPSK系统的星座图,其中b为码元时隙,b为码元速率。可以看到,随着采样时钟相位偏差的增大,信号的星座图越发弥散。而采样时钟的频率差会导致采样时刻偏差的周期性变化,对相干系统性能的影响更大。

图5 不同采样时钟相位差下的星座图

图6 不同采样时钟频率差下的星座图

通过SignalTapⅡ将时钟恢复反馈环路各部分的工作情况实时导入到MATLAB中,在MATLAB中采样信号进行降采样,从而每个符号获得1个采样点,最后再进行自适应均衡、载波恢复和QPSK解调。图7为在FPGA中加载时钟恢复算法前后,偏振态输出信号的星座图。由于采样点的偏移,图7(a)显示出没有完全恢复出原始信号。图7(b)的星座图展现了清晰的QPSK调制信号,经计算误码率为零,从而验证了FPGA中时钟恢复算法的有效性。

如图8所示在FPGA上加载时钟恢复算法,反馈环路经过一段时间的跟踪和捕获后,时钟误差检测器TED的输出即时钟的定时误差收敛在0附近,说明时钟的偏差得到了有效纠正,环路滤波器LF的输出和DAC的有效值均围绕某个确定值波动,这表明实时化时钟恢复算法收敛,反馈环路保持稳定。资源占用方面,时钟恢复算法在FPGA中仅使用590个自适应逻辑块ALMs(Adaptive Logic Modules)和4个DSP乘法模块。

图7 Y偏振态星座图

图8 时钟恢复反馈环路工作情况

最后测试了背靠背条件下,系统BER与接收光功率的关系如图9所示,利用可调节光衰减器,逐渐将接收机的接收光功率ROP(Received Optical Power)从–43 dBm降低到–51 dBm。当接收光功率为–48 dBm时,误码率约为1.45×10–4,低于KP4前向纠错码KP4-FEC(KP4-Forward Error Correction)FEC的门限(BER=2.4×10–4)。接收光功率为–51 dBm时的误码率为1.56×10–3,低于7%开销的硬判决前向纠错码HD-FEC(Hard-Decision-Forward Error Correction)的阈值门限(BER=3.8×10–3)。实验中所用的光功率计精度限制了更低接收机功率下的误码率测试,预计系统的灵敏度优于–51 dBm。

图9 系统BER与接收光功率关系曲线图

4 结束语

本文设计了一套10 Gb/s PM-QPSK相干光通信系统,在FPGA芯片上实现了并行架构的实时时钟恢复算法,并进行了实验验证。实验结果证明了时钟偏差的有效校正和定时反馈环路的稳定工作。以7 %开销HD-FEC为门限,系统的灵敏度优于–51 dBm。

[1] 刘向南, 李春才, 李晓亮, 等. 天地一体化信息网络空间激光通信新技术[J]. 遥测遥控, 2019, 40(1): 1–7.

LIU Xiangnan, LI Chuncai, LI Xiaoliang, et al. New technologies of space laser communication for the space-ground integrated information network[J]. Journal of Telemetry, Tracking and Command, 2019, 40(1): 1–7.

[2] 崔潇. 卫星光通信关键技术及发展态势分析[J]. 信息通信技术与政策, 2021(11): 65–72.

CUI Xiao. Analysis of key technologies and development trend of satellite optical communication[J].Information and Communications Technology and Policy, 2021(11): 65–72.

[3] 晏蕾, 余荣, 梅顺良. 全数字接收机中定时同步算法和实现[J]. 电子技术应用, 2005(12): 45–47.

[4] KIKUCHI K. Clock recovering characteristics of adaptive finite-impulse-response filters in digital coherent optical receivers[J]. Optics Express, 2011, 19(6): 5611–5619.

[5] LIN Changxing, ZHANG Jian, SHAO Beibei. A high speed parallel timing recovery algorithm and its FPGA implementation[C]// 2nd International Symposium on Intelligence Information Processing and Trusted Computing, 2011.

[6] 周娴. 100 Gbps PM-(D)QPSK相干光传输系统DSP算法研究[D]. 北京: 北京邮电大学, 2011.

[7] 赵亮, 李竞翔, 杜玉海, 等. 一种改进的符号定时同步算法的研究[J]. 电波科学学报, 2013, 28(4): 749–753.

ZHAO Liang, LI Jingxiang, DU Yuhai, et al. An improved symbol timing synchronization algorithm[J]. Chinese Journal of Radio Science, 2013, 28(4): 749–753.

[8] 邵子金, 冯磊, 张军, 等. 一种星间激光通信高速并行定时恢复算法设计[J]. 电子设计工程, 2018, 26(21): 86–89.

SHAO Zijin, FENG Lei, ZHANG Jun, et al. A parallel timing synchronization algorithm design for inter⁃satellite high speed laser communication[J]. Electronic Design Engineering, 2018, 26(21): 86–89.

[9] 王利军. 突发通信定时同步算法的FPGA实现[J]. 科技信息, 2013(21): 97–98.

[10] AMADO S B, FERREIRA R, COSTA P S, et al. Clock and carrier recovery in high- speed coherent optical communication systems[C]// Second International Conference on Applications of Optics and Photonics, 2014.

[11] JOSTEN A, BAEUERLE B, EPPENBERGER M, et al. 168 Gb/s line rate real-time PAM receiver enabled by timing recovery with 8/7 oversampling in a single FPGA[C]// Optical Fiber Communications Conference and Exhibition, 2017.

[12] ZHAO Shaohua, WANG Youzheng, QI Tingyu, et al. Parallel structure of all digital timing synchronization and realization of FPGA[C]// 3rd Advanced Information Technology, Electronic and Automation Control Conference, 2018.

[13] HU Jiao, ZHU Lichen, WANG Jianpeng. The implementation of high speed parallel timing synchronization algorithm based on FPGA[C]// 10th International Conference on Communication Software and Networks, 2018.

[14] HAO Xin, WU Qiuyu, WANG Zhaohui, et al. Parallel timing synchronization algorithm and its implementation in high speed wireless communication systems[C]// International Conference on Electronics, Information, 2019.

[15] MUELLER K, MULLER M. Timing recovery in digital synchronous data receivers[J]. IEEE Transactions On Communications, 1976, 24(5): 516–531.

[16] LOUVEAUX J, VANDENDORPE L, CUVELIER L, et al. An early-late timing recovery scheme for filter-bank-based multicarrier transmission[J]. IEEE Transactions on Communications, 2000, 10(48): 1746–1754.

[17] OERDER M. HEYR H. Digital filter and square timing recovery[J]. IEEE Transactions on Communications, 1988, 36(5): 605–612.

[18] GARDNER F. A BPSK/QPSK Timing-error detector for sampled receivers[J]. IEEE Transactions on Communications, 1986, 34(5): 423–429.

[19] MAYA J A, CASCO N A, RONCAGLIOLO P A, et al. A high data rate BPSK receiver implementation in FPGA for high dynamics applications[C]// Southern Conference on Programmable Logic (SPL), 2011.

FPGA implementation of clock recovery algorithm for coherent optical receiver

JIN Xin, YANG Qi, AO Xueyuan, ZHANG Shenmao

(School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China)

When low-orbit small satellites carry out coherent laser communication, it is necessary to solve the clock deviation problem between the transmitter and the coherent optical receiver in real time. In this paper, the influence of clock deviation on the performance of coherent optical receiver is analyzed, a parallelized clock recovery feedback loop based on Gardner algorithm is designed to correct the clock deviation, and the principle of each component is explained. The algorithm is implemented on FPGA by dividing the 5 GSa/s sampling signals into 32 parallel channels in the FPGA with the main frequency of 156.25 MHz to complete the clock synchronization processing, and the real-time clock synchronization algorithm only occupies 590 adaptive logic blocks and 4 multiplier units of the FPGA. At the same time, the self-developed integrated coherent optical communication module was used to demonstrate the 10 Gb/s PM-QPSK coherent optical communication system experiment. The experimental results show that the scheme can stably compensate the sampling timing error caused by the frequency and phase offset of the local sampling clock. The HD-FEC(Hard Decision Forward Error Correction) code with 7% overhead is used as the threshold, the sensitivity of the system is better than –51 dBm.

Coherent receiver; Clock recovery; Gardner algorithm; FPGA

TN929.11

A

CN11-1780(2022)04-0106-07

10.12347/j.ycyk.20220324001

金鑫, 杨奇, 敖学渊, 等.相干光接收机时钟恢复算法的FPGA实现[J]. 遥测遥控, 2022, 43(4): 106–112.

10.12347/j.ycyk.20220324001

: JIN Xin, YANG Qi, AO Xueyuan, et al. FPGA implementation of clock recovery algorithm for coherent optical receiver[J]. Journal of Telemetry, Tracking and Command, 2022, 43(4): 106–112.

国家重点研发计划项目(2018YFB1801303)

杨奇(yangqi@hust.edu.cn)

2022-03-24

2022-04-28

Website: ycyk.brit.com.cn Email: ycyk704@163.com

金 鑫 1995年生,硕士研究生,主要研究方向为光通信实时信号处理。

杨 奇 1981年生,教授,博士生导师,主要研究方向为超大容量、超高速、超远距离光传输和实时信号采集与信号处理等。

敖学渊 1996年生,博士研究生,主要研究方向为实时相干光通信系统。

张深茂 1996年生,博士研究生,主要研究方向为短距光纤通信和空间激光通信。

(本文编辑:潘三英)