不同基站计算架构Massive MIMO 基带能效建模和趋势研究

邓爱林,冯 钢,刘梦婕

(电子科技大学通信抗干扰技术国家级重点实验室 成都 611731)

碳排放增加导致的全球变暖已成为制约人类社会可持续发展的主要障碍,全球已有超过40 个国家和经济体正式宣布了碳中和目标[1]。中国提出2030 年前实现碳达峰,2060 年前实现碳中和。

对于移动通信行业来说,践行碳中和也已势在必行。移动通信行业在节能减排、绿色低碳发展方面进行了积极探索,一方面是为了彰显了通信行业的社会责任,另一方面是因为网络能耗支出在OPEX 的占比不断提升。5G 网络能效相比4G 提升了10~20 倍,但随着网络承载数据量的急剧增加,将导致5G 通信设备总能耗增长,基站能耗成为运营商实现碳中和目标的重要挑战。大规模多输入 多 输 出(massive multiple-input multiple-output,massive MIMO)是5G 系统的标志性技术,该技术利用大规模天线有效提高空口容量和频谱利用率。随着未来5G Advanced 和6G 业务需求和性能要求的大幅提升,massive MIMO 将向超大规模MIMO和超大孔径阵列(extremely large aperture array, ELAA)演进,需要支持更多的天线数和更复杂的算法,而基带算法复杂度一般随着天线数的平方至立方增长,因此基带计算能耗会成为持续提升网络能效的主要挑战之一[2-3]。

现有支持massive MIMO 技术的底层硬件架构方案主要有两种,即专用计算架构和通用计算架构。专用计算架构以ASIC 芯片为主,通过面向5G 的定制化芯片持续提升性能和能效,是当前业界的主流方案。通用计算以CPU 通用处理器为主,可利用FPGA 或GPU 进行基带硬件加速,是Open RAN 的技术主张之一。当前专用计算架构的能效优于通用计算架构,通用计算在性能和能效上仍然有较大的挑战[4],但业界对未来不同基站架构的能效优劣和发展趋势仍存在争议:一种观点认为随着技术发展,未来两者的能效比差距会缩小甚至反转,另一种观点认为两者的能效比差距不变甚至拉大。随着基站计算复杂度的增加,不同计算架构对碳排放的影响将成为未来基站架构选择的关键因素,因此针对不同基站计算架构的能效比差值趋势做量化研究非常有必要。

当前已有文献研究某个5G 空口算法在不同计算架构下的性能和能效,如文献[5] 提出了一种基于ASIC 的专用FFT 算法,证明基于ASIC 实现FFT 相对通用CPU 有超过180 倍的能效提升。文献[6] 从功能可重构角度,提出基于FPGA 硬件加速实现massive MIMO 功能,但是没有给出量化能效分析。文献[7] 利用FPGA 的多千兆收发器(multi gigabit transceivers, MGTs)来实现C-RAN 集中信号处理,但只评估了FPGA 硬件吞吐能力,没有分析如何将硬件能力转化为无线空口性能或能效的收益。综上,现有文献主要分析单点5G 空口算法的计算性能,虽然能够定性体现出专用计算在能效上的优势,但由于缺少对基站基带全系统的计算需求和能效的量化建模,从现有文献的研究结果并不能得到不同计算架构的整体系统能效差异和演进趋势。

基于通信基站碳排放最小化的目标,本文通过计算需求建模、计算架构能效建模和量化功耗分析的研究方法,给出了不同基站计算架构的能效对比,并对基站计算能效的发展趋势进行量化研究。

1 Massive MIMO 计算需求建模

1.1 Massive MIMO 基带功能划分

本文以典型5G 三扇区站点为例,包含1 个BBU 和3 个AAU 天线,5G 典型的AAU 天线为64 TRX,小区带宽为100 MHz。

从系统层面上典型的5G 收发器由以下组件组成:L1/L2/L3 数字信号处理、数字中频前端、模拟RF 前端和天线。5G 需要的基带处理技术非常复杂,基带运算有如下特征:1)计算密集型,massive MIMO 天线所涉及的矩阵运算复杂度与天线数呈2~3 次方关系;2)功能单一,基站工作在网络协议的底层,对所有的数据都按固定流程处理,只执行特定功能。

按3GPP 协议定义,数据信道负责用户数据传输,并且占用了绝大多数的时频资源,在基带芯片中的大部分计算为数据信道服务。数据信道分为下行数据信道PDSCH 和上行数据信道PUSCH,按协议定义,下行数据信道主要划分为LDPC 编码、层映射、多天线权值映射、IFFT 模块,上行数据信道主要划分为FFT、信道估计与测量、权值计算、MIMO 均衡、LDPC 译码模块。在整个基带处理部分,LDPC 译码、MIMO 均衡、权值计算和下行加权占用了整个芯片资源的80%以上,本文以这几项关键算法来代表整个基站数字信号处理,用以分析基站数字信号处理部分的功耗。

1.2 关键算法复杂度建模

LDPC 译码:在NR 协议中采用LDPC 码作为上下行数据信道的编码方式,文献[8] 给出了LDPC译码复杂度,对数域译码只需要加法和比较,其加法次数为:

比较次数为:

考虑到加法器和比较器复杂度相近,这里统一为加法,则需加法器次数为:

式中,dv,1为校验矩阵除了列重为1 列的平均列重;dc为校验矩阵的平均行重;M为矩阵行数;N1为矩阵行数。

NR 协议的最小时域调度粒度为Slot,即一次调度数据需要占据同一个Slot 的所有数据信道资源。由于协议的LDPC 最大码长限制,1 个Slot 的传输数据可能不只1 个LDPC 编码块,需要有NCB个LDPC 编码块。同时,考虑到LDPC 译码需要多次迭代才能有较好的性能,则1 s 内LDPC 译码所需要的加法次数为:

MIMO 均衡:MIMO 均衡的经典算法为最小均方误差(minimum mean square error, MMSE)均衡算法,其表达式如下:

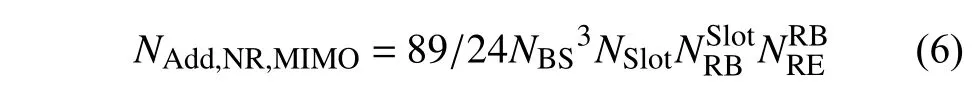

NR 的MIMO 均衡是在RE 粒度进行的,1 s内MIMO 计算复杂度需要在单次MIMO 均衡的基础上乘上1 s 内上行数据信道和控制信道的RE个数。同时考虑上行多用户MIMO,虽然上行同时复用的流数最大为NBS,但考虑连续组网对抗干扰,商用网络中的典型上行流数不会大于NBS/2,即NUE取 值为NBS/2。则NR MIMO 加法器次数可以表示为:

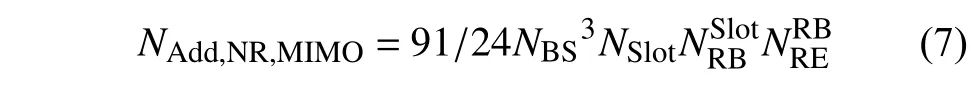

NR 乘法器次数可以表示为:

式中,NSlot为 1 秒内Slot 个数;为1 个Slot 内的RB 个数;为一个RB 上的RE 个数。

SU 权值计算:对于时分双工(time division duplexing, TDD)系统,下行信道信息利用信道的上下行互易性在基站侧获取,上行信道通过上行探测参考信号(sounding reference signal, SRS)获取。

对单用户权值,奇异值分解(singular value decomposition, SVD) 是有效的权值方案,可将 MIMO信道转化为无干扰的并行信道,以获取MIMO 信道的复用收益[11]。信道H可SVD 分解为:

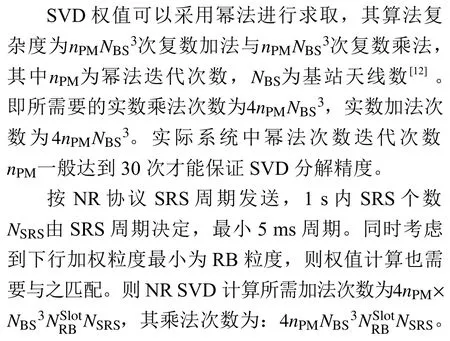

式中,酉矩阵V中的前RANK 个向量即为SVD权值。

对于MU(multi-user)-MIMO,迫零(Zero-forcing,ZF)权值是一种有效的下行多用户权值[13]:

借助SVD 可以将MU 权值计算简化,由下式可以将W的计算简化为:

即MU 权值计算可以先由SVD 得到U、S、V,再由矩阵乘法得到W。考虑S−1为实数对角阵,求取W所需SVD 计算的复杂度与SU 相同,所需矩阵乘法算法复杂度为次复数乘法、(NBS−1)次 复数加法和次实数乘法。因此,所需要的实数乘法次数为+次实数乘法,−次实数加法。

由于NR 每个Slot 都可以调度不同用户,因此每个Slot 都需要计算MU 权值,同样考虑DRS 粒度,MU 权值粒度同样最小为RB 级。则NR MU计算所需加法次数(忽略低阶项)为4(nPM+1)×,其乘法次数为4 (nPM+1)。

结合SU 和MU 计算,权值计算所需要加法次数为:

乘法次数为:

下行加权计算:下行数据发射之前需要根据权值将数据流映射到天线,加权后数据x为:

式中,W为计算后权值;s为原始数据向量。

忽略低阶项,则NR MIMO 加法器次数可以表示为:

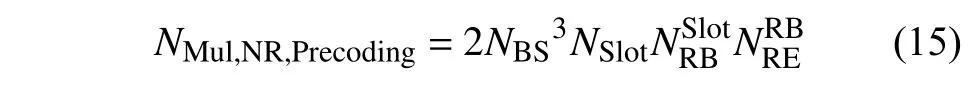

NR 乘法器次数可以表示为:

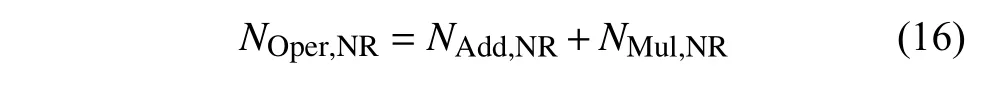

考虑到LDPC 译码、MIMO 均衡、权值计算、下行加权占据了大部分基带算力,这里用这4 项之和代表整个NR 的基带算力需求,1 s 内的总操作数NOper,NR为:

式中,NR 1 s 内总加法次数为:

1 s 内总乘法次数为:

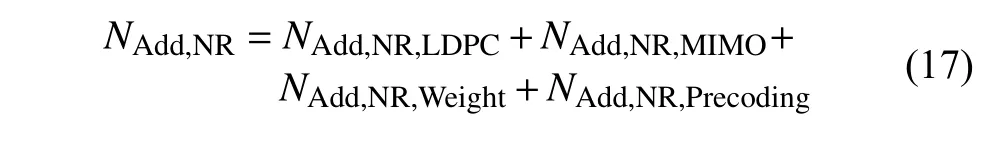

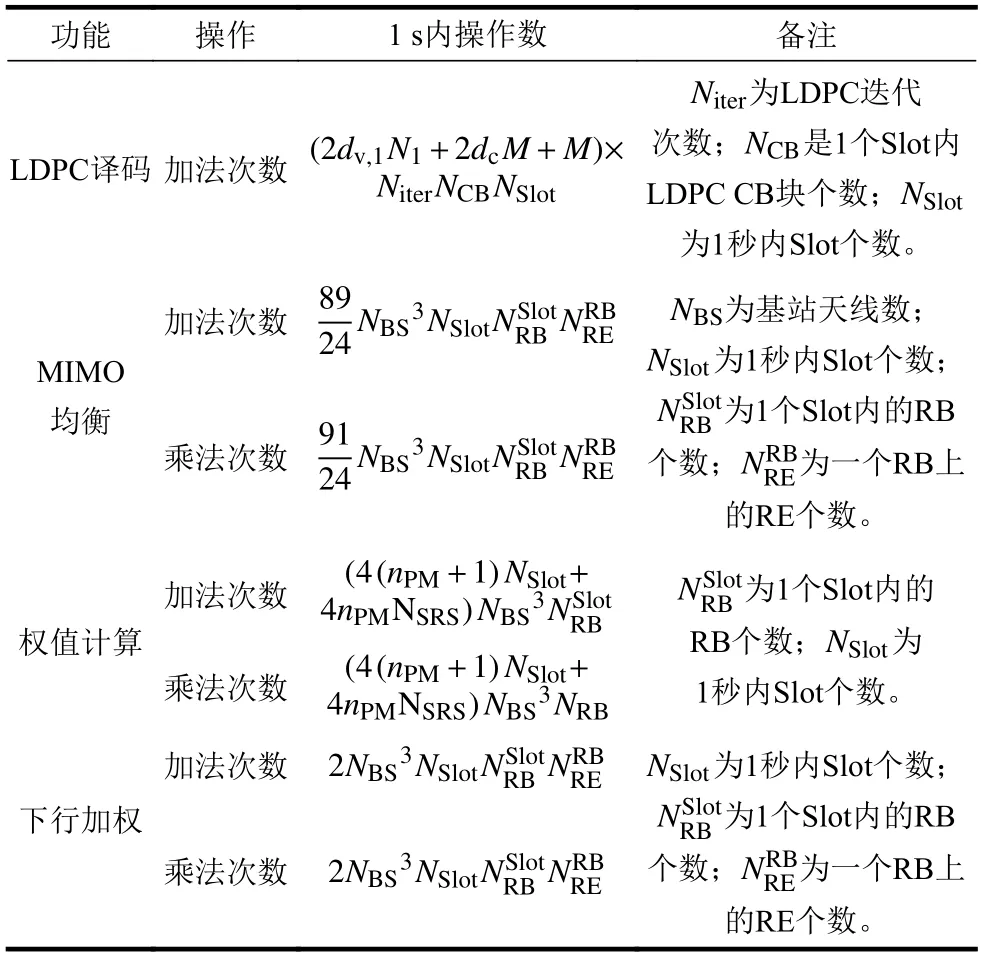

汇总LDPC 译码、MIMO 均衡、权值计算和下行加权计算计算复杂度,如表1 所示。

表1 计算复杂度对比

2 基站计算架构的能效建模

2.1 基站计算架构

基站计算架构可以分为两种,以ASIC 为主的专用计算和以通用处理器CPU 为主的通用计算,当前主流方案是以ASIC 为主的专用计算。Open RAN 宣称采用通用计算技术,如乐天移动的Open RAN 建网方案中,BBU 硬件基于“Intel X86 服务器+FPGA 加速卡”。

在通用计算芯片领域,CPU、GPU、FPGA 是3 大主流技术。其中,CPU 适用于处理逻辑复杂、重复性低的串行任务,如基站L3 和核心网算法。GPU 适合通用并行处理,适合大规模数据的并行加速处理。FPGA 具备可重构特性,在无线通信的L1 基带信号处理加速和数字中频信号处理中有一定应用。

不同计算架构的计算方案各不相同,其能效评估方法也存在差异。本节针对ASIC 专用计算、CPU 通用计算、以及CPU+FPGA 加速的通用计算分别进行分析,建立能效评估模型。本文对不同架构选取当前主流工艺进行对比,ASIC 选择7 nm FinFET 工 艺,CPU 选 择Intel 10 nm 工艺,FPGA选择Xilinx UltraScale+ 系列16 nm 工艺。

每秒浮点运算数(FLOPS)用于限定计算系统的性能,功率用于测量单位时间内消耗的电能。因此,能效可以通过性能和功率之间的比率来定义,即FLOPs/Watt,能效比ρ 定义为:

式中,CPeak为1 s 内可运行的操作数;P为1 s 内的能耗,即功率。

2.2 专用计算能效评估模型

由于ASIC 的定制化特点,完成一个具体功能的硬件功耗与设计强相关。考虑到本文旨在获取一个较为通用的评估模型,选取当前7 nm FinFET 工艺ASIC 的典型功耗作为参考,其16 bit 加法器和乘法器的典型功耗分别为0.650 FJ 和4.018 FJ[14]。为了保证计算精度,基带计算单元中求逆、SVD等一般采用32 bit 进行计算。相比16 bit 计算,32 bit加法器复杂度为2 倍,乘法器复杂度为4 倍[9]。另外,考虑在基带ASIC 里面除了负责计算的组合逻辑单元外,还有存储、接口等单元,组合逻辑的占比在20%~50%[14-16]。取20%占比评估,则单个加法/乘法操作对应的整个芯片的消耗分别为6.5 fJ 和80.36 fJ,对应能效比为ρAdd,ASIC=154 TFLOPs/Watt,ρMul,ASIC=12.4 TFLOPs/Watt。

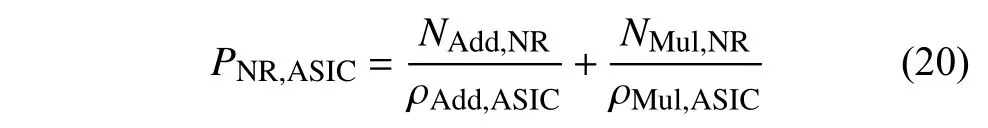

采用ASIC 架构来实现NR 基带,所需功耗(1 s内能耗)为:

代入式(17)、(18)并省略低阶项,可以进一步表示为:

2.3 通用计算能效评估模型

CPU 的能效由功耗和峰值计算能力来评估,CPU 能效比为:

式中,PCPU为 CPU 功耗;CPeak,CPU为CPU 的1 s内峰值算力。

CPU 理论峰值算力可以表示为:

式中,NCPU_Core表示CPU 的核数;fCPU代表CPU单核的主频;NFlops_Cycle表示CPU 在每个周期的浮点计算次数。

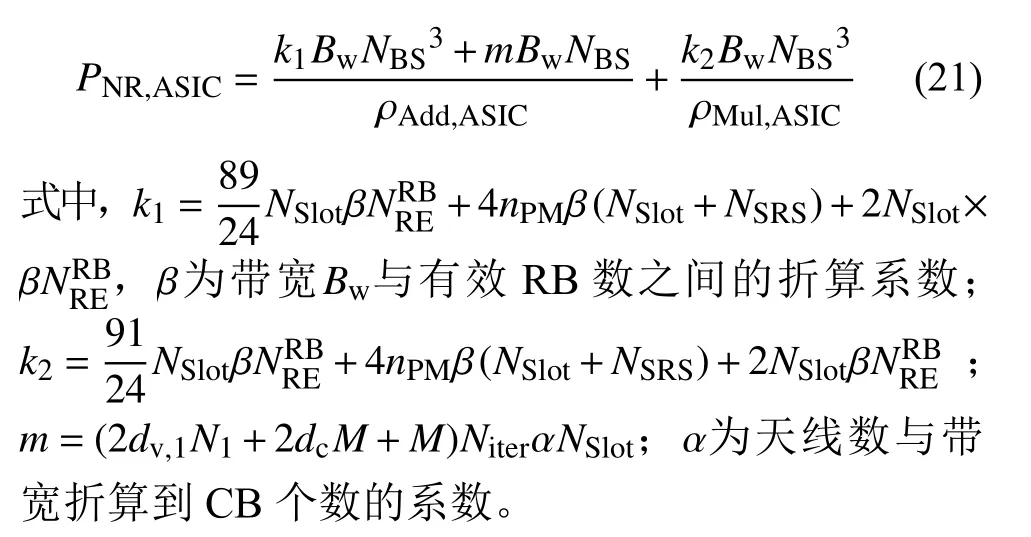

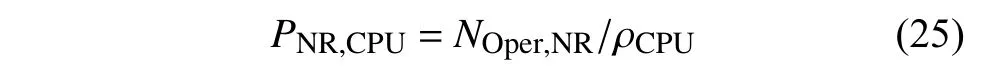

而CPU 单周期单精度浮点计算能力NFlops_Cycle可以表示为:

式中,NFMA代表每个CPU 核中的乘加计算单元(fused multiply-add, FMA)个 数;NBits代 表FMA处理比特数;NWidth代表操作系统位宽。以最新intel 用于服务器的CPU Intel® Xeon® W-11865MLE为例[17],采用10 nm 工艺,基本参数为8 核,单核最大频率为4.5 GHz,功耗为25 W,支持最新的AVX512 指令集,共有2 个FMA。可得对于32位操作系统NFlops_Cycle为64 FLOPs,则Xeon W-11865MLE 对应的理论峰值算力为2304 GFLOPs,对应能效比为ρCPU=92.2 GFLOPs/Watt。

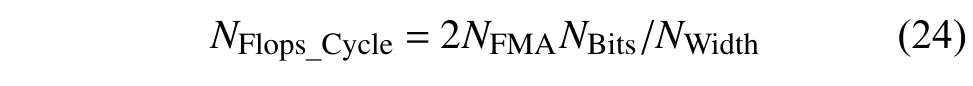

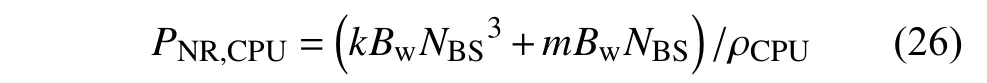

采用CPU 来实现NR 基带,所需功耗(1 s 内能耗)为:

同样代入式(17)、(18)并省略低阶项,可以进一步表示为:

式中,k=k1+k2。

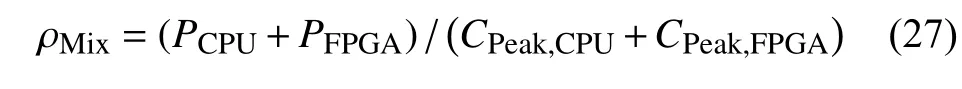

对于混合架构的单次操作功耗可以表示为:

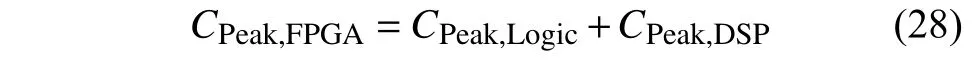

式中,CPeak,FPGA为FPGA 的峰值计算能力。FPGA的算力分为两部分,一部分是逻辑单元的算力CPeak,Logic, 一部分是内置DSP 的算力CPeak,DSP,即:

由于FPGA 门与ASIC 门存在一定转化关系,一个FPGA 门等价为β 个ASIC 门,对于Xilinx 而言,一个逻辑单元对应15 个ASIC 门,则逻辑单元的峰值算力可以表示为:

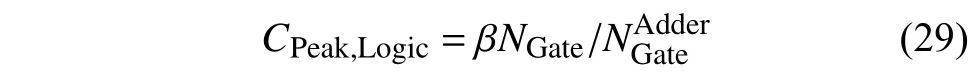

而DSP 的峰值算力为:

式中,NFlops_Cycle,DSP为一个时钟的操作数,由于DSP 核一个时钟周期可以进行一次加法和一次乘法,NFlops_Cycle,DSP取值为2。

FPGA+CPU 架构选取Xilinx 最新的UltraScale+系列FPGA 和CPU Intel® Xeon® W-11865MLE 组合。UltraScale+系列FPGA 能效比为7 系列的2.4 倍,Xilinx 的V7-690T 包含了3600 个DSP 核和693120个逻辑单元,主频为250 MHz,功耗为30 W。根据式(28)~(30)可得1 s 内峰值算力为18 TFLOPs,相同能耗下UltraScale+系列峰值算力为18 TFLOPs×2.4 = 43.2 TFLOPs。则UltraScale+ FPGA 与W-11865MLE 组合架构的能效比为ρMix=854 GFLOPs/Watt。FPGA 与CPU 混合架构在1 s 内的功率消耗为:

同样代入式(17)、(18)并省略低阶项,可以进一步表示为:

3 结果和讨论

3.1 不同计算架构的能效对比

对基于64TRX 的massive MIMO 基站进行分析,设带宽为100 MHz、调制阶数为256QAM、码率为0.926、采用30 kHz 子载波间隔,1 s 内有2000个Slot,每个Slot 有14 个OFDM 符号,每个OFDM符号有效子载波为3276 个,SRS 周期为5 ms,考虑小区间干扰上下行最大流数为收发天线数的一半。下面将基于上述参数和上一章的计算复杂度模型给出具体的基带计算复杂度。

根据上述参数可以计算出一个Slot 最大的上行 物 理 共 享 信 道(physical uplink shared channel,PUSCH)传输量为10860596bit,则最大可以有=1286个CB块。按式(4) 计算出LDPC需要的加法次数为1.75×1013次。

MIMO 均衡为RE 粒度的,基于式(6)、(7)可以计算出MIMO 均衡需要的加法次数为8.92×1013次,乘法次数为9.12×1013次。

权值计算的计算次数由RB 数、SRS 周期等决定,根据式(11)、(12)计算得出权值计算所需要的加法次数和乘法次数皆为1.95×1013次。

下行加权是RE 级的,按式(14)、(15)可以得出所需加法次数和乘法次数皆为4.81×1013次。

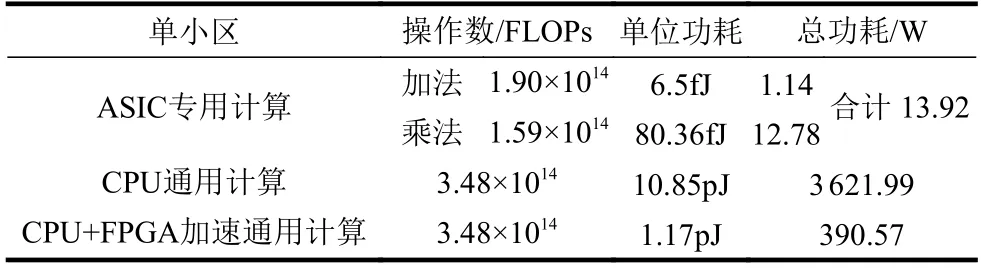

按本文分析,7 nm ASIC 单个加法/乘法操作对应的整个芯片的消耗为6.5/80.36 fJ。Intel 10 nm CPU 单次操作的功耗为10.85 pJ,UltraScale+ FPGA与W-11865MLE 组合架构的单次操作对应功耗为1.17 pJ。则根据本文分析的基带计算复杂度,可以得出3 种架构的不同功耗,如表2 所示。

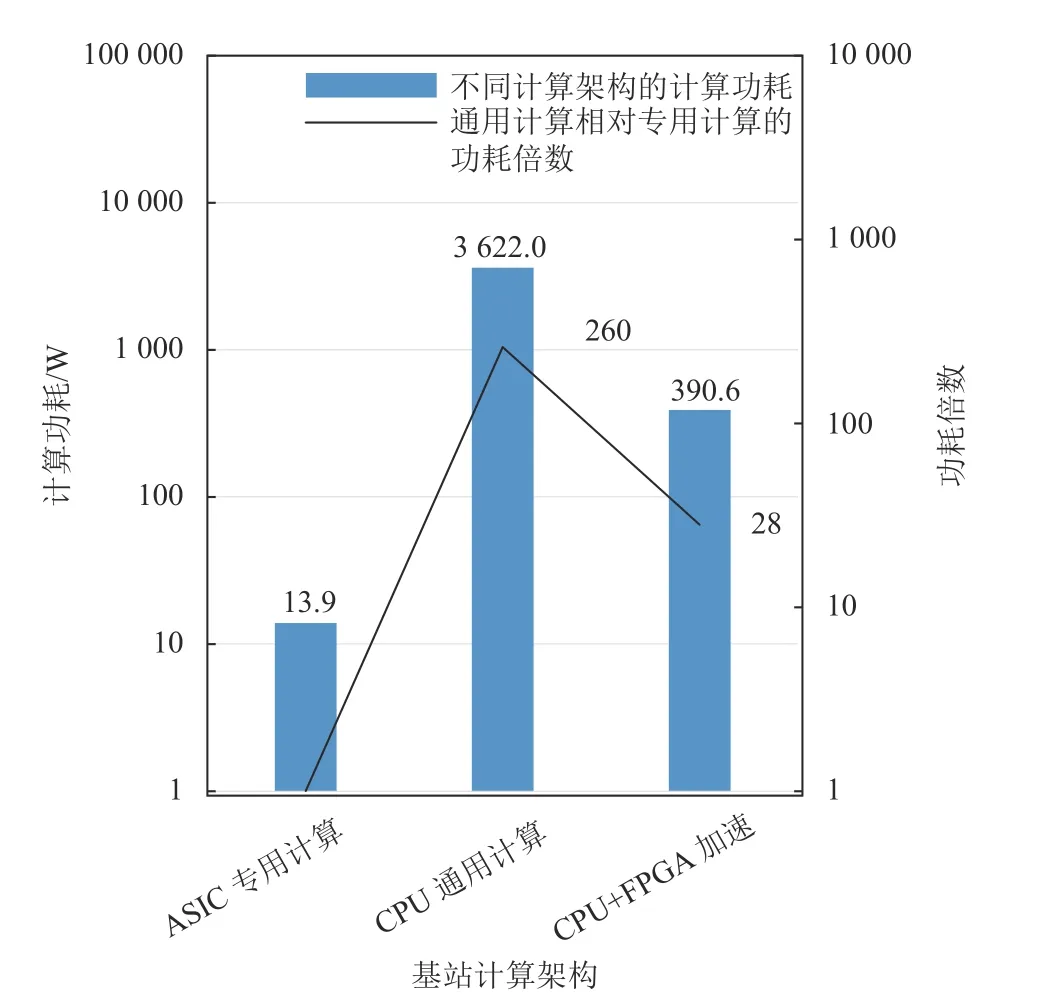

根据表2 给出的不同架构的功耗,可以计算得出不同计算架构的功耗对比系数,如图3 所示。

表2 5G massive MIMO 不同基带架构的功耗对比

从图1 可以看出,相比ASIC 专用计算,CPU 通用计算和CPU+FPGA 加速的基带整体功耗都有显著提高,其中CPU 计算功耗提高260 倍,CPU+FPGA加速架构功耗提高28 倍。因此,移动通信基站以确定性的计算为主,以ASIC 为主的专用计算在功耗上有明显优势。通过使用FPGA 或CPU 硬件加速,可以在一定程度上提升计算能效,但是相对ASIC 专用计算的能效仍然有较大差距。

图1 不同计算架构的基带整体功耗对比

上述分析只考虑基带计算芯片的能效对比,不包含周边电路和器件,因此计算芯片的能效差异大于整体BBU 的能效差异,但典型场景下计算芯片消耗大部分能耗,其占比通常超过50%,因此上述分析结果仅体现不同计算架构的计算能效差异。

基站是网络边缘节点,除了基站主设备的功耗,还包含很多站点配套设备,如电源、空调、监控等。站点配套设备的功耗跟基站主设备功耗强相关,如果基站主设备功耗增加,站点整体能耗将以相应的幅度增加。因此,如果BBU 直接采用通用处理器的COTS 服务器,成本、功耗、集成度都会与专用硬件BBU 有巨大差异,导致更多的站点配套和更多的能源消耗及碳排放。

3.2 不同计算架构能效差异的趋势分析

当前ASIC 专用计算相对通用计算有明显能效优势,业界已有共识,但对不同计算架构能效的未来变化趋势仍存在争议,本节将通过建模来分析不同计算架构的能效差异的变化趋势。

随着massive MIMO 的演进,包括ELAA、cell free massive MIMO 等,未来通信系统将走向更大的频谱带宽和更多的天线数,从而带来基带计算需求的增加。另外考虑芯片工艺的进步,计算能效比会持续提升。由于下一代移动通信协议的不确定,这里按NR 协议来分析带宽增加、天线数增加和能效比提升3 个因素对未来移动通信架构功耗的影响。CPU 通用计算相对ASIC 专用计算的能耗差值Ptrend,CPU可以表示为:

CPU+FPGA 加速架构相对ASIC 专用计算的功耗差值Ptrend,Mix可以表示为:

式中,ln为未来芯片工艺进步带来的能效比提升,其取值分别为1.0 (64 TRX 100 MHz,对应2021 年)、2.8 (128 TRX 400 MHz,对应2025 年)和3.1 (256 TRX 800 MHz,对应2028 年)[18]。

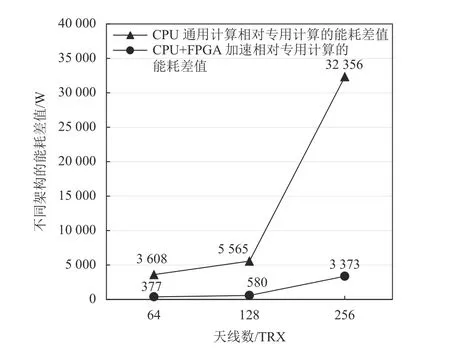

将小区带宽、基站天线数和能效比指标带入式(33)和式(34),可以分别得到不同massive MIMO天线数和不同小区带宽下通用计算相对专用计算的能耗差值。

如图2 所示,CPU 通用计算相对专用计算的基带整体功耗差值随着天线数增加而大幅增加(假设带宽保持100 MHz 不变),当天线数从64 TRX 提升到256 TRX 时,功耗差值从3608 W 增加到32356 W(接近9 倍)。CPU+FPGA 计算架构相对专用计算的基带整体功耗差值也随天线数增加而大幅增加,当天线数从64 TRX 提升到256 TRX 时,功耗差值从377 W 增加到3373 W(接近9 倍)。

图2 不同massive MIMO 天线数的基带整体能耗差值

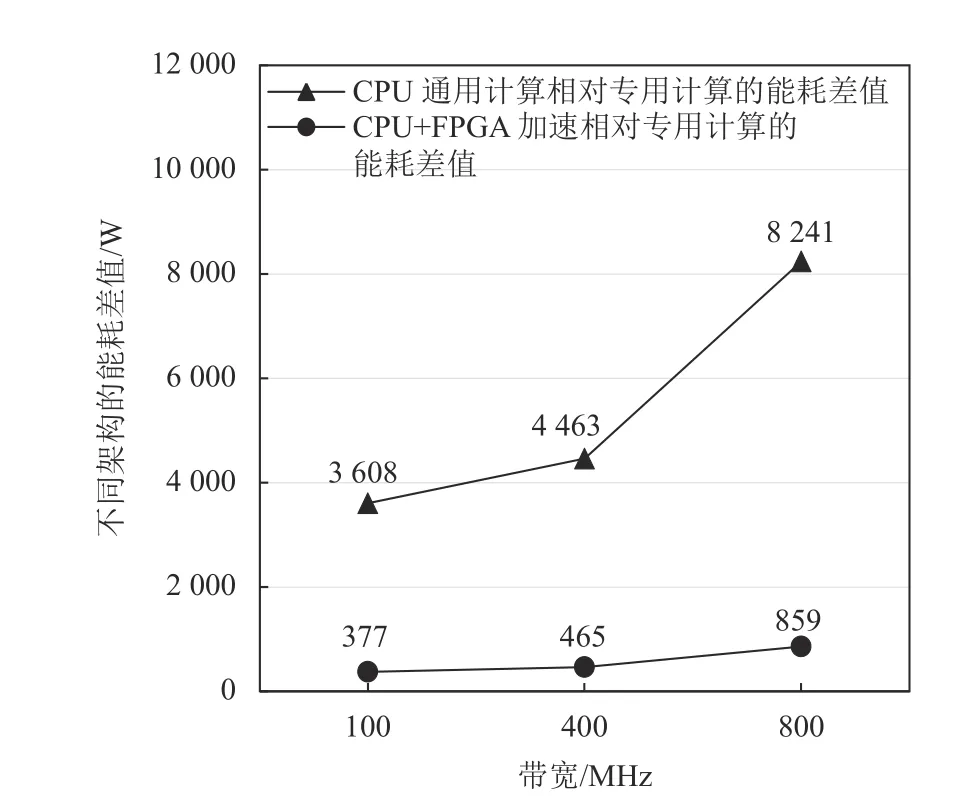

如图3 所示,CPU 通用计算相对专用计算的基带整体功耗差值随着带宽增加而明显增加(假设天线数保持64 TRX 不变),当带宽从100 MHz 提升到800 MHz 时,功耗差值从3608 W 增加到8241 W(大于2 倍)。CPU+FPGA 计算架构相对专用计算的基带整体功耗差值也随带宽增加而明显增加,当带宽从100 MHz 提升到800 MHz 时,功耗差值从377 W 增加到859 W(大于2 倍)。

图3 不同小区带宽的基带整体能耗差值

上述模型中,假设了通用计算和专用计算随未来芯片工艺进步带来相同的能效比提升,采用了相同的ln取值。如果考虑到专用计算架构可以充分发挥异构计算优势,通过专门的芯片设计进行优化,获得相对通用计算更大的能效比提升,将导致专用计算相对通用计算的优势会比本文结果更明显。

4 结 束 语

不同计算架构有各自适用的场景,针对计算需求相对确定的计算密集型应用场景采用专用ASIC芯片提升能效比,已经在深度神经网络、区块链等很多行业的实践中得到证明。

本文通过对massive MIMO 基站计算需求建模,同时对不同计算架构的能效建模,给出了定量的分析结果。结果表明当前专用计算相对通用计算(有硬件加速)具有接近30 倍的能效优势,而相对纯CPU 通用计算架构有200 倍以上的能效优势。随着未来基站天线数和小区带宽的增加,通用计算相对专用计算的功耗差值会进一步增加,两者的差距将越来越大,而不是越来越小。即使采用FPGA 对通用计算做加速,相对专用计算的差距依然是越来越大。

因此,无论现在还是未来,massive MIMO 基站采用通用计算相对专用计算,都不利于节能减排目标。Open RAN 主张的基站软硬件解耦、通用计算取代专用计算,也不利于移动通信行业绿色低碳发展。从移动通信行业降低碳排放角度,更应该加大基站专用计算技术的投入。