多通道14 位125MSPS 流水线型ADC 设计∗

龙善丽贺克军童紫平张紫乾徐福彬唐兴刚

(华东光电集成器件研究所,江苏 苏州 215163)

流水线型数模转换器(Analog to Digital Converter,ADC)因其优越的特性而广泛地应用于数字阵列雷达、无线通讯、高清视频设备等领域。近年来,各种数字信号系统对数模转换器的速度、精度和功耗等方面的要求也不断提高[1-4]。不同的电子系统对数模转换器的要求也不一样,比如对于分辨率为10 位以下速率不高的场合,大多采用逐次逼近寄存 器(Sucessive Approximution Register,SAR) 型ADC,对于分辨率要求大于20 bit 的场合常采用Sigma-delta 型ADC,对于采样速率大于2 MHz 以上的高速高精度场合,大都采用折叠插值、流水线(Pipeline)ADC 和全并行(Flash)ADC[1-3]等。流水线型ADC 的量化过程使得噪声、线性度、速度之间有个比较好的折中,在进行具体电路方案设计时可以有不同的选择,这也使得流水线型成为众多高速ADC 的主要实现架构。雷达按用途分类,有预警雷达、搜索警戒雷达、引导指挥雷达、炮瞄雷达、测高雷达、战场监视雷达、机载雷达、无线电测高雷达、引信雷达、气象雷达、航行管制雷达、导航雷达以及防撞和汽车电子雷达等。随着雷达技术的发展,雷达系统多输入/多输出收发技术发展迅速,多通道数字收发系统设计过程中,对发射通道和接收通道的性能设计具有非常严格的要求,其中多通道高速模数转换器(ADC)就是其中最关键的核心器件之一。

本文采用国内SMIC 0.18 μm 1P6M Mixed-signal CMOS 工艺,设计了一款四通道、分辨率为14 bit,采样率为125 MHz 的流水线型A/D 转换器,通过两片叠封的方式组成了八通道模数转换器。单通道流水线型ADC 通过分析设计选取了多位量化架构,合理实现关键电路模块,并对具体电路的设计进行优化,得到了业界较好的测试结果。文章第1 节主要介绍了八通道模数转换器的系统实现架构;第2 节介绍了采样保持电路的设计与实现;第3 节介绍了整体电路的版图设计;第4 节给出了整体电路测试结果。

1 系统架构

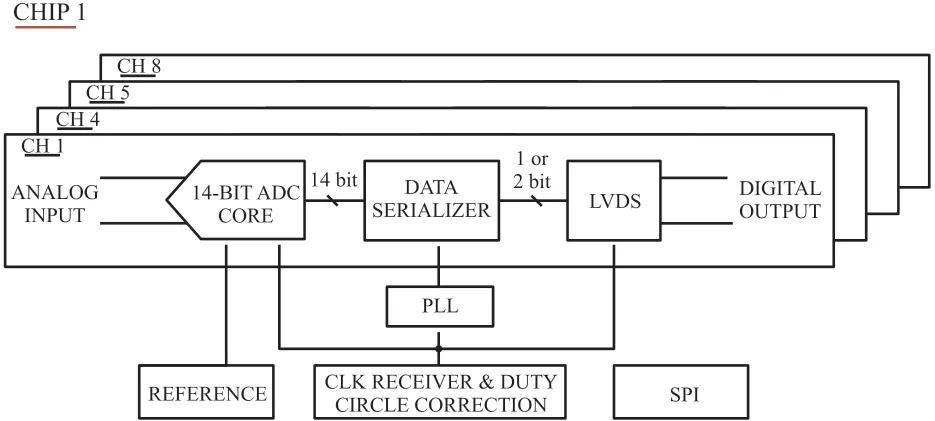

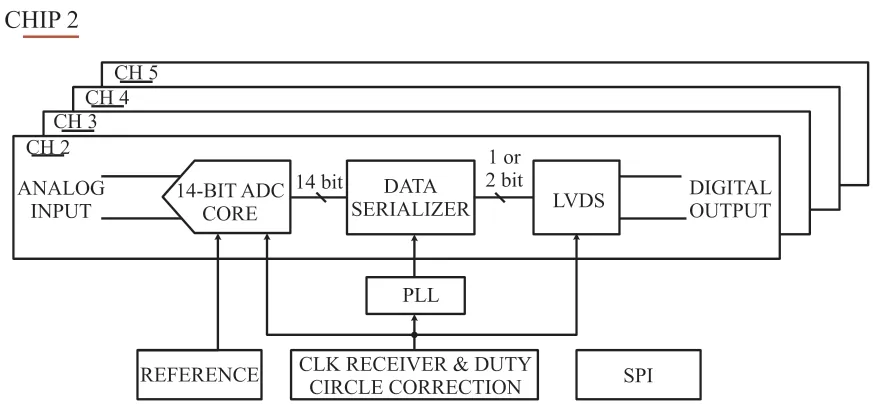

本产品由两个14 bit 125 M 四通道裸芯片采用SIP 叠层封装形式封装在一起构成8 通道14 bit 125 M ADC。芯片1 和芯片2 的结构框图如图1 和图2 所示。每个芯片包含4 个14 位125 M ADC 通道、参考模块、时钟接收和占空比稳定器模块、PLL模块和SPI 模块。

图1 芯片1 结构框图

图2 芯片2 结构框图

芯片1 内是ADC 的1、4、5、8 通道,芯片2 内是ADC 的2、3、6、7 通道,一起组成了八通道模数转换器。

每个ADC 通道包括ADC 核、数据串行化模块和LVDS 模块,模拟输入首先经过ADC 核量化为14 bit数据,经过串行模块后得到1 bit 或者2 bit 输出。串行输出通过LVDS 模块输出到ADC PIN 脚。

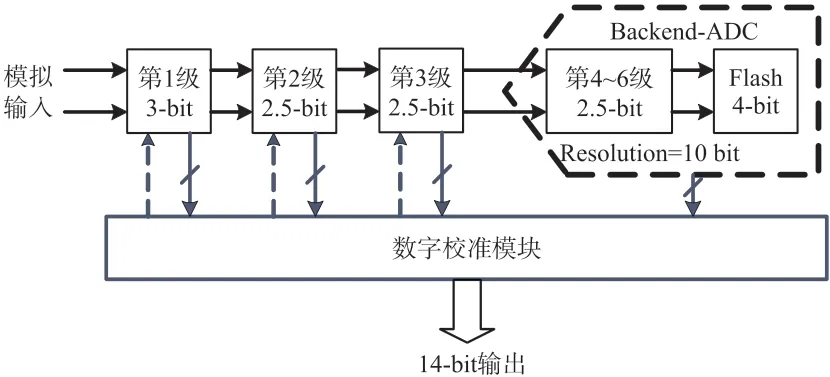

在实际研究中,流水级多采用1.5 bit 级联结构来实现,本文采用的流水线型ADC 的系统架构如图3 所示,共包括6 级流水级和一级Flash ADC。前三级流水级的分辨率是3 bit,后三级流水级的分辨率是2.5 bit,最后一级Flash ADC 的分辨率是4 bit。每级流水级分辨率均较高,可有效提高线性度,并对噪声进行衰减,有助于降低功耗。所有流水级的输出经过数字校准逻辑得到最终的14 bit 模数转换结果。数字校准电路还会对前三级流水级的电容失配误差以及有限增益误差进行校准,可以看到,数字校准电路有输出控制信号给前三级流水级。

图3 本文14 位模数转换器实现架构

2 采样保持电路设计

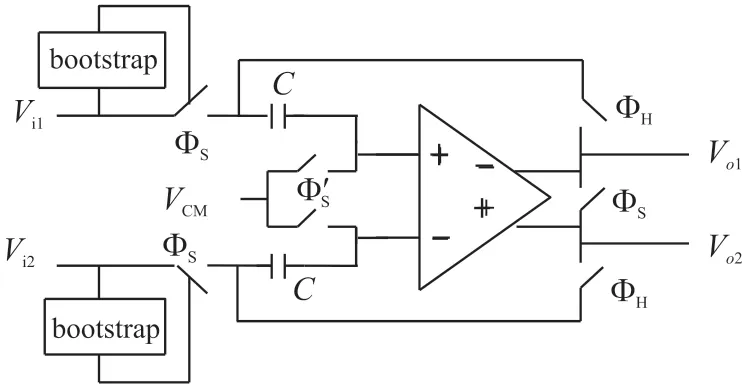

对于高速流水线ADC 来说,关键的模块为采样保持器(Sample/Hold,S/H)和流水线第一级,因为他们是噪声、速度和功耗的主要限制者[5-9]。通常的采样保持器如图4 所示。

图4 采样保持器

Vi1、Vi2分别为采样保持电路同相输入端和反相输入端,bootstrap 为输入电压跟随电路,它使得采样开关管VGS为常数,减少了MOS 管导通电阻与输入信号相关的非线性。时钟信号控制的开关为运算放大器提供输入共模电压VCM。当Φs和Φ′s为高电平时,采样开关NMOS 导通,输入信号被采样到电容C上,同时输出Φs对应的开关导通,使得Vo1和Vo2建立相等的共模输出电平。当ΦH为高电平时,ΦH对应的开关导通,电容C上电荷建立相应的输出信号。对应的开关较Φs对应的开关先关断,以克服开关断开时的沟道电荷注入。在实际电路设计中,ΦH对应的开关采用传输门,以减少开关导通电阻随着输入电压变化。

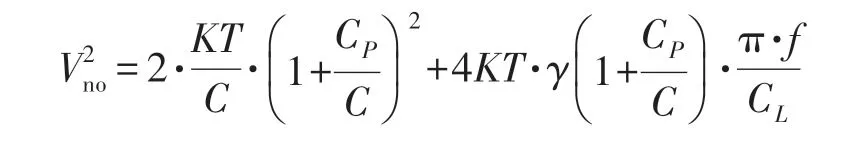

采样保持器的噪声由采样相位热噪声和保持相位运算放大器噪声组成。采样相位噪声为:2 K·T/C。保持相位运算放大器引起采样保持输出热噪声为:为运算放大器输入参考热噪声,Gn=(1+CP/C)为运算保持相位噪声增益,BWn为噪声带宽。对于全差分运算放大器,输入参考热噪声为:8K·T·γ/gm,这里gm为运算放大器输入MOS跨导,γ为MOS 管热噪声系数。对于单极点运算放大器,采样保持电路噪声带宽为:π·gm·f/2CL,其中CL为运算放大器负载电容,f为采样保持电路反馈系数,因此采样保持电路总的输出热噪声为:

式中:CL为采样保持电路的等效负载电容。

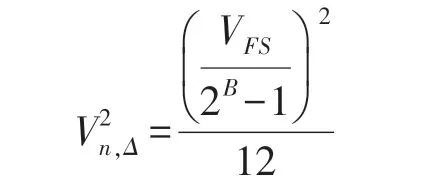

Pipelined ADC 每一级采用相同结构,采样保持电路的热噪声小于ADC 的量化噪声,一个Bbit(即以Bbit 量化精度为例)的ADC 它的量化噪声为:

式中:VFS为满量程电压。

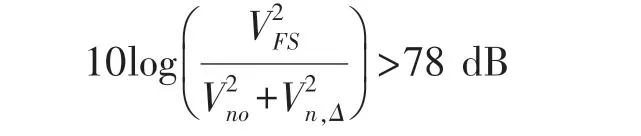

根据信噪比设计值的要求,有:

根据上式可以得出输入采样电容的大小。

后级流水级在第一级的基础上进行了逐级缩减,在不影响性能的条件下尽量降低电路功耗和版图面积。

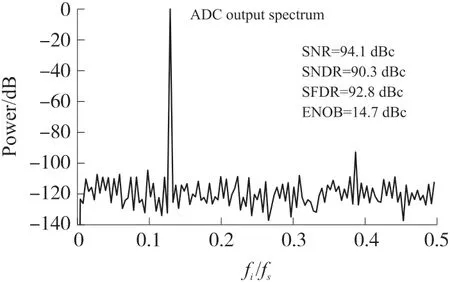

前端采保电路和所有流水级的整体联调仿真结果如图5 所示,由于仿真速度的限制,选取的仿真条件为:采样频率为125 MHz,输入信号频率为16 MHz,输入峰峰值为1 980 mV,典型工艺角下,ENOB 为14.7 bit,无杂散动态范围(SFDR)为92.8 dB,最差工艺角-电压-温度(PVT)组合性能ENOB 13.8 bit,SFDR 为88 dB,在电路设计阶段留有一定的设计余量。

图5 采保和流水级联调仿真结果

3 版图设计

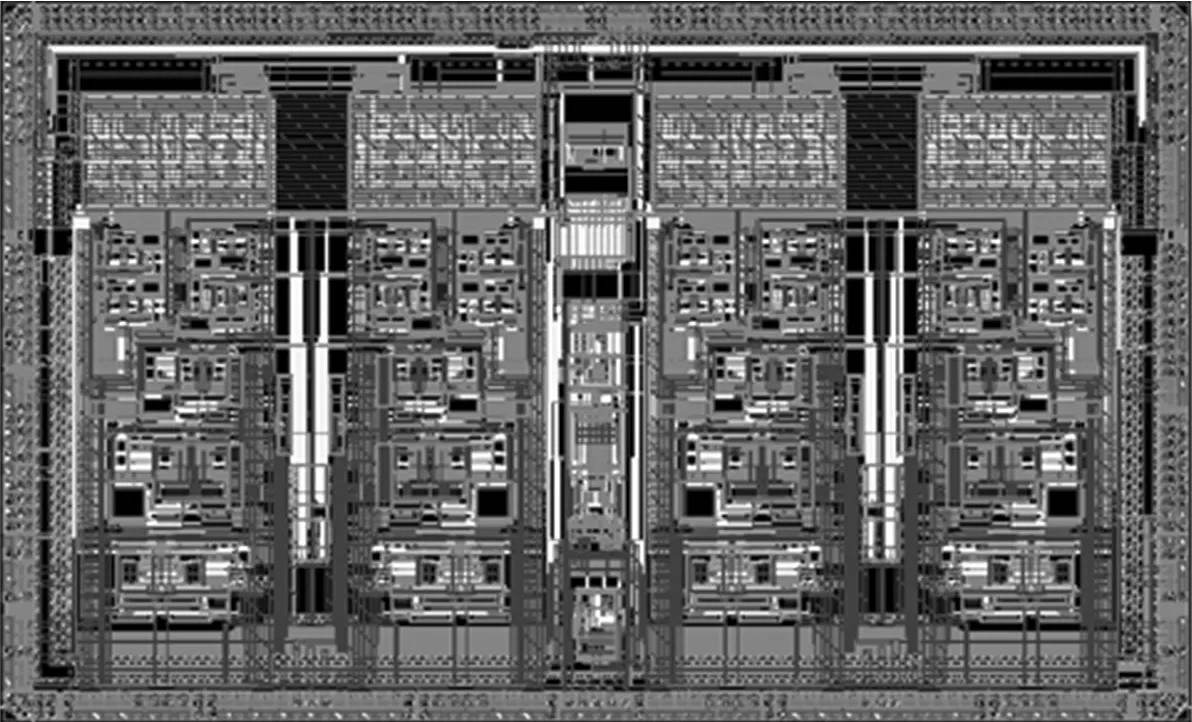

如图6 所示为四通道流水线型ADC 的版图,该版图采用SMIC 0.18 μm 1P6M Mixed-signal CMOS工艺实现。

图6 模数转换器电路版图

对于这种高速高精度模数转换器,工艺制作过程中和封装过程中产生的误差和环境噪声等对电路性能是巨大的误差源。为了克服实际版图中的器件失配和信号干扰,在进行版图布局设计中,首先要考虑各功能模块放置的位置,其次在版图设计中要重点关注对管的匹配设计和各敏感信号之间的抗干扰设计。对于前级需要对输入信号进行精确放大的级电路中,寄生电容和电阻对电路性能的影响非常大,所以关键节点的优化是非常有必要的。在采样放大通路中,采样电容和反馈电容的两端为关键节点。这些点的寄生电容将影响流水级电路的闭环增益,造成余差增益误差。在多通道高速电路中,各种电源线之间、电源和地之间的屏蔽和抗干扰设计显得尤为重要,在具体实现中,需要对各类电源进行隔离处理,对于需要有大电流经过的地方,尽量加粗地线和电源线。同时对于高信噪比ADC 来说,金属层电容的失配决定了ADC 的动态和静态性能。进行运算放大器版图设计时,全差分的两部分对称布版,晶体管交叉匹配;电容的版图采用中心对称形式。

版图的抗干扰设计主要是使模拟信号远离噪声源;数字电源和模拟电源分离;模拟电路模块和数字电路模块分开布版;敏感模拟信号两边采用地线屏蔽干扰。

4 测试结果

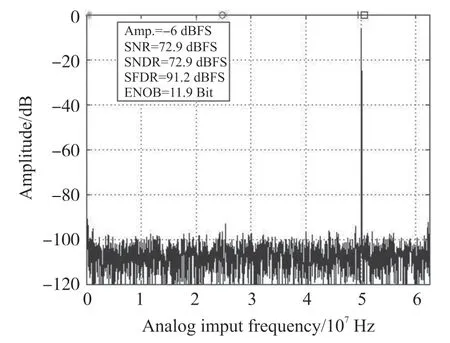

对流片电路进行了封装和测试验证,搭建了测试台进行性能评估。静态参数的码密度直方图测试法和动态参数的快速傅里叶变换(Fast Fourier Transform,FFT)测试法可以使用同一套测试系统,该方法也有利于测试方案设计、简化测试流程以及减少测试成本。动态特性测试频谱图如图7 和图8所示。图7 的测试条件是输入信号频率为70 MHz,信号幅度为-1 dBFS(即相对满摆幅下的信号功率)的正弦信号,采样频率为125 MHz,结果显示无杂散动态范围为87.4 dB,信噪比为74.3 dB,有效位数约为12 bit。图8 为输入信号为300 MHz,信号幅度为-6 dBFS 的正弦信号,采样频率为125 MHz 时的测试结果,通过结果显示无杂散动态范围为91.2 dB,信噪比为72.9 dB,有效位数约为11.8 bit。

图7 输入信号70 MHz 时动态特性测试频谱图

图8 输入信号300 MHz 时动态特性测试频谱图

5 结论

本文设计了一款可以用于高速高精度通信采集用途的多通道高速高精度模数转换器。其内核采用国内SMIC 1.8 V 0.18 μm 1P6M CMOS 工艺条件实现,是一款分辨率为14 bit,采样率为125 Msample/s流水线型模数转换器。系统架构采用6 级流水线和3 bit Flash 架构构成,其中采样保持电路使用电容翻转式结构。通过采用增益提高技术的折叠式共源共栅放大器、优化采样电容和运算放大器指标从而使电路满足低电压下高速高精度模数转换器设计的要求。流片测试结果表明,该款电路SNR 为74.3 dB,SFDR 为87.4 dB,有效位为12 bit,可以满足汽车雷达等多种系统的通信应用需求,应用前景广泛。