一种基于TMS320F28377D型微控制单元的低成本控制器软件方案设计

付建国,李 益,李 程,周 斌

(中车株洲电力机车研究所有限公司,湖南 株洲 412001)

0 引言

工业实时控制器作为工业设备的大脑,承担着设备实时控制、系统IO、对外通信等功能。随着当前工业设备市场竞争日趋白热化,对控制器功能多样性及成本管控提出了越来越大的挑战。

为实现设备在功能密度提升的同时满足成本下降的需求,本文提出并设计了一种基于TMS320F28377D型微控制单元(microcontroller unit,MCU)的控制系统的平台架构。TMS320F28377D(简称“F28377D”)为TI公司生产的单MCU双核芯片,其中一个内核完成传感器信号采集、PWM脉冲生成、故障快速保护与电机算法控制等任务,另一个内核实现逻辑程序控制、故障数据记录、程序远程加载、波形监视等功能。这种基于F28377D的单芯片平台架构不仅满足了工业实时控制器的功能需求,而且极大地简化了系统的数据流并降低了产品成本,同时也减轻了平台的维护压力[1]。

1 系统平台架构设计

本控制器采用单芯片F28377D架构,其硬件关联关系如图1所示。F28377D采用I2C总线通信,实现对时钟芯片和温湿度芯片的访问;采用串行外设接口(serial peripheral interface,SPI)总线通信,实现对旋变解码芯片、NOR Flash芯片以及集成以太网芯片的访问,进而实现以太网通信功能;利用片内AD采样模块实现对电压、电流等信号的采集;利用片内PWM模块生成PWM脉冲,进而实现电机控制。

1.1 主控芯片简介

主控芯片采用F28377D,其是一款功能强大的32位浮点微控制器(MCU),专门针对高级闭环控制应用而设计。F28377D支持新型双核架构,显著提升了系统性能;双实时控制子系统基于TI的32位C28x浮点CPU,每个内核可提供200 MHz的信号处理能力。F28377D包含2个外部存储器接口(EMIF)、2个CAN模块、3个高速(最高50 MHz)SPI端口、4个串行通信接口、2个I2C接口、4个模数转换器(最多支持12路16位AD采样或者24路12位AD采样)、24路具有增强功能的脉宽调制器通道以及8个比较器子系统,可在未满足电流限制条件的情况下保护功率器件。

1.2 总体方案设计

基于F28377D的控制系统软件架构主要分为底层软件和应用软件,它们分别被存放在片内FLASH存储器的两个扇区。底层软件主要负责更新应用软件,应用软件主要实现实时控制功能。控制器上电时,首先运行底层软件并判断是否需要跳转到应用软件;应用软件运行后,根据需求可下发指令跳转回底层软件进行应用软件的更新。应用软件的架构如图2所示。其中,内核CPU1负责逻辑程序控制、故障记录并结合硬件TCP/IP协议栈芯片(W5500)实现以太网通信,进而实现参数分离、波形监视等功能。内核CPU2通过片上AD采样模块实现对电机控制侧和电网控制侧模拟信号以及模块温度信号的采集;同时利用采集到的模拟信号生成相应的PWM脉冲,实现电机算法控制;另外,根据故障反馈信号封锁PWM脉冲,实现故障保护。CPU1和CPU2通过内部共享RAM,实现双核之间的数据交互。

1.3 平台优势

在工业领域,成本是产品竞争的关键,针对这一特点,本文提出的低成本控制平台相较于传统平台有如下优势:

(1)在传统平台中,实时控制由DSP执行,逻辑控制由ARM处理器执行;本文所设计的平台则将实时控制及逻辑控制功能融合于单片MCU中,使得成本大幅降低[2]。

(2)在传统平台中,实时保护由FPGA完成;而本平台以F28377D作为专用MCU,在芯片内部集成了基于模拟量比较器的实时硬件保护电路,构建了实时保护体系。

(3)在传统平台中,用操作系统的文件服务记录故障文件;本平台建立了一套全新的文件管理机制,在无操作系统情况下可以实现文件管理。

(4)在传统平台中,用操作系统的内存服务管理波形监视数据;本平台提出了一种高效内存管理方法,可提升内存利用率,实现数据的高效管理。

(5)传统平台设计需要操作系统工程师、实时控制软件工程师、底层驱动开发工程师3人全部参与;而本平台实现所有功能一体化,只需底层驱动开发工程师1人参与即可,实现了资源集约型平台开发。

本平台在成本大幅降低的同时,完全保留了既有“CPU+FPGA”架构平台的所有功能特征,性价比高,优势明显,满足低成本实时控制系统需求。

2 功能单元设计

本节重点介绍该控制平台软件架构重要功能的实现方法,主要包含系统同步采样、以太网通信、波形监视、故障记录以及程序远程加载等。

2.1 系统同步采样

工业实时控制器是一个高实时性的数字控制系统,在实际的控制过程中,采样位置和控制输出的精确性直接影响着控制系统的控制精度和系统的响应速度,最终影响算法的控制效果。

在当前常见的“DSP+FPGA”架构控制器中,DSP的主循环控制在DSP芯片时钟驱动下周期性运行,而数据采样则在可编程器件的内部时钟驱动下按照固定周期完成数据采样,两者属于异步时钟系统。采样数据在传递给DSP的过程中引入了由于异步时钟关系引起的抖动偏移,造成DSP接收数据采样时刻的不确定性,从而影响控制响应过程。在这样的异步架构下,DSP的控制结果输出也同样存在这样的问题,其引入的数据抖动对系统的快速响应和收敛会造成一定影响。

为保证传感器采样与控制算法间的固定相位关系,本方案基于F28377D内部集成的ADC电路,构建了一套同步采样方案,即在载波过零点t0时刻和周期值点t1时刻两个时刻同时触发AD采样并且产生中断运行控制算法,t2时刻和t3时刻分别为AD采样完成时刻,且(t2-t0)等于(t3-t1)。该方案可以保证采样转换完成时刻与主循环周期的固定相位关系,从而有效控制采样偏移抖动带来的控制振荡。其同步控制系统时序如图3所示。

2.2 以太网通信

以太网通信作为当前运用最为普遍的通信方式,已成为工业设备调试及信息交互不可或缺的手段。传统以太网协议栈软件体积较大,需要具备大容量内存的CPU及操作系统来实现。

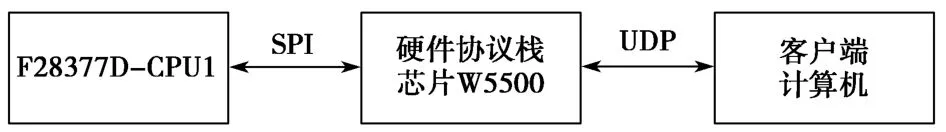

为满足小型MCU处理器系统对外以太网通信的需求,本平台采用“F28377D+硬件协议栈芯片W5500”的方式来实现以太网通信,其内部数据流为F28377D内核CPU1与W5500进行SPI通信传输的数据,W5500与客户端计算机之间按照特定的TCP/IP协议进行用户数据报协议(user datagram protocol,UDP)通信来传输数据,其数据流如图4所示[3-4]。相较现有的“ARM+以太网物理层芯片”方案,本文所提方案可降低开发难度、减轻工作量、提高系统集成度、使系统运行更加稳定;且以太网通信模块的应用为波形监视、故障记录、程序远程加载等功能的设计提供了基础[5]。

图4 以太网通信数据流Fig.4 Ethernet communication data flow diagram

2.3 波形监视

为了在产品开发过程中调试,本平台利用已开发的以太网通信方案,设计并开发了波形监视功能。基本原理为:CPU2将待监视数据存储到片内RAM存储器中;CPU1读取RAM中待监视的数据,其通过W5500发送给上位机软件并以波形的形式显示出来[6]。

根据应用的需求,波形监视方案设计要点如下:

(1)CPU2配置16个待监视变量。

(2)为防止出现数据丢失现象,在CPU2片内RAM中配置2个缓存区间,每个缓存区间大小为160个字(缓存10次),以实现乒乓缓存。

(3)为防止CPU1重复接收数据,在CPU1读取待监视数据程序里定义了防止重复读取标志位。

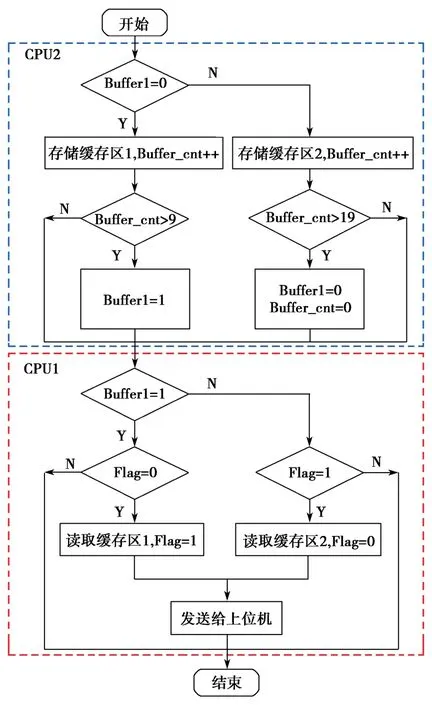

波形监视流程如图5所示。图中,Buffer1是用来表示缓存区间1和缓存区间2缓存数据满标志位。该标志位只能由CPU2对其进行写操作,CPU1只能对其进行读操作。标志位为1,表示缓存区间1存满数据;标志位为0,表示缓存区间2存满数据。Buffer_cnt为缓存次数变量,每个缓存区缓存10次。Flag为防止重复读取标志位,标志位为0,表示缓存区间1数据未被读取;标志位为1,表示缓存区间2数据未被读取。该标志位只能由CPU1对其进行写操作,CPU2只能对其进行读操作。

图5 波形监视流程Fig.5 Waveform monitoring flow diagram

图5中,蓝色虚线框内为CPU2将待监视数据存储到片内RAM的流程;红色虚线框内为CPU1将RAM里的待监视数据读取出来,并采用以太网通信方式发送给上位机软件后以波形的形式显示出来的流程。

本方案对波形监视中可能出现丢失数据和重复接收数据的情况做了相应的处理。首先,数据丢失和重复接收是由于CPU2存满一个缓存区间所用的时间(T2)与CPU1读取一个缓存区间所用的时间(T1)不匹配而导致的。如果T1>T2,则会出现数据丢失情况,此时可通过增加每个缓存区间的缓存次数来解决该问题,即增大每个缓存区间的存储容量;如果T1<T2,则会出现重复接收数据的情况,此时通过判断Flag的值并做相应处理来解决该问题。

2.4 故障记录

为了提升产品的质量,故障记录在工业传动产品应用过程中是不可或缺的。本平台故障记录的基本原理为:F28377D内核CPU1接收故障反馈信息,再将此故障信息传输给CPU2;若没有故障发生,CPU2将在环形缓存区更新并存储故障前数据;若有故障发生,CPU2将在环形缓存区更新、存储故障后数据并在存储完后告知CPU1,CPU1将禁止CPU2更新环形缓存区内数据,同时,将环形缓存区内数据存储到NOR flash存储器,待CPU1完成故障信息存储再通知CPU2更新环形缓存区内数据[7]。

根据应用的需求,故障记录方案设计要点如下:

(1)在SDRAM内配置环形缓存区,大小为120 000个字节,即60 000个字。存储20个16位的变量,每个变量故障前存储2 000个点,即存储空间为2 000个字;故障后存储1 000个点,即1 000个字。

(2)在NOR Flash内配置环形缓存区,分为41块。每块大小为128 KB,存储一条故障记录数据,擦除下一数据块用来存储40条故障记录数据。

(3)若无故障,环形缓存区持续更新、存储故障前数据;若发生故障,环形缓存区更新存储故障后数据(共计1 000个点)。

(4)禁止更新环形缓存区内数据,并将环形缓存区内数据存储到NOR Flash存储器中。

根据应用需求,故障记录模块需要保存最新的40条故障记录数据。由于本平台没有相应操作系统来对文件进行管理,这就要求平台能够记住上一次故障记录数据存放在NOR Flash内的位置。本平台采用的防掉电连续存储方案如下:

(1)在NOR Flash内配置一个环形缓存区,将其均分为41块区域,依次为扇区1,......,扇区41,每块大小为128 KB。

(2)依次读取(从第1到第41扇区)41个扇区的第1个字节,若第1个字节为0xFF,则表示该扇区没有存储数据,并将此次故障记录数据存储到该扇区。

(3)擦除步骤(2)中存储故障记录数据扇区的下一个扇区。

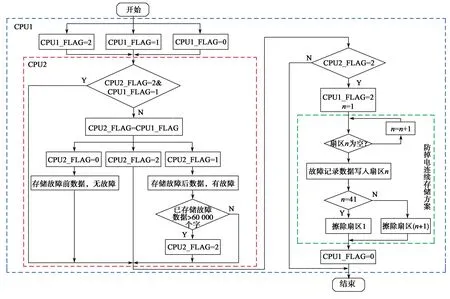

故障记录流程如图6所示。图中,红色虚线框内流程为CPU2核内执行的将故障记录数据存储到SDRAM的过程;蓝色虚线框内除去红色虚线框内流程外,其他流程为CPU1核内执行的将故障记录数据从SDRAM存储到NOR Flash的过程;绿色虚线框内流程为防掉电连续存储方案。

图6 故障记录流程Fig.6 Fault record flow diagram

图6中,CPU1_FLAG=0,表示没有故障发生;CPU1_FLAG=1,表示有故障发生;CPU1_FLAG=2,表示有故障发生且CPU2已经将故障记录数据存储到SDRAM的环形缓冲区,此时CPU1正在将环形缓冲区中的数据存储到NOR Flash,并且禁止CPU2向SDRAM的环形缓冲区存储数据。CPU2_FLAG=0,表示没有故障发生,此时正在向环形缓冲区更新故障前数据;CPU2_FLAG=1,表示有故障发生,此时CPU2正在向环形缓冲区存储故障后数据;CPU2_FLAG=2,表示有故障发生且CPU2已经将故障记录数据存储到SDRAM的环形缓冲区,此时正在等待CPU1将环形缓冲区中的数据存储到NOR Flash。CPU1_FLAG只允许CPU1对其进行写操作,CPU2只能对其进行读操作;CPU2_FLAG只允许CPU2对其进行写操作,CPU1只能对其进行读操作。

2.5 程序远程加载

现有的MCU应用程序更新的主要过程为:利用仿真器通过MCU的联合测试工作组(joint test action group,JTAG)接口将应用程序下载到MCU内部闪存中,以对应用程序进行升级[8-9]。然而该种更新方式需要拆开控制器才能将仿真器连接到MCU,可操作性不强。另外,控制器若是从主电路取电,在升级过程中则可能存在安全隐患,也容易出现应用程序更新失败的情况,从而使得程序升级工作效率偏低[10-11]。因此,本文提出了一种基于以太网通信的可靠、稳定、高效的MCU应用程序升级方法。

本文使用的F28377D芯片包括两个内核,每个内核都有其独立的片内RAM和片内Flash,供每个内核自身使用[12]。每个内核的片内Flash分为两个区间,分别存储其对应的Boot程序和应用程序[13]。内核CPU1可与上位机进行以太网通信,通过上位机实现将应用程序装载到片内FLASH中存储应用程序的区间[14]。F28377D程序远程更新主要分为以下几个步骤:

(1)上位机通过以太网向F28377D发出更新请求。

(2)F28377D控制其内核CPU1和内核CPU2处于应用程序更新状态。

(3)上位机通过以太网将升级程序发送给内核CPU1和/或内核CPU2。

(4)MCU根据接收到的升级程序对对应的应用程序进行升级。

F28377D的内核CPU1更新程序详细步骤如下:

(1)上位机将升级程序分为多页数据包,并依次将每页数据包发送给内核CPU1。

(2)内核CPU1依次对数据包进行页校验。若页校验通过,则将该页数据包存储到内核CPU1中;否则上位机重新发送对应页数据包。若同一页数据包页校验3次均不通过,则停止升级。

(3)当升级程序的所有页数据包均被存储于内核CPU1中时,内核CPU1对接收到的升级程序进行程序校验;若程序校验通过,则上位机提示升级程序成功,否则提示升级程序失败。

F28377D的内核CPU2更新程序详细步骤如下:

(1)上位机将升级程序分为多页数据包,并依次将每页数据包发送给内核CPU1。

(2)内核CPU1将接收到的数据包依次发送给内核CPU2。

(3)内核CPU2对读取的数据包进行页校验。若页校验通过,则将该页数据包存储到内核CPU2中;否则上位机重新发送对应页数据包。若同一页数据包页校验3次均不通过,则停止升级。

(4)当升级程序的所有页数据包均存储于内核CPU2中时,内核CPU2对接收到的升级程序进行程序校验;若程序校验通过,则上位机提示升级程序成功,否则提示升级程序失败。

3 结语

基于目前工业实时控制器平台架构复杂、成本高等问题,本文提出并设计了基于F28377D的控制系统软件平台方案。该方案不仅满足了工业实时控制器的功能需求,同时改变了传统平台的开发方式,实现了平台的集约型开发,原有平台开发需要3人,每人开发用时2个月,本方案设计平台只需1人开发,开发用时3个月,缩短了平台开发周期;另外,原有平台需要“ARM+FPGA+DSP”3块芯片,而本方案只需要单片F2837TD芯片,简化了平台数据流,控制器降本约30%。该平台在空调螺杆机变频器产品上批量装机应用数千套,连续稳定无故障运行一年以上,验证了该平台的可靠性。

为了满足工业实时控制器日益增加的应用需求,后续本平台可以利用其内部协处理器,将故障诊断及旋变软解码等功能布局在协处理器内,以实现单芯片4核控制。