一种基于IC_NQC的数字振镜位置检测方法

廖文鑫,陈光胜

(上海理工大学机械工程学院,上海 200093)

0 引言

振镜是激光振镜扫描的核心部件,由于数字振镜抗干扰能力强,已成为研究激光振镜扫描的主要方向。在高精度数字振镜控制系统中,通常采用正余弦编码器获取高精度位置数据,但正余弦编码信号的纠偏和细分效果是影响位置检测效果的重要因素。现阶段常见的细分方法包括CORDIC 反正切算法细分、麦克劳林级数算法细分、闭环跟踪算法细分、跟踪环路算法细分等。

王强等[1]提出的CORDIC 反正切算法和李雪等[2]提出的优化CORDIC 反正切算法均在FPGA 上实现,但这类方法都不可避免地需要进行多次角度旋转、运算迭代来计算细分值,迭代次数越多,细分精度也就越高,但运算处理时间也会随之增加,造成算法获取高精度位置周期长、消耗大。刘海龙等[3]提出运用麦克劳林级数展开式反向数据,直接拟合正余旋编码信号的相位以计算细分值,该方法获取的细分值精度直接取决于正余旋编码信号的质量,因此对调理硬件电路设计的要求过高。吴立等[4]提出的闭环跟踪算法细分和马泽龙[5]提出的跟踪环路算法都通过构建闭环结构计算当前角度与辨识角度误差,以实时调整辨识角度,调整后的辨识角度即为细分值,该类方法的细分数可高达223,但构建的闭环结构十分复杂,运算环节较多,对硬件资源消耗极大。

为在减少算法对FPGA 硬件资源的消耗、简化电路设计的同时,满足位置获取周期的要求。本文运用外部芯片处理正余弦编码信号纠偏和细分,FPGA 读取和解码芯片的位置数据信息。具体的,利用IC_NQC 芯片完成正余弦编码信号的纠偏和细分,然后利用BISS_C 模块配置IC_NQC 芯片读取振镜位置信息,最后通过解码模块获取振镜位置。其中,位置获取精度由配置参数决定,位置获取速度由BISS_C 通信协议周期决定。

1 IC_NQC

IC_NQC 是IC_Haus 公司出厂,带信号校准的13 位Sin/D 转换器,采用BISS_C 协议进行通讯。通过动态纠偏和细分技术,将正余弦编码信号数字化处理为细分精度可调的位置数据信息。采用数字量动态补偿获取高质量的正余弦编码信号,首先利用内部集成的A/D 转换器采样当前正余弦信号并将数据传输至IC_NQC 内部控制器,然后通过控制器测量当前正余弦信号的直流电平、幅值和相位并计算相对应的补偿值,接下来将补偿值写入对应的偏置寄存器,最后通过D/A 转换器调节可编程硬件电路,实现对正余弦编码信号的纠偏。

纠偏过程需要预先配置寄存器的信号调节类功能位。例如,增益选择(GAIN)、sin 信号偏移校准(SINOFFS)、cos信号偏移校准位(COSOFFS)等。纠偏后的正余弦信号既需要通过IC_NQC 内置的周期计数器累计正余弦信号个数,还要经过反正切硬件电路进行细分。细分精度由反正切运算精度决定[6],反正切运算精度由寄存器的分辨率位(SELRES)决定。周期计数器值和反正切值由BISS_C 进行通信传输[7],根据配置寄存器的BISS 类功能位设置协议版本(Protocol Version)、数据输出选项(M2S)及超时(TIM0)。

2 数字振镜位置检测原理

数字振镜位置检测原理如图1 所示。其中,Mecury_1200 相对编码器一般安装于振镜电机底部,当振镜电机摆动时,Mecury_1200 会输出差分正弦信号、差分余弦信号和差分零位信号[8]。为提高信号质量,这三组差分信号会分别经过IC_NQC 接口电路进行滤波处理。具体的,由FPGA的IC_NQC 配置模块发送命令帧,通过BISS_C 通讯模块的时钟线MA 将命令帧传输至IC_NQC 芯片,复位芯片开始配置寄存器[9]。然后,利用IC_NQC 芯片对差分信号进行数字量动态纠偏,通过硬件电路对信号分别进行计数和反正切细分运算,以取得数字量位置数据信息。最后,通过BISS_C 通信模块的输出线(SLO)与零位信号线(Zero)提取数字量位置数据中的周期计数数据(P)、角度数据(A)和零信号数据(Z),并通过位置解码模块获取当前振镜电机的位置数据。

Fig.1 Principle of digital galvanometer position detection图1 数字振镜位置检测原理

3 IC_NQC通讯与软件设计

3.1 通讯协议

3.1.1 寄存器写操作命令帧

为实现IC_NQC 芯片通讯,必须首先配置芯片寄存器功能位[10]。图2 为利用BISS_C 协议对寄存器执行写操作的一个命令帧的数据结构。

其中,初始位主要用于等待上一次命令帧的结束,由14bit 组成;起始位(S)、停止位(P)及控制选择位(CTS)都为1bit,前两者取1,后者取0;器件地址(IDL)主要为IC_NQC 的确定地址;读控制位(R)与写控制位(W)为低电平有效,执行写操作取1;寄存器地址位(ADR)和寄存器配置数据(DATA)需要根据功能选择相应的寄存器标志位进行配置;校验位(CRC)是CRC 校验的结果值,第一个用于校验IDL 与ADR 组合数据,后一个是用于校验DATA数据。

Fig.2 Command frame data structure图2 命令帧数据结构

3.1.2 寄存器写操作

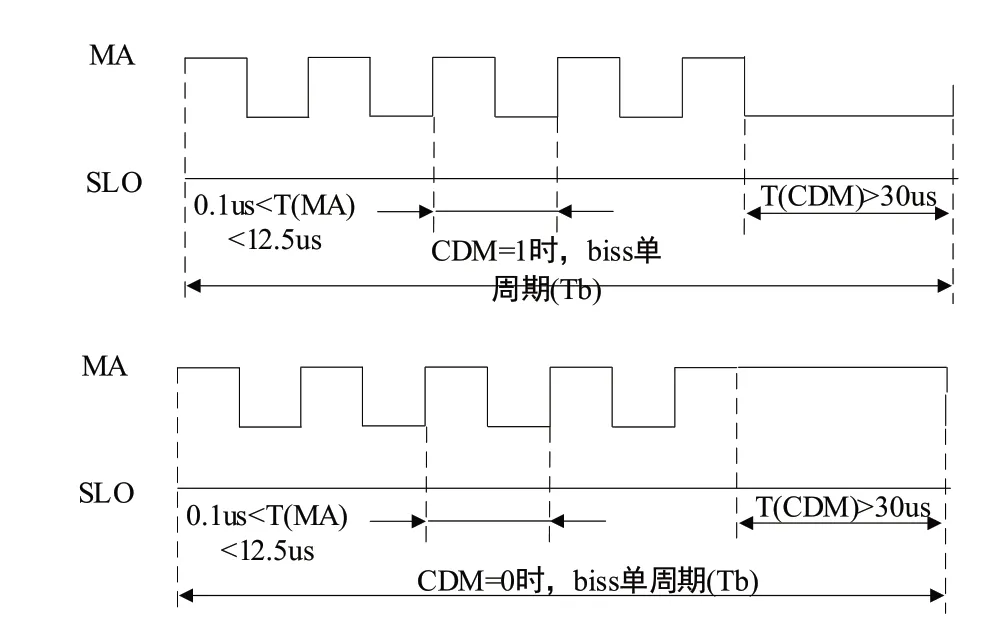

写操作主要将命令帧数据的每一位,通过时钟线MA的控制数据操作位CDM 发出,命令帧数据的每一位均需要一个BISS_C 单周期传输[11]。IC_NQC 芯片寄存器写操作主要分为以下两种:

(1)如图3 所示,IC_NQC 复位写操作[12],数据传输线SLO 一直为高电平1,时钟线MA 连续发出4 个脉冲,单个脉冲时间周期范围为0.1~25us,随后发送CDM 位的反码,持续时间要超过30us。

Fig.3 IC_NQC reset write operation BISS_C single cycle sequence图3 IC_NQC复位写操作BISS_C单周期时序

(2)如图4 所示,寄存器配置写操作[13],当芯片复位后对IC_NQC 芯片寄存器的其它功能位进行写操作,在MA的第2 个脉冲上升沿,SLO 进入应答位(ACK)默认为0,第3 个脉冲上升沿进入开始位(Start)默认为0,第4 个脉冲上升沿进入控制数据抓取位(CDS),电平状态与上一个BISS_C 周期的CDM 位相同,在最后一个脉冲上升沿MA 进入CDM 位,发送CDM 的反码,SLO 进入超时阶段(Time⁃Out),电平与CDS 位相同,并且保持至少46 个MA 脉冲周期以上,单个MA 脉冲周期最短为0.1us。

Fig.4 Register configuration write operation BISS_C single cycle se⁃quence图4 寄存器配置写操作BISS_C单周期时序

3.1.3 位置数据信息采样

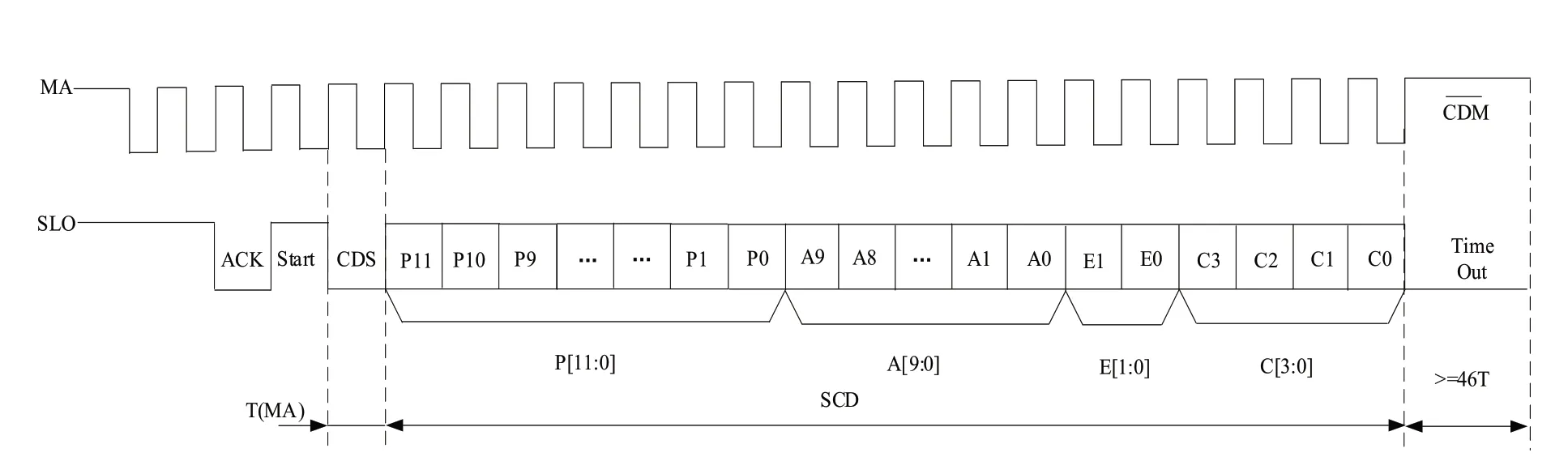

图5 为位置数据信息采样BISS_C 单周期时序图。时序中,前4 个时钟线MA 脉冲对应的数据线SLO 变化和MA脉冲周期时间的要求与图4一致。

在第5 个时钟上升沿MA 不再进入CDM 位,而是作为采样时钟采集单周期数据SCD。单周期数据SCD 主要包括周期计数数据P、角度数据A、错误标志位ERROR 和校验位CRC。其中,错误标志位为2 位,周期计数数据位P、细分数据位A 和校验位CRC 均需通过寄存器数据进行配置。当MA 进入CDM 发送CDM 的反码时,CDM 电平取0,SLO 进入超时阶段(TimeOut),电平取0,并且保持至少46个MA 脉冲周期以上。

Fig.5 Location data information sampling BISS_C single cycle sequence图5 位置数据信息采样BISS_C单周期时序

3.2 软件设计

3.2.1 通讯流程

图6 为FPGA 与IC_NQC 通讯流程图,时钟线MA 波特率设置为5MHZ。首先,通过IC_NQC 进行复位写操作,BISS_C 通信模块以图4 时序方式对IC_NQC 芯片逐位发送复位类寄存器功能位的命令帧。若零位置信号Zero 从高电平转为低电平时,则代表复位完成,否则重新执行复位操作。复位完成后,对IC_NQC 芯片进行寄存器配置写操作,即通过BISS_C 通信模块以图5 时序方式逐位发送各寄存器功能位的命令帧。若在BISS_C 周期中,数据线SLO的CDS 位与上一周期的CDM 位(设为CDM1)均一致,则代表IC_NQC 寄存器配置完成,否则寄存器配置失败,需重新回到复位操作。

寄存器配置完成后,通过BISS_C 通信模块以图5 时序方式采集IC_NQC 的单周期数据SCD,对周期计数数据位P和细分数据位A 的数据组合进行CRC 校验(CRC 校验的多项式由寄存器功能位M2S 决定),若校验值的二进制表示与CRC 校验位一致,则代表采集数据无误,接下来将数据输入位置解码模块进行处理,否则等待数据线SLO 超时阶段(TimeOut)结束,进行下一BISS_C 周期位置数据采集。通常在实际应用中,由于CRC 校验正确代表着检测错误标志位必然正确,因此省略了错误标志位E[1:0]检验。

Fig.6 FPGA and IC_NQC communication flow chart图6 FPGA与IC_NQC通讯流程图

3.2.2 位置解码

IC_NQC 位置数据由周期计数器P 与角度值A 构成,均为二进制表示。周期计数器P 累计一段弧度经过正余弦个数,为了保证位置坐标的唯一性,周期计数器P 累计最大正余弦个数所表示的弧度必须超过振镜摆动范围。

由于采用相对位置编码器,为了确定唯一坐标,零信号位置对应坐标零点,周期计数器P 应全表示为0[14]。角度值A 为正余弦反正切计算的细分值,角度值A 的单位值代表位置坐标的最小分辨率[15]。振镜运动方向由周期计数器P 和角度值A 累计的方式予以体现[16-17],当振镜运动经过一个正余弦时,顺时针周期计数器P 累计递减,逆时针运动P 累计递增;当振镜运动未经过一个正余弦时,顺时针角度值A 累计递减,逆时针角度值A 递增累计。此外,当零信号位置顺时针移动一个正余弦,周期计数器P表示为全1。

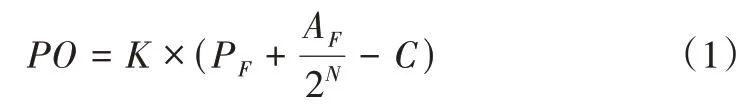

为了便于后续处理位置坐标值,需要将位置值表示为32位浮点数。计算公式如式(1)所示。

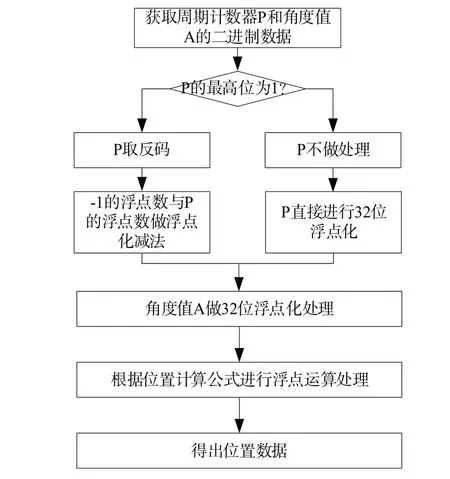

其中,PF为P 处理后的32 位浮点化值的十进制表示。具体处理过程为:当P 的最高位为1 时,P 作反码运算,并进行32 位浮点化处理,最后与-1 的32 位浮点数作浮点数减法得到32 位浮点数PF;当P 的最高位为0 时,直接进行32 位浮点化得到PF。AF为A 的32 位浮点数的十进制表示,2N为细分数(N为角度值A 的位数),C为零信号位置与实际位置坐标零点的偏置值,K为编码器坐标与实际位置坐标转化的角度系数[18]。图7为位置解码流程图。

Fig.7 Flow chart of location decoding图7 位置解码流程图

4 实验结果与分析

如图8 所示,实验搭建的数字振镜位置检测实验平台采用某一国产摆动电机并安装有振镜片[19],电机摆动范围为±0.191 9rad,电机底部安装Mercury_1200 正余弦相对编码器,单位正余弦对应的弧度为2.308mrad。控制主板的控制主芯片型号为XlinxSpand6LX45,并安装有13 位Sin/D转换器IC_NQC。

Fig.8 Experimental platform图8 实验平台

在ISE14.6 软件环境下,分别对CORDIC 反正切算法细分检测方法[20-21]、麦克劳林级数算法细分的检测方法、闭环跟踪算法细分的检测方法及本文采用的IC_NQC 细分检测方法进行比较,设置以上方法的细分数均为1 024,通过型号为XlinxSpand6LX45 的FPGA 实现并进行综合编译。其中,寄存器、查找表和片选等FPGA 核心硬件资源消耗数量如表1所示。

Table 1 Comparison of FPGA hardware resource consumption表1 FPGA硬件资源消耗对照表

由表1 可见,采用IC_NQC 细分方式的检测方法寄存器和查找表和片选消耗都至少减少了30%。

将IC_NQC 细分检测方法作为三闭环控制器的位置反馈环,设置细分精度为2.25urad。通过fifo 模块采集位置数据,UART 串口进行传输,由MATLAB 进行数据处理和显示,采样时间为28.1us。零点位置波动图如图9所示。

Fig.9 Zero position fluctuation图9 零点位置位置波动

由图9 可见,控制器的定位误差为9urad,能够满足高精度振镜控制对重复定位误差的要求。

通过三闭环控制器将振镜固定至零点位置,控制振镜间歇式作20ms 的匀速摆动,单周期匀速运动时间为10ms,速度为4mrad/s,运动位置波动图如图10所示。

由图10 可见,3 个周期匀速运动阶段平均速度分别为4.037mrad/s、4.015mrad/s 和4.009mrad/s,最大速度误差为0.037mrad/s,能够满足高精度振镜控制对速度偏差的要求。

5 结论

通过实践验证,IC_NQC 细分方式相较于以往检测方法,在相同位置检测精度的条件下,硬件资源消耗至少了减少了30%,位置获取周期为28.1us,通过1 024 细分方法能够有效满足高精度数字振镜控制对位置获取及误差的要求。

Fig.10 40mrad/s constant speed intermittent motion position fluctu⁃ation图10 40mrad/s匀速间歇运动位置波动图