基于PUF的JTAG安全认证架构

王 凯,李校南,刘燕江,陈 韬,李 伟

(1.信息工程大学 信息安全重点实验室,河南 郑州 450001;2.96901部队,北京 100094)

0 引 言

随着半导体和集成电路技术的发展,SoC(system on chip)通过将通用处理器、系统总线、接口和存储等模块集成到单颗芯片中,能够独立搭建一个完整的片上系统,满足用户多样化的应用需求,已经成为了当前信息系统的核心部件[1]。JTAG(joint test action group)作为一种国际标准调试协议(IEEE1149.1)在芯片测试和系统调试中受到了广泛应用。如果对所有用户开放SoC的JTAG调试权限,必然造成严重安全隐患[2]。因此,必须对JTAG调试增加安全防护措施,以保证SoC安全。

近年来,国内外学者针对JTAG接口保护的研究主要从以下几个方面展开。文献[3]采用了两层机器学习的JTAG安全防护方案,通过支持向量机(support vector machines,SVM)监测用户操作的合法性来抵御JTAG非法攻击。文献[4]通过基于机器学习的三级监测器和阴影寄存器,实现了JTAG调试的可控性和可观测性,实现了保护JTAG接口的目的。文献[5]提出了一种对JTAG内部TAP控制器数据加密,进而保护JTAG内部敏感信息泄露的安全防护方式。而文献[6]则采取了一种对整个扫描链数据进行加密的方式,实现了对JTAG接口的安全防护。

上述文献主要从JTAG接口安全认证、机器学习监测和JTAG数据加密等方式完成对JTAG接口的保护,其中现有的JTAG方式大多基于公钥密码算法实现,虽然安全性较高,但是硬件开销大,且认证效率低。而通过机器学习监测用户操作,也很难抵御所有的JTAG攻击方式,安全性不足。而JTAG数据加密虽然能够防止敏感信息泄露,但也带来了硬件开销大,降低调试效率的严重问题。

针对SoC在资源受限条件下的JTAG接口安全认证的问题,结合SoC电路基本结构,本文深入分析了JTAG安全防护需求、HMAC身份认证协议和SRAM-PUF密钥生成,提出了一种基于SRAM-PUF的低成本JTAG接口安全认证架构,在保证合法用户正常调试需求的同时,有效抵御攻击者非法入侵系统,保护SoC中敏感信息的安全性。

1 SRAM-PUF密钥生成模型

HMAC协议由H.Krawezyk、M.Bellare、R.Canetti提出,是一种基于哈希运算消息认证码的身份认证协议,近年来HMAC协议广泛应用在多种安全认证服务中,其安全性能够抵御多种形式的攻击,并经受了多个安全应用的考验[7]。HMAC协议的安全性基础在于合法用户与JTAG接口间的共享密钥。如何确保密钥的可靠生成与安全存储是保证HMAC认证协议安全性的关键。而密钥的可靠生成与安全存储通常需要满足以下3个基本条件:

(1)生成随机性。随机性是衡量密钥质量的重要指标。安全性强的密钥应当具有良好的随机性和密码特性,进而保证其唯一性和不可预测性,确保整个HMAC协议的安全性。

(2)存储安全性。密钥在应用过程中必须有一段独立的受保护的存储空间,防止非法用户通过各种攻击手段获取到密钥的正确内容。

(3)应用可靠性。在HMAC协议中,密钥作为合法用户的身份标识,一旦密钥存在误码,则将导致HMAC消息认证码与实际不符,进而导致认证失败。

要正确实现基于HMAC身份认证的安全JTAG调试协议,合法用户与安全JTAG接口间的共享密钥可靠性是关键。而传统的密钥生成器大多借助于某种噪声源产生具有较好统计分布特性的序列,再对这些序列进行复杂的随机性检验过程以确保其具有较好的密码特性。这种方式一方面需要经过复杂的随机性检验过程,另一方面也难以重复产生相同的密钥,可靠性较差[8]。基于此,国内外科研工作者提出了基于PUF(physical unclonable function)的密钥生成方法。该方法能够很好满足以上3个基本条件,其基本原理是利用芯片在制造过程中,由于工艺限制,使得每颗芯片都拥有其独特的“物理指纹”[9]。PUF的主要特点在于针对每一个激励(challenge),不同的PUF电路会产生不同的响应(response),即每颗芯片都具有其独特的激励响应对(challenge-response pairs,CRPs),因而具有较强的随机性、鲁棒性、不可预测性和不可克隆性,近年来在密钥生成和用户身份认证得到了广泛应用。

1.1 SRAM-PUF基本原理

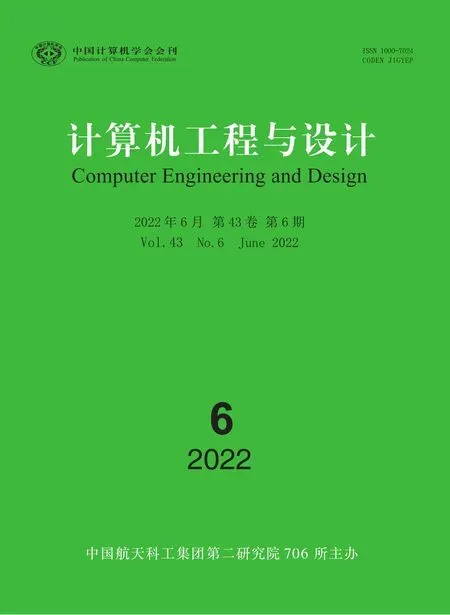

SRAM-PUF的基本原理就是,不同的SRAM单元受工艺限制,导致两个反相器中MOS管的“强度不同”,进而使其在流片后表现出不同的上电特性,如图1所示[10]。因此,SRAM存储单元的上电初始值即可作为SRAM-PUF。

图1 SRAM-PUF基本原理

定义SRAM中的一对MOS管的晶体管参数分别为I1和I2,此时SRAM某个响应位的上电初始值r可以表示为式(1)

(1)

从理论上来讲,对于特定的SRAM-PUF电路结构,在每次上电时,每个存储单元出现“0”和“1”的概率各占50%。而实际工作过程中,I1和I2均受到阈值电压、温度和老化程度影响,假设二者的差值为ΔI,标准偏差为σ,则此时SRAM某个响应位的上电初始值r′可以表示为式(2)

(2)

假设芯片在两次上电过程中,某一SRAM单元初始值不同的概率Pe,则其值可表示为式(3)

(3)

对一般SRAM而言,其中某一存储单元两次上电初始值不同的概率Pe通常不大于15%[11]。

以一个16×16的SRAM存储单元为例,其上电初始值的分布模型如图2所示[12]。在每次上电时,某些存储单元的上电初始值固定为“0”,某些单元的上电初始值固定为“1”。还有一小部分单元的上电初始值受到温度、电路老化和噪声等因素的影响,其上电初始值可能为“0”也可能为“1”。这些上电初值不稳定的存储单元,是影响SRAM-PUF响应可靠性的主要原因。

图2 16×16-SRAM上电初始值分布模型

1.2 SRAM-PUF密钥生成模型

为了从SRAM-PUF这种带噪声的芯片“物理指纹”中,提取出能够精确再生且随机分布的密钥,本文采取了一种基于模糊提取器(fuzzy extractor)的可靠密钥生成模型。该模型由Dodis等提出,近年来在指纹识别、虹膜识别和量子信息等领域得到了广泛应用[13]。基于模糊提取器的可靠密钥生成模型,按照其实现过程,大体可以分为密钥注册和密钥重构两个阶段。密钥注册模块电路结构如图3所示[14]。

图3 密钥注册模块电路结构

c=α⊕p

(4)

b=ENC(β)

(5)

s=b⊕p

(6)

(7)

(8)

密钥重构模块电路结构如图4所示。

图4 密钥重构模块电路结构

b′=p′⊕s

(9)

β=DEC(b′)

(10)

b=ENC(β)

(11)

c′=α⊕b⊕s

(12)

(13)

根据式(3),假设在任意k位SRAM存储单元中,上电以后出现i位错误的概率为Pi,则其值可以表示为式(14)

(14)

设t为所选纠错算法的最大纠错能力,那么若要从k位SRAM-PUF中成功完成密钥重构,则SRAM-PUF的最大错误位数不能超过t。因此,从k位SRAM-PUF从成功完成密钥重构的概率Psuccess可以表示为式(15)

(15)

在实际应用过程中,要完成可靠密钥生成,通常要求纠错的失败率小于10-6[15],即

Psuccess≥0.999 999

为了实现对PUF的纠错,近年来国内外学者提出了大量的纠错算法,如重复码、格雷码、循环码和BCH码等。在众多的纠错算法中,BCH码具有纠错能力强,纠错能力可控等特点,非常适合应用于SRAM-PUF纠错中。现有BCH码纠错的主要缺陷在于译码相对复杂且硬件开销大[16]。

在SoC安全JTAG调试中,HMAC认证所需共享密钥只需在上电初始化时生成即可,因此其生成速度不会影响系统运算性能。而面积开销则是衡量SRAM-PUF密钥生成的关键指标。为了解决现有SRAM-PUF可靠密钥生成硬件开销大的问题,本文设计了一种基于模糊提取器和小位宽BCH码的密钥生成模型,能够满足资源受限条件下的可靠密钥生成。

SRAM-PUF低成本安全可靠密钥生成过程如算法1所示。

Algorithm 1: 基于模糊提取器的注册密钥生成算法

Input:x,α,β,Ψ

Output:K,C

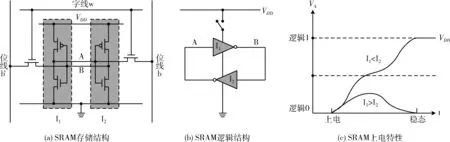

(1) For j (2)pj←P(xj); (3)cj←αj⊕pj; (4)bj←E(βj); (5)sj←bj⊕pj; (8)P(xj)←11…1; (10) End for (11)C←{C1,C2,…,CN}; SRAM-PUF的重构过程如算法2所示。 Algorithm 2: 基于模糊提取器的密钥重构算法 Input:x,C,Ψ (1) For j (3)p′j←P(xj); (4)b′j←p′j⊕sj; (5)βj←D(b′j); (6)bj←E(βj); (7)c′j←αj⊕(bj⊕sj); (9)P(xj)←11…1; (10) End for 图5 HMAC身份认证流程 由图5可得,HMAC身份认证协议的安全性基础在于合法用户与网络信息系统间的密钥共享。因此,要安全可靠实现SoC的JTAG调试,必须确保SRAM-PUF密钥生成的可靠性,以及HMAC协议实现过程的安全性,二者缺一不可。 如何保证JTAG调试用户的安全性,是防止非法用户入侵系统造成敏感信息泄露的关键。基于HMAC安全认证的JTAG安全防护思想,就是在标准JTAG协议的基础上增加身份认证过程。扩展接口安全认证后的JTAG连接初始化过程如图6所示。 图6 JTAG安全调试流程 根据图6,整个JTAG安全调试过程可以分为JTAG认证过程和JTAG调试过程两部分。其中JTAG认证过程主要用于SoC通过HMAC协议判别调试用户的合法性,进而阻止非法用户入侵系统。合法用户经过HMAC身份认证以后,JTAG模块将开启JTAG调试通道,允许用户进入JTAG调试过程,进而实现调试程序的编译和执行,完成对整个SoC的调试和控制。 本文以RISC-V处理器的JTAG调试为例,开展安全JTAG调试协议设计与实现。作为整个JTAG调试的核心,用户能够通过TAP控制器完成调试指令和数据的注入,进而实现完整的JTAG调试操作。为了在标准JTAG基础上融入安全身份认证协议,需要完成JTAG调试指令扩展和JTAG接口集成HMAC身份认证电路两部分工作。 JTAG调试指令按照其具体的功能可以分为通用指令和专用指令两种。其中通用指令主要完成一些基本的JTAG调试操作,见表1。 表1 通用JTAG调试指令 针对JTAG协议融合HMAC身份认证协议,需要对JTAG调试指令做以下几条用户身份认证指令扩展,见表2。 表2 JTAG扩展用户身份认证指令 为了使标准JTAG接口能够支持JTAG扩展用户身份认证指令,进而实现安全JAG调试,需要进一步修改TAP控制器中IR寄存器,并在JTAG接口内部集成HMAC身份认证模块和调试通道控制器。完整的安全JTAG调试接口,其整体架构如图7所示。 图7 安全JTAG接口电路整体架构 整个安全JTAG接口按照其功能,可以划分为DMI模块、HMAC身份认证模块、DM模块、调试通道控制器、主机接口和从机接口6个部分。其中DMI模块主要接收来自调试适配器的JTAG调试信号并通过协议转换,进而完成调试指令和调试数据的读写访问。HMAC身份认证模块则完成执行调试认证过程,并控制调试通道控制器的开启和关闭。DM模块则负责根据外部注入的调试指令和数据,完成相应的调试操作,并在调试通道控制器开启时,实现对RISC-V处理器的调试控制,以及对片上存储资源的读写访问。 为了验证本文设计架构的合理性、安全性和可靠性,本文基于RISC-V处理器、安全JTAG接口、AMBA总线、SRAM-PUF和UART等单元,搭建了一套SoC验证平台,并通过了功能仿真,其结果如图8所示。 图8 基于SRAM-PUF的安全JTAG调试仿真波形 根据图8,本文中基于SRAM-PUF的安全JTAG调试能够从带噪声的SRAM-PUF响应中生成可靠密钥,并基于该密钥实现基于HMAC协议的JTAG安全认证。 SoC中JTAG调试的安全性,直接决定了整个系统的安全性。而在本文设计的安全架构下,HMAC协议的安全性,以及用户与SoC间共享密钥的安全性,是整个系统的安全性基础。下面针对典型的JTAG攻击方式,对整个调试协议进行安全性分析。 (1)重放攻击 对安全JTAG认证进行重放攻击,是指攻击者向JTAG接口发送一个合法用户已经发送过的数据包,进而达到欺骗JTAG接口的目的。而每次HMAC身份认证时,SoC都会生成一组新的随机数r,保证了认证的实时性。因此即使攻击者能够捕获到上一次的身份认证通信内容,也无法在下一次身份认证时使用。 (2)克隆攻击 相比于重放攻击,克隆攻击对攻击者有着更高的要求,即:①攻击者必须了解整个身份认证协议的运算过程和通信内容;②攻击者必须要有和合法用户相同的计算能力;③攻击者必须掌握合法用户的私密信息(即HMAC协议中的共享密钥K)。HMAC协议采用的是单向杂凑函数,且共享密钥长度大于杂凑算法分组长度(SM3为512 bit),使现有的计算平台无法实现克隆攻击。 (3)猜想攻击 猜想攻击是指攻击者在已知合法用户与JTAG接口间通信内容的基础上,从中分析提取出共享密钥。这种攻击方式对于攻击者的运算能力要求比克隆攻击更高,必须采用高强度的密码破解算法。而用户要想对认证密钥进行猜想或穷举,在实现上也是不可行的。 (4)中间人攻击 中间人攻击需要攻击者能够通过各种技术手段让自己能够作为一个虚拟用户,控制合法用户与SoC之间的数据通信过程。这要求攻击者必须控制信道,且同时欺骗合法用户和JTAG接口。而实际上,合法用户与JTAG接口在认证启动之前,早已完成了密钥共享,由此保证了攻击者无法实现中间人攻击。 (5)监听攻击 监听攻击是一种攻击者通过监听合法用户与安全JTAG接口之间的通信内容,进而从中分析和计算得到系统敏感信息的方式。在安全JTAG认证过程中,通信内容只有该次认证的认证请求、随机数和HMAC值,而并不包含任何与合法用户及安全JTAG身份相关的信息。因而本文中的安全架构能够抵抗监听攻击,从而保护合法用户身份信息。 经过以上分析,本文提出的JTAG接口认证架构,能够抵御典型的JTAG攻击方式,在保证合法用户正常完成JTAG调试的基础上,防止攻击者非法入侵系统并造成敏感信息泄露。 SRAM-PUF生成密钥的安全性和可靠性,是决定整个JTAG认证架构安全性和可靠性的关键。一般来说,按照FPGA芯片实现原理,绝大多数FPGA内部并不存在真实的SRAM存储单元,仅仅依靠FPGA板级验证平台无法完成SRAM-PUF密钥生成可靠性验证。因此本文在实验过程中,采取“SoC芯片+FPGA”方式完成SRAM-PUF密钥生成可靠性验证。其中SoC芯片采用的是实验室已经流片验证成功的某型SoC芯片,其内部集成了存储空间大小为8192×32的SRAM,用作SRAM-PUF单元。而FPGA则选取Xilinx Zynq-7000 FPGA,其中运行模糊提取器实现密钥的注册与重构。SoC芯片与FPGA之间通过UART接口进行通信。系统运行时,SoC芯片内部通用处理器执行汇编程序,读取SRAM-PUF上电初始值并通过UART接口发送给FPGA芯片。而FPGA芯片收到后则通过模糊提取器完成密钥注册/重构,并将其反馈给SoC芯片。 BCH编解码作为模糊提取器实现SRAM-PUF密钥生成的关键模块,不仅其纠错能力决定了密钥生成的可靠性,而且也占据了模糊提取器面积开销的大部分。本文为了寻求SRAM-PUF密钥生成需求、模糊提取器面积开销之间的平衡,基于BCH(63,30,6) 编解码方式完成了模糊提取器设计。即从每组32 bit的SRAM-PUF单元中选取30 bit作为信息位进行纠错编码,此时BCH编码的实际纠错能力为6 bit,纠错率为20%,能够很好满足SRAM-PUF错误率为15%的纠错需求。 另一方面,为了满足PUF生成密钥的安全性需求,本文选取国家密码管理局发布的SM3算法作为模糊提取器中的Hash函数。每当BCH完成对256 bit的SRAM存储进行编解码以后,可以启动SM3算法生成密钥。 为了评估本文提出SRAM-PUF密钥生成架构的密钥生成质量,本文通过一致性指标λ来衡量相同SRAM-PUF生成密钥的可靠性[18],如式(16)所示。其中,X表示SRAM-PUF的存储位数,Y表示实验次数,而ζi,j则表示SRAM-PUF响应值中,第i位在第j次实验中的纠错输出结果 (16) 基于ThermoJet Environment Simulator、Xilinx Zynq-7000 FPGA和SoC芯片搭建了SRAM-PUF一致性测试平台,其中SoC芯片和FPGA开发板放在ThermoJet Environment Simulator的气罩下,测试系统如图9所示。ThermoJet Environment Simulator是一种通过气流为SoC芯片测试提供-80 ℃~+225 ℃温度环境,温度精度±1 ℃,可为芯片温度测试提供长时间稳定的测试环境。 图9 SRAM-PUF一致性测试平台 本文在-20 ℃到80 ℃对SoC芯片内的SRAM-PUF进行温度测试,其中温度间隔为10 ℃,分别对SRAM-PUF进行了300次一致性测试,得到一个300×11的PUF输出响应矩阵。利用式(16)的一致性计算方法计算在11个温度区间下的一致性值,并对比了纠错前后的一致性,具体结果如图10所示。 图10 不同纠错状态下SRAM-PUF一致性统计结果 根据图10可得,在没有BCH编解码纠错的情况下,SRAM-PUF响应的一致性率仅为85%~90%。而经过BCH编解码之后,SRAM-PUF的可靠性可得到大幅度提升,尤其是在温度条件为10~40 ℃时,SRAM-PUF响应的纠错成功率最高可达99.98%,有效提高了SRAM-PUF的鲁棒性,非常适合应用于SoC可靠密钥生成和JTAG接口认证。 为了对本文提出的JTAG架构进行面积和性能评估,将其在CMOS 65 nm工艺下完成了仿真综合,实验结果见表3。 表3 安全JTAG架构 根据表3可得,相比文献[3-6],本文中的JTAG架构在保证用户身份认证安全性的前提下,在面积开销方面具有较大优势,非常适合应用于资源受限条件下的网络信息安全系统下的JTAG。此外,本文中的安全架构硬件开销主要包括JTAG接口扩展HMAC身份认证单元和模糊提取器两部分。该架构虽然整体面积与文献[2]较为接近,但是模糊提取器单元却有更广泛的应用,其生成的密钥不仅可以用作JTAG接口安全认证,还能应用于其它领域,如数据加密和消息签名验证等。 而在实现性能方面,由于文献[3]和文献[4]是通过机器学习检测JTAG调试用户的合法性,而文献[5]和文献[6]是通过JTAG数据加密保护系统敏感信息安全,与本文采取的实现思想差异较大,因而彼此间的比较没有意义。因此,同样是JTAG接口身份认证,本文中的安全架构具有更高的认证效率。 针对SoC中的JTAG接口认证,本文深入分析了SRAM-PUF实现原理、SoC密钥生成需求和HMAC身份认证协议,提出了一种基于SRAM-PUF的低成本可靠JTAG接口认证架构,并完成了实验验证和安全性分析。实现结果表明,该架构能够通过增加少量的硬件资源,实现可靠密钥生成和JTAG接口认证,有效抵御典型的JTAG攻击方式,保证网络信息系统的数据安全性,非常适合应用于各类资源受限条件下的网络信息系统。此外,基于SRAM-PUF生成的密钥也可以应用于其它方面,比如用作会话密钥加密系统敏感信息,或者用作用户私钥完成消息签名等。下一步,本文将继续深入展开研究,进一步提升SoC和信息系统的安全性。

2 基于SRAM-PUF的JTAG调试认证

2.1 HMAC身份认证协议概述

2.2 安全JTAG调试协议

3 实验验证与评估

3.1 JTAG认证安全性分析

3.2 密钥生成可靠性分析

3.3 架构性能评估

4 结束语