基于FPGA数字复接器设计

杨 湲

(西华师范大学电子信息工程学院 四川 南充 637009)

数字复接是提高通信效率常见手段之一,复接其本质是把时间分成若干相等的时隙,让各路信号在独立的各自对应的时隙上传输[1,2]。信号按字复接是较为普遍的方法,其特征是:每个时隙上传输8位码,便于数字分接器信号的提取[1-4]。由于各路复接信号到达复接器的时间、距离、相位不同,可能导致复接输出信号误差较大,而同步复接方式在一定程度上能降低误码率,因此本文采取同步按字复接的方法来完成四路信号的复接[5]。

1 电路结构

1.1 普通复接器

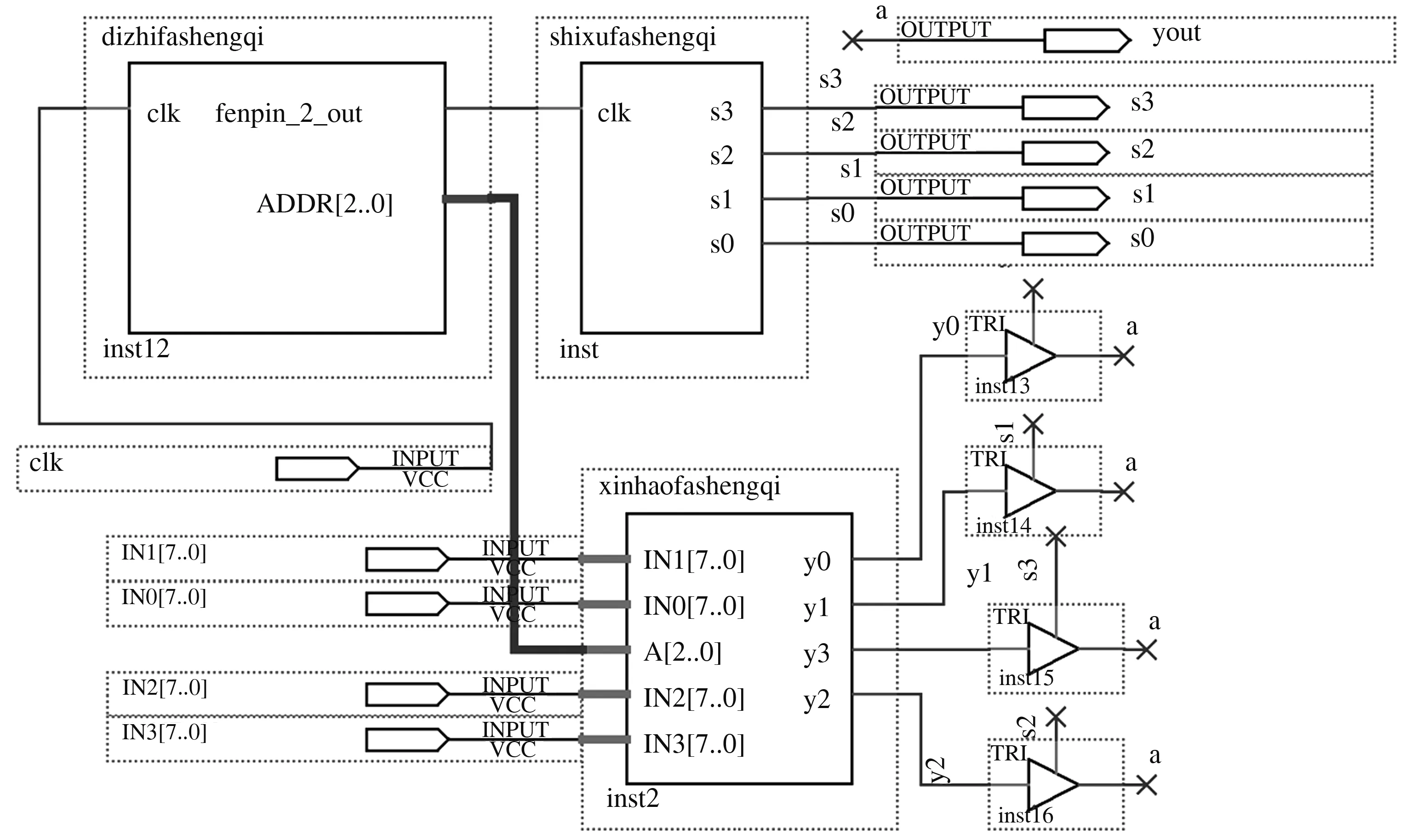

图1是普通复接器硬件电路,该电路由4部分组成,分别是地址发生器(dizhifashengqi),时序发生器(shixufashengqi),信号发生器(xinhaofashengqi)、以及输出电路部分[1-3]。地址发生器实际上是对时钟进行二分频、四分频、八分频。其二分频信号作为时序发生器的时钟输入,二分频、四分频、八分频作为信号发生器的地址输入。时序发生器在时钟的作用下,产生4路相位不同的时序信号,以此来控制输出端[6]。信号发生器在地址端的控制下,依次将四路并行信号串行输出。输出电路是由4个三态门构成,三态门在时序信号的作用下便实现了4路信号的复接,并从yout输出[7,8]。

1.2 第一步改进的复接器

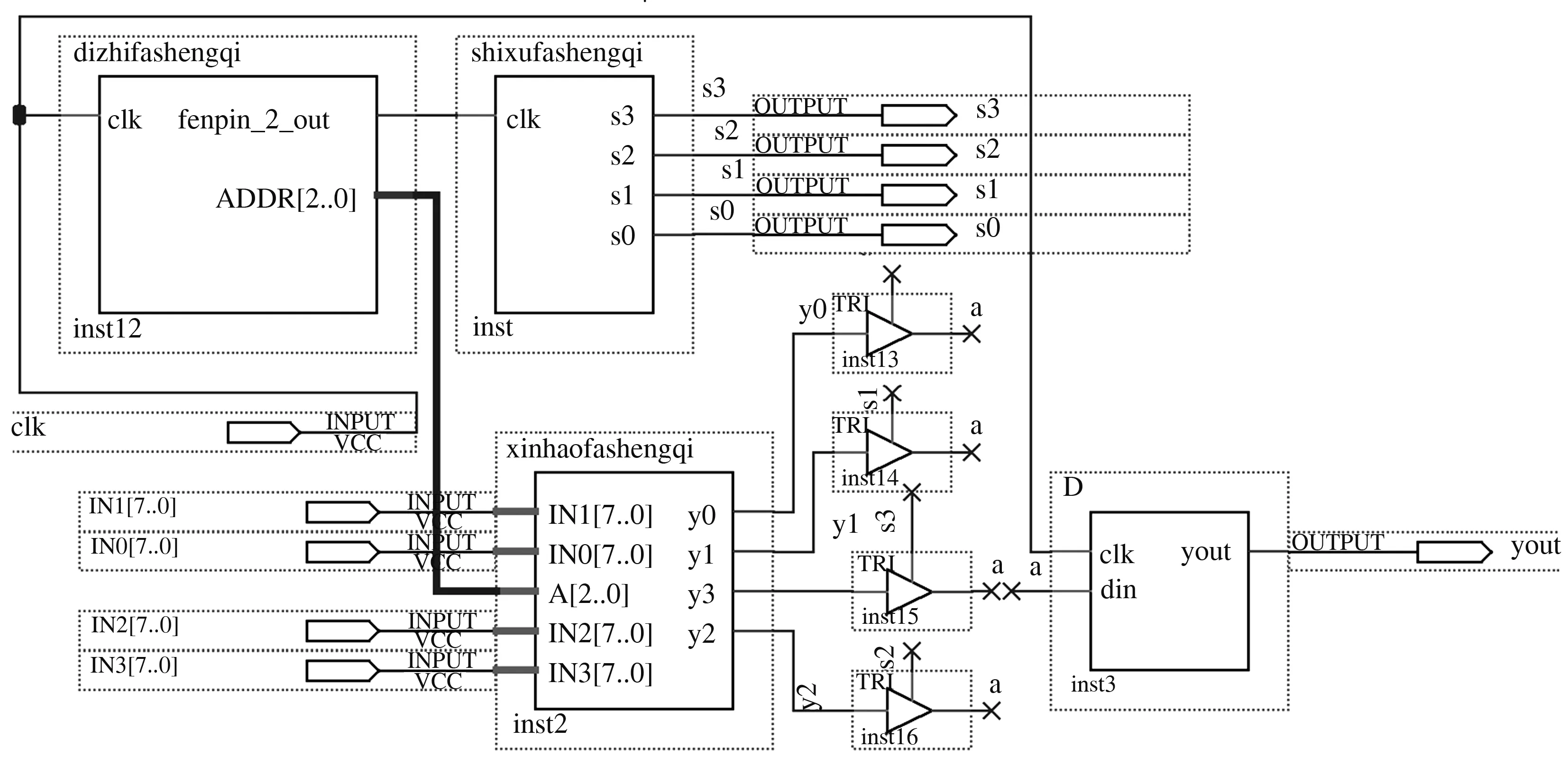

图2是第一步改进的硬件电路,该电路是在普通复接器的输出电路部分增加了一个D触发器,以此来减少由于逻辑竞争与冒险产生的毛刺[1-4]。

图1 普通复接器硬件电路

图2 第一步改进后的复接器硬件电路

1.3 第二步改进的复接器

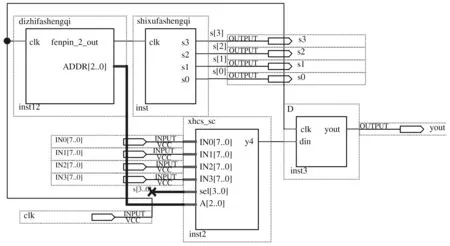

图3是第二步改进的硬件电路,第一步改进后的电路虽然可以减少毛刺,但是,由于增加了D触发器,导致输出延时增加,为了提高系统输出速率,第二步优化了信号发生器与输出部分的逻辑,即第一步改进的复接器中的信号发生器与输出电路部分由xhcs_sc代替,该模块在地址信号与时序信号的作用下先产生4路串行信号,然后将分时的4路信号从y4端输出[1-4]。

图3 第二步改进后的复接器硬件电路

2 仿真结果与资源占用

2.1 普通复接器

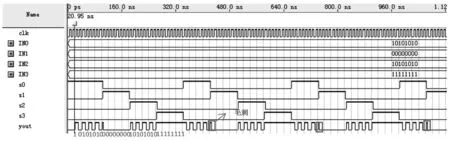

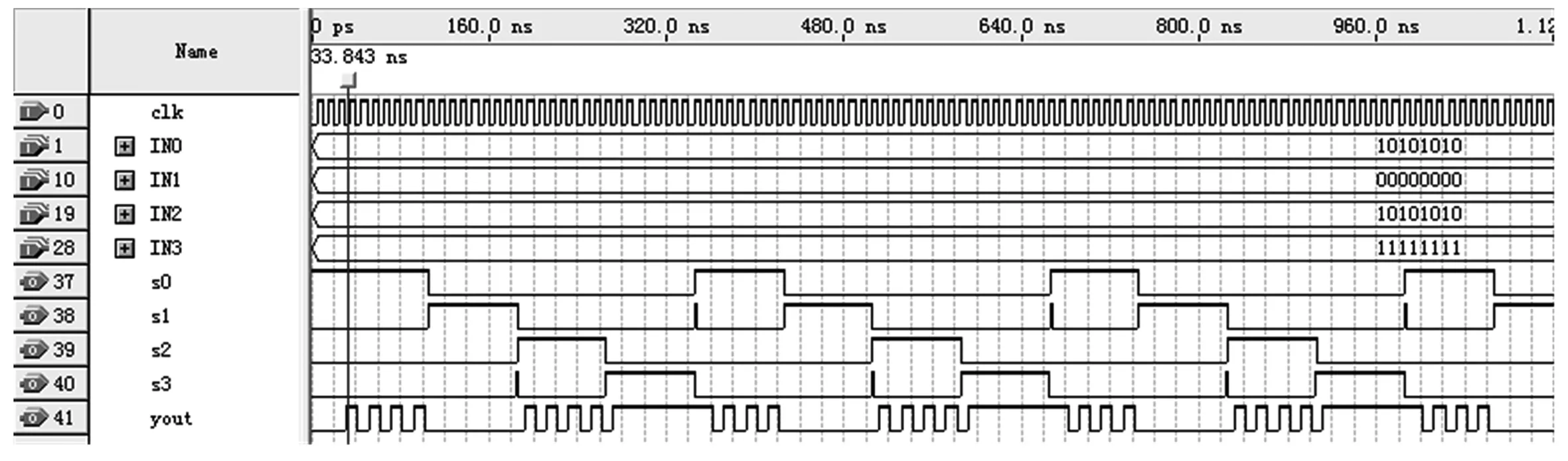

图4是普通复接器的仿真结果,clk为100 MHz时钟信号,IN0、IN1、IN2、IN3是4路输入的并行信号,s0、s1、s2、s3是产生的4路相位不同的时序信号,yout是输出的复接信号。从仿真结果看出,经过20.95 ns系统依次将4路并行信号复接在第一、二、三、四个时隙上输出,但由于器件之间的逻辑竞争冒险,导致复接信号存在些许毛刺。

从编译综合看出,普通复接器组合逻辑占用33个,时序逻辑占用15个。

2.2 第一步改进的复接器

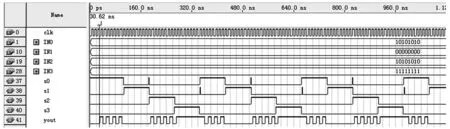

由于普通复接电路输出的毛刺可能会影响后续分接器的效率,所以去毛刺迫切需要。yout是第一步改进后的输出信号,从仿真图5看出,输出波形无毛刺,效果较好,但需经33.843 ns系统才依次将4路信号复接输出。

从编译综合看出,第一步改进后的复接器组合逻辑占用24个,时序逻辑占用15个。

图4 普通复接器仿真结果

图5 第一步改进后的复接器仿真结果

2.3 第二步改进的复接器

第一步改进后虽然资源占用较少、波形效果较好,但由于增加了D触发器导致输出延时增大,因此为了提高系统输出速率,对电路的逻辑结构进行了调整。图6是第二步改进后的仿真结果,从波形看,效果较好,无毛刺现象,并且只需30.62 ns信号便可复接输出。

从编译综合看出,第二步改进后的复接器组合逻辑占用26个,时序逻辑占用15个。

图6 第二步改进后的复接器仿真结果

3 结论

普通复接器,组合逻辑占用33个,时序逻辑占用15个,复接信号经过20.95 ns输出,波形存在毛刺。

第一步改进后的复接器,组合逻辑占用24个,时序逻辑占用15个,复接信号经过33.843 ns输出,波形无毛刺。

第二步改进后的复接器,组合逻辑占用26个,时序逻辑占用15个,复接信号经过30.62 ns输出,波形无毛刺。

普通复接器系统输出速率高,但资源占用较大,并且存在毛刺。第一步改进后的复接器,系统资源占用较少,无毛刺,但系统输出较慢。第二步改进后的复接器不论是系统输出速率、资源占用还是波形效果方面都较优。