基于 DDS 的微波频率源实现方案分析

摘要随着现代电子技术的飞速发展人们对微波频率源提出了更高的要求诸如频谱纯度、频率范围以及步进等要素都成为关注的重点其中相噪更是首当其冲地成为高性能频率源的重要标志之一文章从具体的需求角度出发对微波频率源的建设提出了对应的改进构想并针对相应的构想对相关相噪进行了估算

关键词微波;频率源;实现方案;相噪

中图法分类号:TN74文献标识码:A

Implementation scheme analysis of microwave frequency source based on DDS

ZHAO Jian

(The 13th Institute of China Electronics Technology Group Corporation,Shijiazhuang 050000,China)

Abstract: With the rapid development of modern electronic technology,people have put forwardhigher requirements for microwave frequency sources,and factors such as spectral purity,frequencyrange and stepping have become the focus of attention.Among them,phase noise is the first tobecome one of the important symbols of high-performance frequency sources.From the perspective ofspecific needs,this paper puts forward corresponding improvement ideas for the construction ofmicrowave frequency sources,and estimates the relative phase noise for the corresponding ideas.Key words : microwave,frequency source,implementation scheme,phase noise

微波频率源能够于多个参考频率中产生特定频率的信号源,广泛应用于各类电子系统之中,在民用和军用领域都十分常见,如广播电视、高速(轨道)交通以及飞行器测控、精准打击等领域。微波频率源自身的稳定性和准确性而直接成为影响对应工作体系性能的直接因素,因此一直以来都受到国家的重视。

1 DDS 合成频率源的特征

从技术层面看,微波频率源使用非线性有源器件以及无源电路等共同参与工作,能够将直流功率转变成为稳定精确的射频信号。通常可以将微波频率源分为自激振荡型微波频率源和合成型微波频率源,并且后者相对而言应用更为广泛,具有频率稳定性高以及相噪低等优点,且易于控制。但是,相对来说技术难度比较大,成本也尚未得到有效控制。从技术指标角度看,微波频率源的主要性能指标包括输出频率范围、频率分辨率、相噪、输出功率及波动、跳频能力、调制状态等,不同的应用环境会对指标的选择有不同的侧重。但是从整体上看,基本各个应用领域都会在一定程度上对噪声做出要求,因此本文同样从该领域展开分析,考察微波频率源的实现。

在此之前,首先对 DDS 频率合成技术进行必要的了解。DDS 频率合成技术,也就是常说的第三代技术[1] 。本质上,此技术以相位作为根本出发点而展开频率合成,因此能够产生出多样化频率和波形的信号,对于初始相位的控制也因此变得简单。整体而言,DDS 频率合成技术的特征首先表现在带宽方面,依据奈奎斯特采样定理可以确定,DDS 系统在理想状态之下,其输出频率可以达到时钟频率的一半水平。换言之,DDS 合成频率源的频率上限可以由时钟频率进行确定。并且在捷变频速度方面, DDS 系统同样具有显著优势。DDS 合成频率源本身属于开环系统,因此其转换时间依赖于低通滤波器的时延。随着时钟频率的不断提升,转换时间会因此缩短,这就决定了 DDS 系统的转换时间也会随之不断压缩。

就目前而言,DDS 系统的转换时间大多保持在 ns 级,捷变频速度在频率源领域可谓首屈一指。在步进方面,DDS 频率源能够实现超细分辨率,这主要是因为 DDS 系统的分辨率依赖于内部相位累加器的长度,并且满足Δfmin=整体而言,DDS 频率源基本可以满足当前社会的要求,其完全可以实现mHz乃至于μHz 数量级步进。DDS 合成频率源在相位连续方面同样具有优势,本质上看,其改变了相位增量,因此输出信号上不会出现有其他信号叠加的情况。而在相噪方面,DDS 系统的本质相当于实现了分频器功能,因此对应的相噪必然能够得到控制。DDS 频率源的相噪,甚至可以控制到与时钟噪声同一个量级的水平。

除此以外,DDS 频率源的缺点也不容忽视。首先,其工作速度会受到内部变换器和 ROM 的制约,这也成为直接关系到其工作频率的重要因素,直接将 DDS 系统的工作频率约束在几十 MHz 到几百 MHz 范围内。并且这种完全由数字结构来实现的系统,其输出信号杂散的问题必然比较突出。而且这一问题并无法通过相关的技术调整来进行控制和解决,其来源于数字结构自身的原理,属于此类频率源的固有不足。

2 DDS 频率源相噪的计算

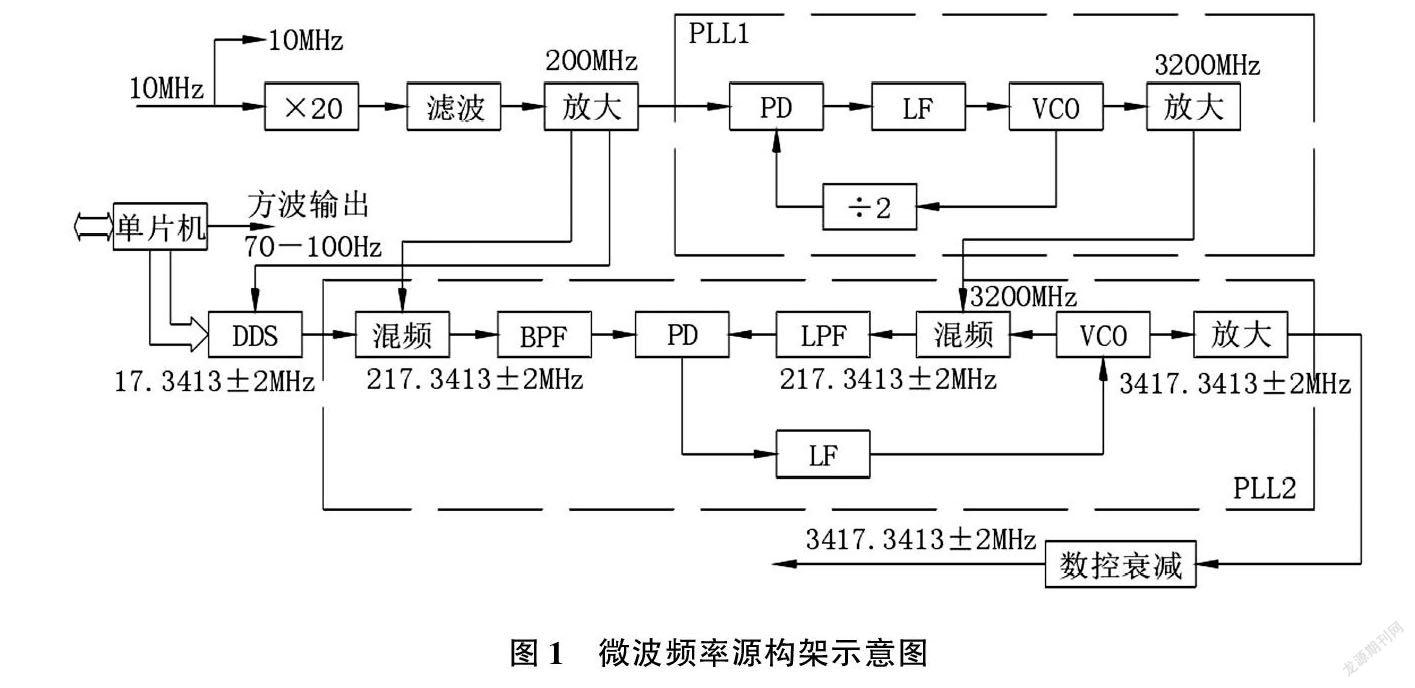

就目前的技术而言,单一的锁相环无法解决解决细频率分辨率与低相噪的矛盾,而单一的 DDS 又具有输出频率较低、杂散分量丰富的局限性,因此多考虑基于 DDS 小步进低相噪,并且结合 PLL 和混频、倍频等相关合成技术,来实现对于传统多环方案缺点的克服。对于分辨率要求比较高,如要求不高于0.1Hz 的情况,必须使用 DDS 产生对应的频率源,但是受到 DDS 的限制,如果直接将其转变到 S 或者更高频段,则必然会造成输出相噪和近载频杂散成倍增加。针对这一问题,可以考虑在 DDS 和混频跟踪锁相环技术之上展开混合式频率合成。具体而言,其微波頻率源应当包括五个功能模块,即参考倍频、本振环 PLL1, DDS、混频跟踪环 PLL2以及控制模块。具体结构参见图1 。

参考倍频模块主要用于实现对于10MHz 信号实现倍频、滤波以及放大处理,从而获取所需要的 200MHz 参考信号。放大之后的信号会有三个去向,其一去往本振环 PLL1作为输入功率使用,其二作为 DDS 的时钟信号,其三则是作为参与 DDS 混频的本振信号而进入到频跟踪环 PLL2中。本振环 PLL1的作用在于将从参考倍频模块中获取到的200MHz 参考信号锁相倍频到3200MHz 的功能,来将频谱转移到 S 频段,并且将产生的结果送到混频跟踪环 PLL2中,作为混频环的本振信号使用。DDS 模块可以说是微波频率源的核心,该模块接受来源于本振环 PLL1的放大信号,并且能够支持来源于单片机的控制。其能够实现0.1Hz 的频率步进,并且 DDS 输出信号与 200MHz 信號进行一次混频,而后将产出的上混频信号输入到最末一级的混频环中。混频跟踪环 PLL2的功能主要是对本振环 PLL1输出的3200MHz 信号展开进一步的混频,并且与 DDS 模块输出的上混频信号进行鉴相,最终产生对应的输出信号并且进行放大,实现数控衰减[2]。

对于该方案而言,其核心问题在于三个方面,即低相噪、低杂散以及小步进的实现。本文只针对相噪方面的问题进行考察,其他两个方面暂不多做考虑。

该频率源的噪声主要源于四个方面,即参考倍频模块、锁相环、环路滤波中的放大器以及分频器。如果设定对于频率源的相位噪声需要控制在-65dBc@1Hz 之内,则在理论上可以进行如下估算。

首先,10MHz 频标相位噪声,通常可以控制在不超过-120dBc@1Hz 范围之内,对于这一噪声的控制,主要可以通过选用稳定度和低相噪的 BVA 恒温晶振来实现。而对于参考源模块输出的相噪而言,因为去输出频率为200MHz,因此相噪恶化20lg20≈26dB,则对于200MHz 信号,其相噪大约为-94dBc@1Hz 。这两个方面的噪声,都是比较容易确定和估计的。而对于本振环( PLL1)输出相噪、DDS 方面的输出相噪以及混频跟踪环( PLL2)的输出相噪,则需要另外进行详细估算。

对于本振环(PLL1)而言,如果用hittite公司推出的数字鉴相器予以实现,选择 HMC440QS16G 的时候,则其在偏离载波1kHz 处的相噪基底大约为⁃230dBc @1Hz ,估计1Hz 与1kHz 处的相噪基底基本一致,因此这个环节的相噪主要来源于鉴相器基底相噪以及参考信号相噪。

于鉴相器而言,其频率如果为200MHz ,则其所产生的相噪见式(1):

式(1)中,Fc 为鉴相频率,N 为倍频次数。则进一步可以计算出结果见式(2):

对应的,参考信号所产生的相噪影响计算参见式(3):

式(3)右侧第一项为参考信号的相位噪声,R 为分频次数,则可以得到如式(4):

综上,输出信号的相位噪声,就应当是上述两个方面的叠加,参见式(5):

进一步将前述计算所得代入,可以确定 LPLL1(f1Hz )≈-69.9dBc/Hz 。由此可以看出,在这个领域之中,参考信号的影响力占据了决定性地位,而鉴相器基地相噪恶化影响则基本可以忽略。

对于 DDS 输出的相噪估算,首先需要从 DDS 的芯片开始。在相关领域中,ADI 公司的 AD9954在应用中比较常见,相关资料显示,当输出为17MHz 的时候,其相噪基底大约保持在 L′1(f)=-115dBc/Hz 水平,对应的参考信号相位噪声贡献见式(6):

进一步依据线性叠加公式可以确定,DDS 输出相噪约为 LDDS (f1Hz )=-112dBc/Hz 。因此,当 DDS 和200MHz 信号进行混频之后,一混输出的相噪主要受到参考信号相噪的影响[3]。

对于混频跟踪环( PLL2)而言,其本质上的工作原理与本振环(PLL1)类似,鉴相器采用hittite公司产品,型号为 HMC44OQS16G,鉴相频率为217MHz ,则鉴相器基底相噪对于输出信号相噪的影响计算参见式(7):

而与之对应的参考信号对于输出相噪的影响见式(8):

同样依据线性叠加公式可以确定,混频跟踪环的输出信号相噪大约为 LPLL2(f1Hz )=-70.1dBc/Hz。

综上所述,该系统获取到的最终输出信号的相噪可以用式(9)进行表示:

也就是说,该频率源构建方案在1Hz 处的相噪恶化主要集聚在对频标10MHz 相噪恶化方面,其他相关环节的影响相对而言有限,因此该结构相噪能够达标。

3 结论

在构建一个微波频率源时,相噪是首要考虑因素。虽然相噪并不是唯一决定因素(除此以外诸如低杂散以及小步进等同样需要有所满足),但是相噪仍然是经常被列为首位要素,是关系到频率源能否投入应用的关键。当然,杂散抑制以及频率分辨率也是需要加强分析的重点。在当前时代背景之下,微波频率源的构建以及其性能的优化,关系到多个方面应用,必须谨慎对待、不断改进,从而满足社会发展的需要。

参考文献:

[1] 李志云,李英,李建波.移动社交网络中基于用户动态需求的 D2D 数据分流方法[ J].青岛大学学报(自然科学版), 2021,34(1):1⁃6+12.

[2] 丁海春,吴海涛,苏卫国.基于 DDS 的多种调制方式频率源的设计[J].电子技术,2020,49(3):192⁃194.

[3] 蓝友.宽带小步进频率源研制[ D].成都:电子科技大学:2020.

作者简介:

赵健(1994—) ,本科,研究方向:微波射频频率源。