基于三维集成的小型化Ku 波段收发组件

刘昊东,吴洪江,余小辉,马战刚

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

0 引言

微波组件是雷达和通信系统中的重要硬件支撑部分,承担着信号的放大、混频、调制和幅相控制功能。为了满足性能更加强大的雷达和通信系统的需求,设备前端所使用的天线阵列规模越来越大,所需要的信号也越来越复杂,对于微波组件的技术指标来说,就需要在同样甚至更小的体积下有着更多的通道数、更高的通道间一致性和隔离度、更好的电磁兼容和更低的功耗,同时还要保证组件在极端环境下的可靠性。因此,微波组件正在向着小型化、轻量化、高工作频率、多功能、高可靠性和低成本等方向发展[1-2]。然而,目前传统的微波多芯片模块和组件已经渐渐无法满足小体积、低功耗的需求。

本文介绍了一种以硅基三维集成器件为基础的三维集成微波组件,采用盒体单层开腔,电源和信号集成至一整块多层混压PCB 板的形式[3-4],将80%的射频和中频芯片、器件集成在硅基三维集成器件中,采用BGA安装形式,晶圆级键合封装,顶层还可以表贴阻容、电桥等无源器件;再将硅基模块、中频LC 滤波器、温补衰减器、π 型衰减器和稳压电路、控制电路等所需要的器件表贴在PCB 板上形成完整的收发链路和控制电路,最终研制出的微波组件相对于其原型接收机增加了发射功能和一路多功能通道的情况下,整体体积降低至原接收机的一半,实际使用体积仅有原接收机的1/3;组件采用单层开腔、多层混压PCB 板、通道功能硅基模块化、整体装配自动化的设计思路,使多功能组件在保证大批量生产的一致性的同时大幅降低所需要的装配时间,提高组件大批量生产效率,降低人力成本和手工装配所带来的不稳定性。

1 原理设计

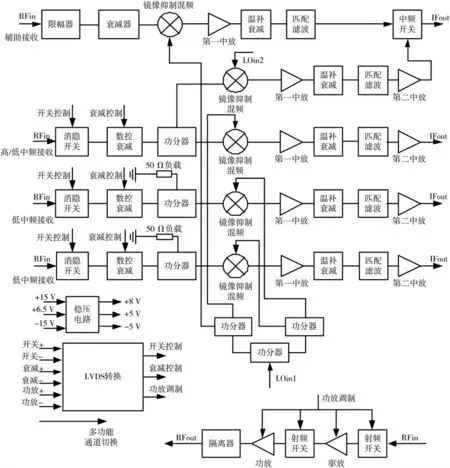

收发组件的原理框图如图1 所示。收发组件主要分为发射部分、接收部分和电源及驱动电路部分[5-6]:

图1 收发组件原理框图

发射部分包括一路发射通道,对发射激励信号进行调制和功率放大,可输出28.5 dBm±1.5 dB 的脉冲发射信号。

接收部分输入包括两路差信号接收通道,一路低中频和接收通道,一路高中频和接收通道和一路辅助校准通道;输出包括两路差信号,一路低中频和信号,一路高中频和信号和一路辅助接收信号。其中,高低中频的和信号接收通道共用一个输入端口,辅助接收信号和高中频和信号由切换开关控制共用一个输出端口,主要功能为对从天线输入的三路射频信号进行变频、滤波和放大,可为微弱信号提供30 dB 接收增益,且通过消隐开关和数控衰减器组合实现接收信号的增益、衰减和关断的状态切换,确保接收通道在接收大信号时仍能正常工作,且不会因发射通道的高功率信号泄漏损坏。

电源及驱动电路包括稳压电路和低电压差分信号(Low Voltage Differential Signaling,LVDS)电平转换电路,为组件电路提供所需的稳定工作电压和控制信号。

2 组件电路及结构设计

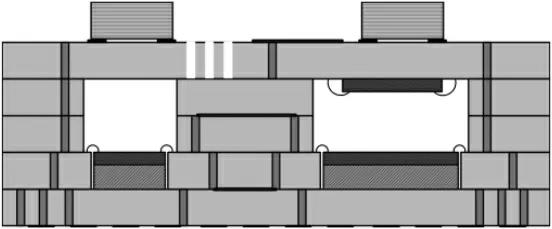

2.1 硅基三维集成模块设计

硅基三维集成模块以硅晶圆为原材料,采用微机电系统(Micro-Electro-Mechanical System,MEMS)工艺制作多层基板,在基板上制作各种集成无源器件,并将GaAs、GaN、互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)等材料制成的芯片以烧结、粘接、键合、倒装焊等微组装工艺填埋在基板内部或表面而制成,在实现相同功能和指标的情况下可以大幅降低组件体积和信号传输损耗[7]。硅基三维集成模块的剖面结构图如图2 所示。

图2 硅基三维集成模块剖面结构图

由于硅基三维集成模块在射频下的优异性能和高一致性,本次将收发链路中的大部分器件均集成进硅基三维集成模块中,将温补衰减器、LC 滤波器、隔离器等体积较大的器件采用独立贴装的方式进行装配。本次硅基三维集成模块采用5 层硅基板堆叠,第一层硅基下表面制作镍金焊盘,用于BGA 植球;硅基采用干法刻蚀芯片掩埋腔体,采用微组装工艺将单片微波集成电路(Monolithic Microwave Integrated Circuit,MMIC)装入芯片腔体中,并通过金丝键合实现互连;顶面贴装元器件提高集成度。

2.2 单元电路设计

2.2.1 发射通道设计

发射通道要求发射输出信号为调幅脉冲信号,具有100 kHz 和500 kHz 两种重复频率,输入功率-1~4 dBm,输出功率在环境温度下全频带内要求28.5 dBm±1.5 dBm,预调制深度大于80 dBc,因此整体电路分为驱放硅基模块和功放硅基模块,驱放硅基模块集成单刀单掷开关、衰减器、驱动放大器和电源调制芯片等,功放硅基模块集成单刀单掷开关、功率放大器、可编程负压稳压芯片、电源调制芯片、滤波电容、调压电阻等;功放芯片选用一款宽带GaAs 放大器,小信号增益28 dB,饱和输出功率30 dBm,动态漏极电流小于0.6 A,饱和输出以保证带内平坦度和输出功率要求。

输出端贴装隔离器以优化端口驻波、增加端口反向隔离度。

2.2.2 接收通道设计

接收通道包括的主要器件包括硅基模块、LC 滤波器、温补衰减器等。硅基模块按照通道功能分为和差通道硅基模块、辅助/高中频和通道硅基模块和中频放大硅基模块。

和差通道硅基模块首先包括由一对单刀双掷开关、限幅器、低噪放、数控衰减器组成的消隐开关电路,实现导通(增益30 dB±2 dB)、衰减(衰减量25±3 dB)、关断(通断比51 dB±3 dB)三态控制;由于低中频和通道需要输出一路射频信号给高中频和通道进行混频,消隐开关后接功分器芯片,差通道不需要功分输出时,将另一路的输出端口以50 Ω 负载接地即可;功分器后接由镜像抑制混频器和90°电桥组成的镜像抑制混频电路,可提供20 dB 的镜像抑制;电桥输出混频后的中频信号,后接一中频放大器,提供中频增益。90°电桥和中频放大器外围电路皆为表贴器件,集成在硅基模块最顶层。

辅助/高中频和通道硅基模块与和差通道硅基模块类似,在其基础上去掉了消隐开关电路,输入端只保留限幅器。

中频放大硅基模块集成中频放大器和其外围电路,位于接收链路的最后端,保证信号经过温补衰减器和LC 滤波器后中频输出功率满足要求。

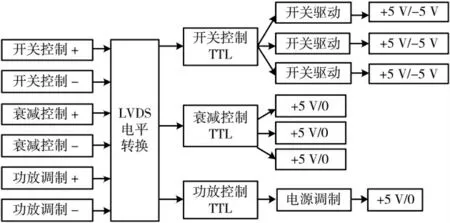

2.2.3 电源及驱动电路设计

外部电源输入组件后,通过线性稳压电路进行稳压后再为有源器件提供电源,提高电源电路的抗干扰能力。

外部输入的控制信号为LVDS 差分信号,组件内部使用晶体管-晶体管逻辑电平(Transistor-Transistor Logic,TTL)进行开关、衰减、功放调制等控制功能,因此需通过LVDS 接收电平转换器件将六路LVDS 信号转换为三路TTL 信号。为了避免信号通过控制电路产生串扰,和差通道分别采用独立的开关驱动器以提高通道间隔离度。驱动电路原理框图如图3 所示。

图3 驱动电路原理框图

2.2.4 本振电路设计

本振信号通过带状线进行传输,通过威尔金森功分器形式,采用二功分器,进行两次信号一分二,从而实现了本振的四路等分。为满足混频器的本振输入功率要求,将本振信号先功分后再放大,输入到和差三路接收通道及辅助和路通道,保证混频器的本振功率需求。

本振输入功率为8~12 dBm,经过两级功分器后,加上微带线的损耗,每路输出功率约为0 dBm,放大器增益为25 dB,输出1 dB 压缩点14 dBm,放大器处于深饱和状态,不利于本振链路的谐杂波抑制,故在放大器之前增加约10 dB 的衰减,同时可起到提高路间隔离的作用。此时,本振放大器可输出功率14 dBm,可满足混频器的正常工作需求。

2.3 射频传输结构设计

2.3.1 PCB 基板及走线设计

本次组件采用单板设计,双层射频基板与单层低频基板混压,走线共六层:前四层为两层双面射频基板压合,表层射频微波信号采用共面波导形式进行传输,并在输入端口增加λ/4 短路线用于中频信号隔离,中层组成带状线结构进行本振信号传输,且做埋阻以提高威尔金森功分器隔离度;后两层为低频基板;六层布线采用信号-屏蔽地的交错结构,信号层均可用于电源和低频控制信号传输。多层板采用包边处理,以增加电路板强度,且可以增强电路板接地效果[8]。板上电气过孔均树脂塞孔表面覆铜,保证焊盘平整度的同时,防止通孔溢锡污染焊盘,另设计有若干孔径0.3 mm 的非金属化透气孔,在烧焊电路板时可以降低电路板空洞率。

2.3.2 波导-微带过渡结构设计

接收部分的和差射频输入信号均采用压缩波导进行传输,而组件内部使用射频基板与微波基板混压的多层PCB 板作为电路基板,采用共面波导形式进行射频信号传输,以降低射频信号在混压板上的损耗。因此,射频信号在进入组件时,需要实现两种传输形式间的转换。由于转换结构位于接收通道最前端,因此其插入损耗和回波损耗对端口的匹配效果和通道的噪声系数有极大的影响[9]。

常见的波导过渡形式主要有以下三种结构:(1)波导-脊波导过渡;(2)波导-鳍线过渡;(3)波导-微带探针过渡[10]。然而以上三种结构由于加工精度要求较高,装配较为困难,且在恶劣的使用环境下难以保证传输性能的稳定,因此本次设计采用较为稳定的波导-同轴-共面波导过渡形式。

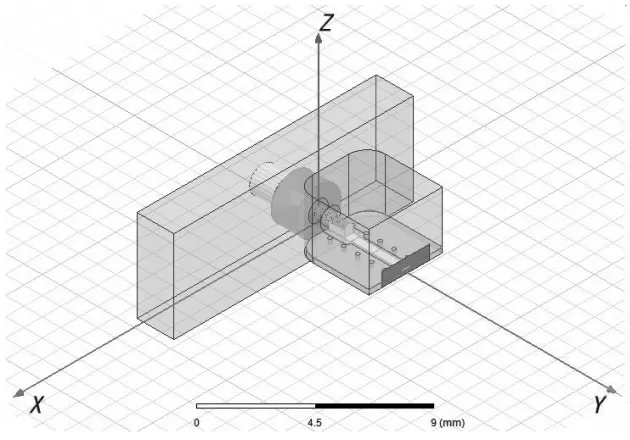

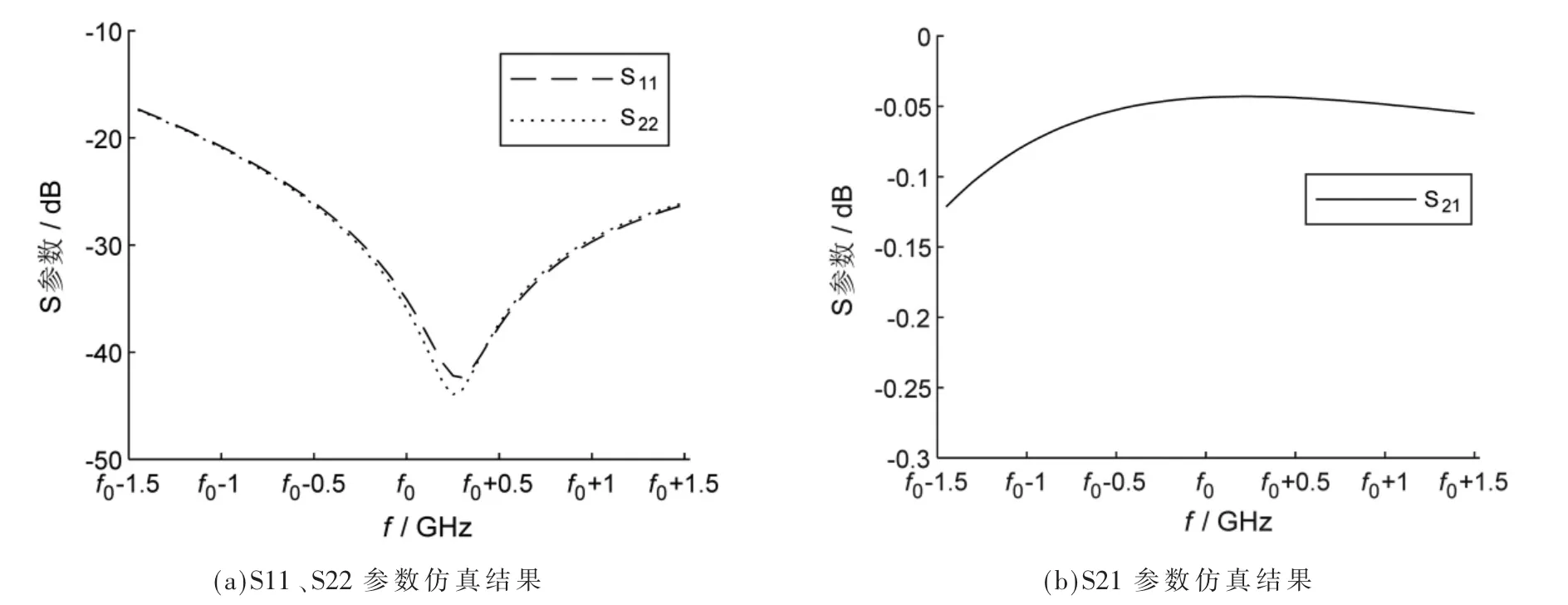

设计中对过渡模型进行了仿真,建模如图4 所示,最终仿真曲线如图5 所示,可见在工作频带内,插入损耗小于0.15 dB,回波损耗小于-15 dB,满足组件使用要求。

图4 波导-同轴-共面波导过渡结构仿真模型

图5 波导-同轴-共面波导过渡结构仿真结果

在实际生产时,需要考虑盒体的加工方式和绝缘子的安装方式。本次设计采用从波导顶部向下打孔的方式加工出绝缘子的安装孔,装配时通过波导顶部的孔装入绝缘子;另设计了波导堵盖,采用合适的焊料烧焊在盒体上以保证波导结构完整。

2.3.3 垂直互连设计

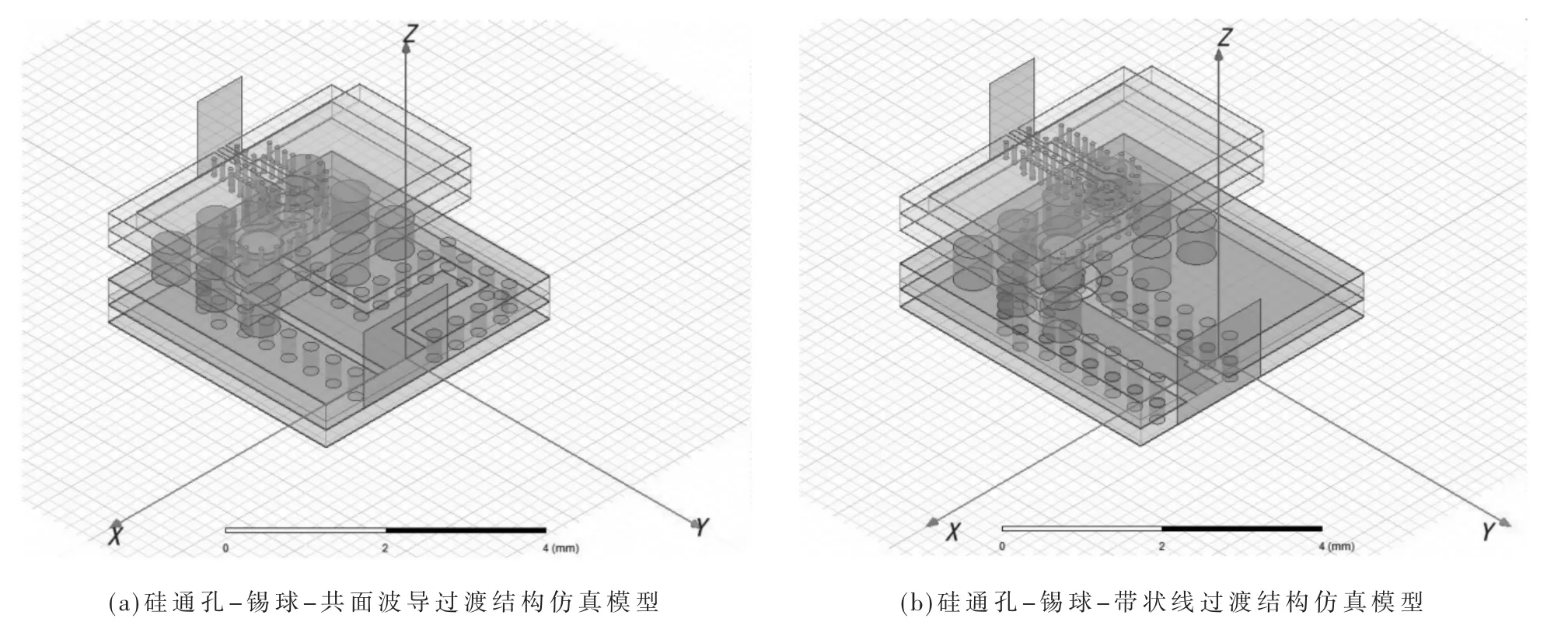

由于硅基集成器件采用BGA 植球工艺进行装配,为了降低微波信号在硅通孔-锡球-共面波导过渡结构和硅通孔-锡球-带状线过渡结构中传输时产生的损耗和串扰,需要对信号的垂直互连结构进行仿真设计。

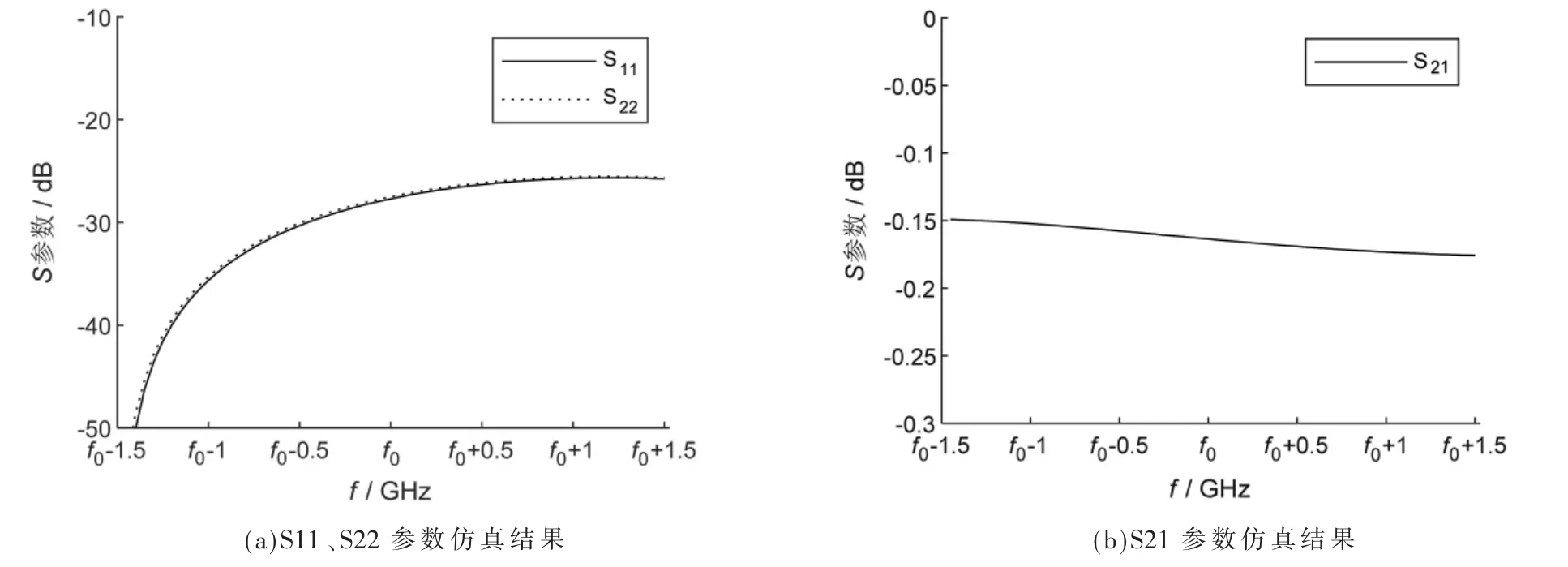

图6(a)为硅通孔-锡球-共面波导过渡结构设计,图6(b)为硅通孔-锡球-带状线过渡结构设计。信号自硅基模块底部焊盘输出后,均通过直径400 μm 的锡球与电路板焊盘进行连接,球心间距设为800 μm;硅基模块和电路板内的传输线两侧均铺设接地面,通过接地面与焊球间的电容效应拓宽频带;垂直通孔均采用类同轴结构,在信号通孔周围以通孔中心为圆心等半径放置接地孔作为屏蔽孔,不仅可以起到对电磁场的束缚和屏蔽作用,而且可以抑制由电磁场不连续性激发的寄生高次模[11-13]。同样,在BGA 的信号球周围等间距设置屏蔽球,可以实现物理支撑和信号屏蔽作用,降低外部信号串扰,提高通道间隔离度。图7 和图8 为两种互连结构工作频带内仿真结果。

图6 信号的垂直互连结构仿真模型

图7 硅通孔-锡球-共面波导垂直互连结构仿真结果

图8 硅通孔-锡球-带状线垂直互连结构仿真结果

2.4 结构设计

组件盒体采用防锈铝材料,外表面导电氧化,内部局部镀金;对外信号接口均为密封式接头,除和差通道波导输入端口为压缩波导形式外,剩余射频和中频端口均为SMA 接头,电源和控制信号采用J30J 插头连接。为了保证通道间隔离度,在电路板表面紧固活动隔墙以实现腔体隔离。

3 实物装配与测试

设计完成后,按照要求对结构件和电路板进行了加工,并根据组件内各种元器件的特点按照成熟温度梯度的加工工艺设计了合适的工艺流程:

(1)将电路板烧焊在盒体上;

(2)将硅基模块、稳压器、绝缘子、滤波器、隔离器、阻容等各种表面贴装器件贴装到电路板和盒体上;

(3)用低温焊料贴装硅基模块上的90°电桥、阻容,并烧焊波导堵盖;

(4)紧固装配活动隔墙;

(5)将低频插排的导线手工焊接至电路板;

(6)将隔离器的输入输出端口采用150 μm 金带楔焊键合至电路板。

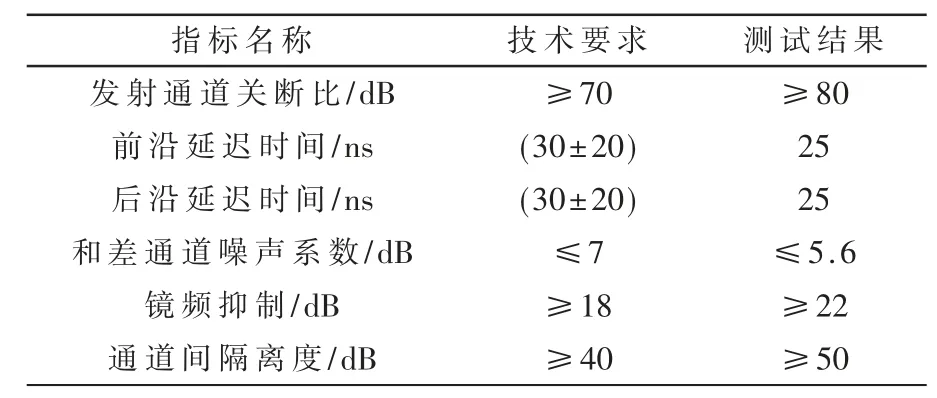

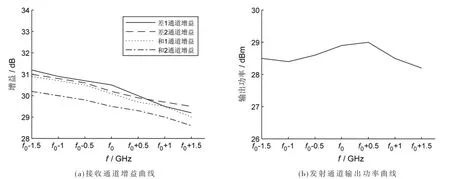

装配完成后,对其进行了测试,各接收通道增益曲线如图9(a)所示,发射通道输出功率曲线如图9(b)所示,其余主要指标结果如表1 所示。

表1 其余主要指标测试结果

图9 组件实物测试曲线

由测试可知,在工作频带内,接收链路增益和发射输出功率均满足指标要求,发射通道关断比≥90 dB,脉冲信号前后沿延迟时间为25 ns,和差接收通道噪声系数≤5.6 dB,镜频抑制≥22 dB,通道间隔离度≥50 dB,验证了组件设计的可行性。图9(a)可见和2 通道增益相比其他三路增益稍低,这是由于和2 通路包含两个硅基三维集成模块,互连时增加了两次射频信号垂直传输和一段带状线导致的,可以通过调整硅基模块内部固定衰减器或外部中频π 型衰减器来调整增益。在设计时为了满足外形要求,实际使用的体积仅占整体电路板的3/5,若按空间利用率最高进行设计,可以将体积降低至目前的1/2。

4 结论

本文基于硅基三维集成器件、PCB 混压工艺、BGA堆叠和各种过渡结构仿真设计,设计并实现了一款Ku波段小型化三维集成收发组件,并给出了实测结果。组件通过各种三维集成小型化技术,在减小整体组件体积的同时,大幅降低了设计、生产和调试难度,提高了产品的可生产性和一致性。硅基三维集成器件的高精度光刻工艺使其实际应用频率可以达到100 GHz,然而,对于Ka 波段或以上的频率来说,多层混压PCB 的过孔加工精度难以保证;同时,由于硅基工艺和BGA 工艺的散热能力有限,难以应用于输出功率较大的发射链路。因此,本次三维集成组件的设计思路更适用于输出功率较低的微波组件,在应用于毫米波频段时,需要尽量缩短在PCB 上的传输距离,重点关注垂直互连结构的设计。综上所述,应用硅基器件的三维集成组件设计方法在T/R组件、毫米波通信和探测、宽带收发组件等领域均具有一定优势,对于实际工程中多功能微波组件的小型化和批量化生产有一定的借鉴意义。