综合电子系统重构时间分析方法研究

郑小鹏,王小辉,陈春燕

(中国运载火箭技术研究院研究发展部,北京 100076)

0 引言

综合电子系统重构是指在系统资源或运行环境故障影响下,为保障系统功能和性能正常,重新配置系统的软硬件资源的过程。综合电子系统逻辑映射具有多样性和不确定性[1],如何在保证系统正常重构情况下,在满足系统的可靠性和安全性要求下,提高系统的资源利用率和架构灵活性,已成为综合电子系统的重要研究方面。

目前,对综合电子系统重构的研究主要包含系统重构配置、重构机制、重构模型的建立与优化、重构蓝图的设计与生成等[2-4]。Chu[5]等提出一种在考虑功能冗余要求的情况下优化综合电子系统配置方案的方法,针对具有功能冗余要求的通用综合电子系统,给出了配置方案模型及其相关的可调度性和可靠性约束。Fontoura[6]等提出通过重构状态空间的转换,将增强AADL 规范的故障模型与重构逻辑相结合,来表示容错能力。罗庆[7]等提出一种基于改进Q 学习的重构蓝图生成方法,综合考虑重构影响、重构时间、重构降级以及负载均衡等多优化目标。综上所述,国内外目前很少对于综合电子系统重构时间分析的研究,求解综合电子系统重构时间的方法大多来自仿真实验,这使得综合电子系统重构的可靠性分析面临着安全隐患。

本文通过对综合电子系统、系统重构和重构时间进行建模,依据对综合电子系统架构、重构策略和重构过程的研究,搭建综合电子系统可重构平台,基于理论基础和重构验证平台对重构时间进行分析和验证。

1 综合电子系统建模分析

根据综合电子系统的组成和特点,对综合电子系统软硬件进行建模,描述在系统硬件上的软件的配置模型,分析故障触发下的系统重构,建立重构时间模型,设计应用迁移优化算法。

1.1 综合电子系统模型

综合电子系统由系统硬件和系统软件组成。为实现可重构综合电子系统,在系统上搭载多个处理器,实现多核心并行处理机制。

1.1.1 系统硬件模型

综合电子系统的核心组件包括处理器、存储器、总线和外围设备等。对系统中的处理器和总线建模,令处理器为C,总线为B,系统内核心硬件集合表示为:

处理器集合表示为:

每个处理器包含多个核心,处理器核心集合表示为:

系统总线是处理器间数据传输的通道,主要包含总线宽度和传输带宽,表示为:

1.1.2 系统软件模型

综合电子系统包含一系列软件应用,表示为:

相关属性表示为:

式中,Acmd代表软件可执行程序大小,Adata代表软件运行时数据所需存储空间,Areq代表软件优先级。

为保证软件正常运行,将软件部署在处理器核心上,部署关系表示为:

系统配置是软硬件间建立关系的映射,表示为:

其中,ACi表示应用Appi的部署情况,SCi表示系统的配置。

1.2 系统重构模型

综合电子系统的故障类型主要有处理器故障和处理器核心故障,处理器Ci故障表示为Fi,处理器Ci的核心CiPj故障表示为,系统故障定义为Fij:

综合电子系统重构迁移模型表示为系统在故障触发下从一个配置运行状态迁移到新的配置运行状态,定义为:

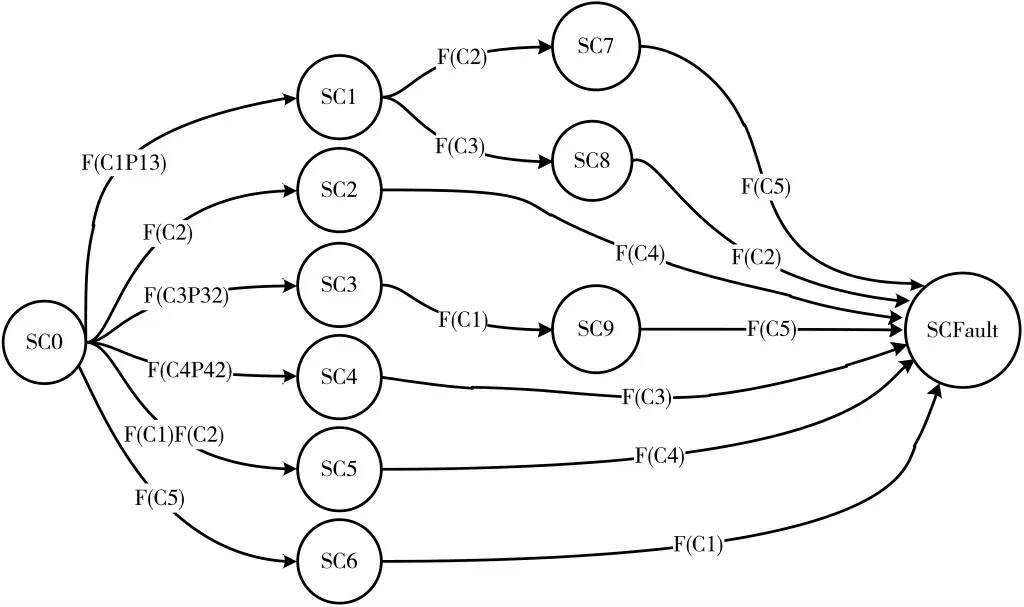

其中RCi代表系统重构蓝图,SCj表示系统在故障发生前的运行状态,SCk表示在故障发生后系统进入的状态。当系统在状态SCj下发生不可恢复的故障,进入到故障状态SCfault,图1 表示系统10 种运行状态对应的16 种重构蓝图的状态迁移图。

图1 系统迁移图

1.3 重构时间模型

若处理器内某个核心发生故障,可以由其他核心承担故障核心应用的运行,核心间应用迁移相对简单,包含应用撤销和应用绑定,核间重构时间模型表示为:

其中,t(AR)表示应用撤销需要的时间,t(AB)表示应用绑定需要的时间。

若系统内某处理器发生故障,需要将该处理器上部署的应用迁移到其他处理器上,在迁移过程中产生应用撤销、应用加载、应用绑定及状态同步等动作。处理器间重构时间模型表示为:

其中,t(AL)表示故障应用重新加载需要的时间,t(AD)表示故障应用恢复需要的时间。

系统重构包含了核间重构和处理器间重构,其重构时间的长短直接由迁移过程规划决定,为了减少迁移产生时间,不同处理器间通常采用并行迁移方式。执行优化算法会产生两个集合,一个是可并行迁移的应用Aen,另一个是只能单独迁移的应用Adis。其算法步骤如下:

(1)获得需要迁移的应用列表;

(2)依据并行迁移属性对应用分类,并放入集合和集合中;

(3)对于集合,依据硬件资源约束将同时迁移的应用划分为一组,最终将分为若干可并行迁移的应用组,每一个应用组表示为:

(4)探索最小迁移策略:验证每个可并行迁移应用组的可行性,并进行调整;

(5)只能单独迁移的应用按顺序执行,得到最终优化后的最短时延迁移策略最优解集:

最优解集中方括号内表示可并行迁移应用,最后的单独应用表示顺序迁移应用。

2 综合电子系统重构验证平台

为验证系统重构过程对系统正常运行的影响,本文搭建了综合电子系统重构验证平台,通过模拟系统运行中产生的故障,计算系统重构消耗的时间,分析重构过程的可靠性和安全性。

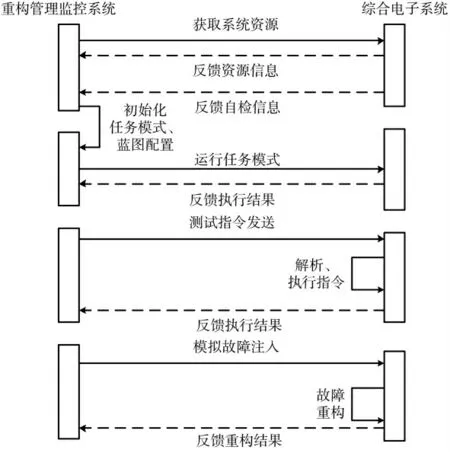

系统的总体架构主要包含综合电子系统和重构管理监控系统,验证平台执行流程主要由两系统间指令和数据的交互产生,如图2 所示。

图2 执行总体流程

综合电子系统重构验证平台执行流程如下:

(1)综合电子系统首先对软硬件资源进行虚拟化管理,然后向重构管理监控系统资源信息和自检信息。

(2)通过系统间的通信来配置任务模式蓝图,并将任务执行结果反馈给重构管理监控系统。

(3)综合电子系统接收重构管理监控系统的测试指令并对其进行解析和执行,将执行结果反馈给重构管理系统。

(4)重构管理监控系统通过故障模拟,将故障通过指令注入综合电子系统,综合电子系统执行重构恢复正常状态后,将系统状态反馈给重构管理监控系统。

3 实验验证分析

本文通过综合电子系统重构验证平台对综合电子系统重构时间进行实验验证。通过计算重构过程消耗的时间、重构蓝图的部署来验证重构过程的有效性和正确性。

3.1 实验环境

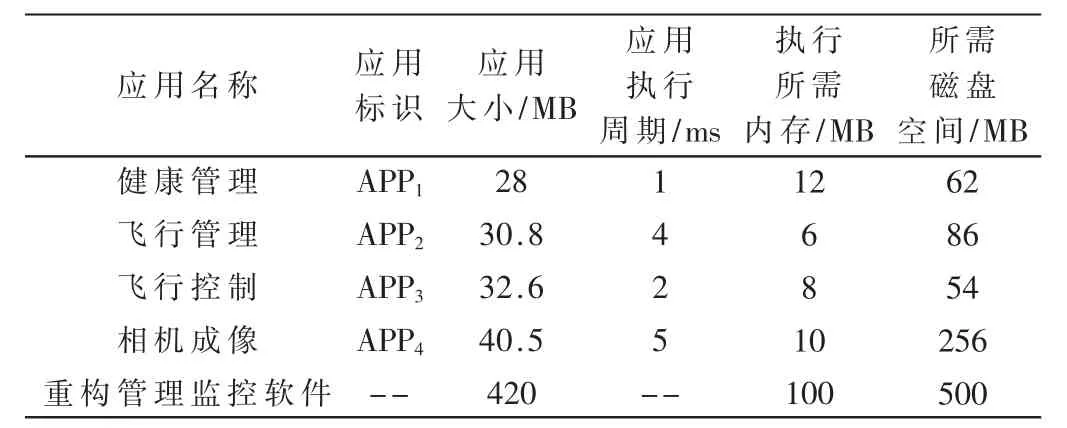

综合电子系统重构验证平台软件应用相关属性如表1 所示。综合电子系统应用的初始配置如表2 所示。

表1 平台软件属性

表2 应用初始部署

3.2 实验过程设计

向综合电子系统注入三种类型的故障进行重构时间的分析和验证,分别是处理器单核心故障、处理器故障和多级故障。本文重构时间验证基于处理器A 作为主处理器,处理器B 作为备用处理器,向综合电子系统处理器A 中注入核心1 故障、核心2 故障和处理器故障并分别进行实验验证和数据分析。对每个注入综合电子系统的故障都使用基于强化学习的智能重构[8]方法生成对应的重构蓝图。

3.3 重构时间分析验证

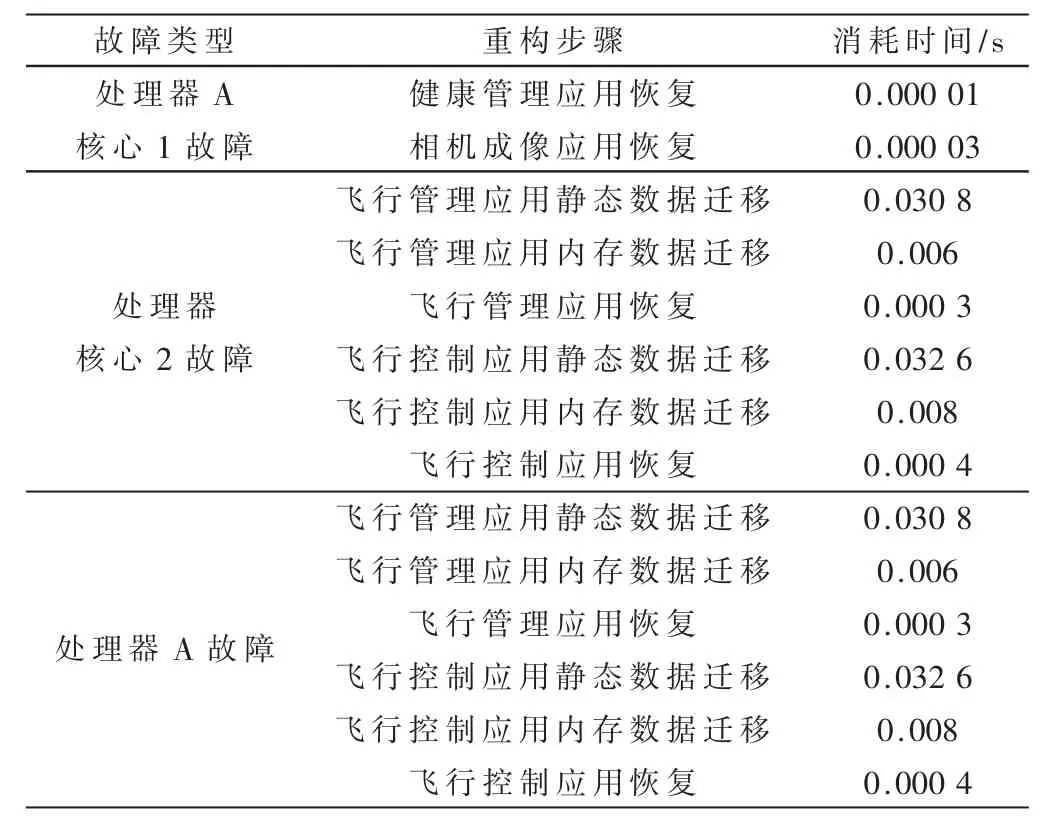

当发生处理器A 核心1 故障,需要对部署在核心1上的应用进行迁移,由于核心2 可以承担故障应用的运行,只需进行核心间重构,将核心1 上的应用迁移到核心2 即可;当发生处理器核心2 故障时,需要对部署在核心2 上的软件进行迁移重构;当处理器A 发生故障时,需要对处理器A 上部署的所有应用进行重新部署。迁移过程消耗的时间理论值如表3 所示。

表3 重构迁移过程理论消耗时间值分析

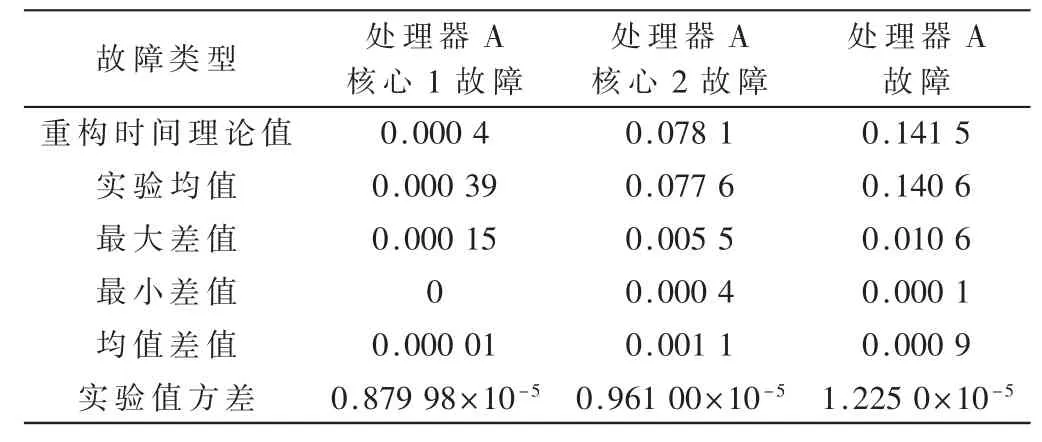

综合电子系统重构验证平台对3 种故障分别进行100 故障模拟,三种故障实验相关数据如表4 所示。

表4 实验数据汇总

由表4 可知,三种故障类型的实验值方差都很小,说明实验产生的重构时间比较稳定,重构蓝图的执行效果较好。

处理器A 的核心1 故障比核心2 故障导致的重构时间显著要小,其原因是核心1 故障引起的重构过程只有应用载处理器内部的部署表示,而核心2 故障还需要进行应用指令和数据迁移,受处理器间传输带宽影响,重构消耗时间就更长。处理器A 故障导致的重构时间最长,由于迁移的应用数量较多,需要对迁移过程进行优化,对于处理器A、B 共同部署的应用还需要进行主备切换。

综上所示,综合电子系统重构时间与故障类型及其重构蓝图有关,故障对系统影响越大,重构蓝图越复杂,重构消耗时间也越长。

4 结论

本文基于可重构综合电子系统架构,研究了综合电子系统重构时间方法。首先基于综合电子系统模型,对系统的软硬件进行建模;然后通过分析系统运行过程中产生的故障类型对综合电子系统重构迁移过程进行建模。总结核间重构时间、处理器间重构时间和系统重构时间的计算公式,利用综合电子系统重构验证平台进行故障模拟和重构时间验证。实验证明,重构时间因不同故障类型导致的系统重构有所差异,通过优化重构蓝图和迁移过程可以有效缩短重构过程消耗的时间。