双通道同步复装载脉冲发生方法研究*

王薪贵,鲍温霞,杨智勇,王 靖,禹明慧,吴 迪

(苏州大学光电科学与工程学院,江苏 苏州 215006)

高速脉冲信号作为现代电子技术的基础,在电子通信、工业控制、采集和测量等方面都有广泛的应用[1-2]。随着信息科学的不断发展,为了使电子装置具有更加良好的通用性和灵活性,越来越窄的脉冲宽度与高精度的脉冲宽度调制是高速脉冲信号发生的重要发展方向[3-4]。

20 世纪初,人类就已经开始利用弦振动产生一定频率的脉冲信号。随后,人们又先后使用气体和火花放电等方法将产生的脉冲宽度由毫秒级减小到了微秒级[5]。其开发成本高昂,设计过程复杂,已经很少再被使用。

从20 世纪70 年代开始,原有的模拟信号处理开始被数字信号处理取代,采用集成式逻辑门电路控制生成脉冲信号的方法得到了应用[6]。随着计算机技术的不断发展,可编程实时脉冲发生电路成为了主流。单片机、微控制器等器件具有成本低廉、体积小的优点,利用时钟信号控制其输入输出口来产生脉冲已经成为目前较为常用的一种方法[7]。然而由于这类器件时钟频率一般较低,所以精度相对较低,而且受到外围模拟电路的限制,控制灵活性差、抗干扰能力弱[8]。FPGA 等可编程逻辑器件以其灵活性高、实时性好、数据处理高效等显著优势在脉冲信号发生领域具有不可比拟的优越性,实现了纳秒级精度的脉冲发生与脉冲宽度的调制[9],满足了绝大多数测量与控制的需求[10],但是进一步减小脉冲宽度需要很高的工作频率,通用FPGA 一般难以达到要求。搭建半导体晶体管电路的方法虽然可以实现极窄脉冲信号[11-12],但受制于电路设计,无法实现脉宽调节,很难加以利用。而基于非线性传输线的边沿压缩技术,通过传输材料、技术工艺和参数的设置,可以大大压缩脉冲信号边沿的过渡时间产生皮秒级的脉冲信号,但是非线性传输线技术并没有公开,具有技术垄断性[13]。除此之外,采用极化门控技术产生分辨率更高的脉冲的技术才刚刚起步,设计十分复杂,生成的脉冲宽度也很难加以控制并利用,是目前的前沿课题[14-15]。

针对目前FPGA 设计的脉冲信号发生方法存在的问题,本文提出了一种双通道同步复装载脉冲发生方法,并基于此方法设计了一个纳秒级瞬态脉冲发生系统。系统采用双通道结构对频率相近的时钟信号上升沿技术产生指示信号输出,利用两个通道之间产生的游标效应,对指示信号逻辑运算直接生成纳秒级瞬态脉冲,在此基础上,还可以通过更改计数值,实现纳秒级精度的脉冲宽度调制。

1 双通道同步复装载脉冲发生方法

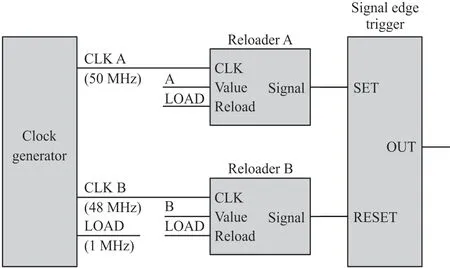

目前通用FPGA 最高工作频率通常在为500 MHz 以下,无法满足直接生成纳秒级瞬态脉冲的发生要求。本文设计了一种双通道同步复装载脉冲发生方法,包括时钟发生(Clock Generator)、同步复装载计数(Reloader_A、Reloader_B)和信号边沿触发(Signal edge Trigger)三个部分。时钟发生部分主要生成两个频率相近的时钟信号和一个装载信号。同步复装载计数部分是由两个可以被装载信号同步装载计数值的计数通道共同组成的控制模块,每个通道对各自的时钟信号进行计数并生成指示信号,将生成的两个指示信号通过信号边沿触发,实现输出电平翻转发生纳秒级精度的窄脉冲。

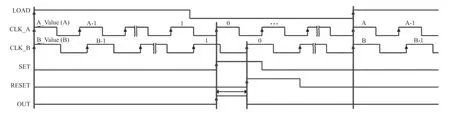

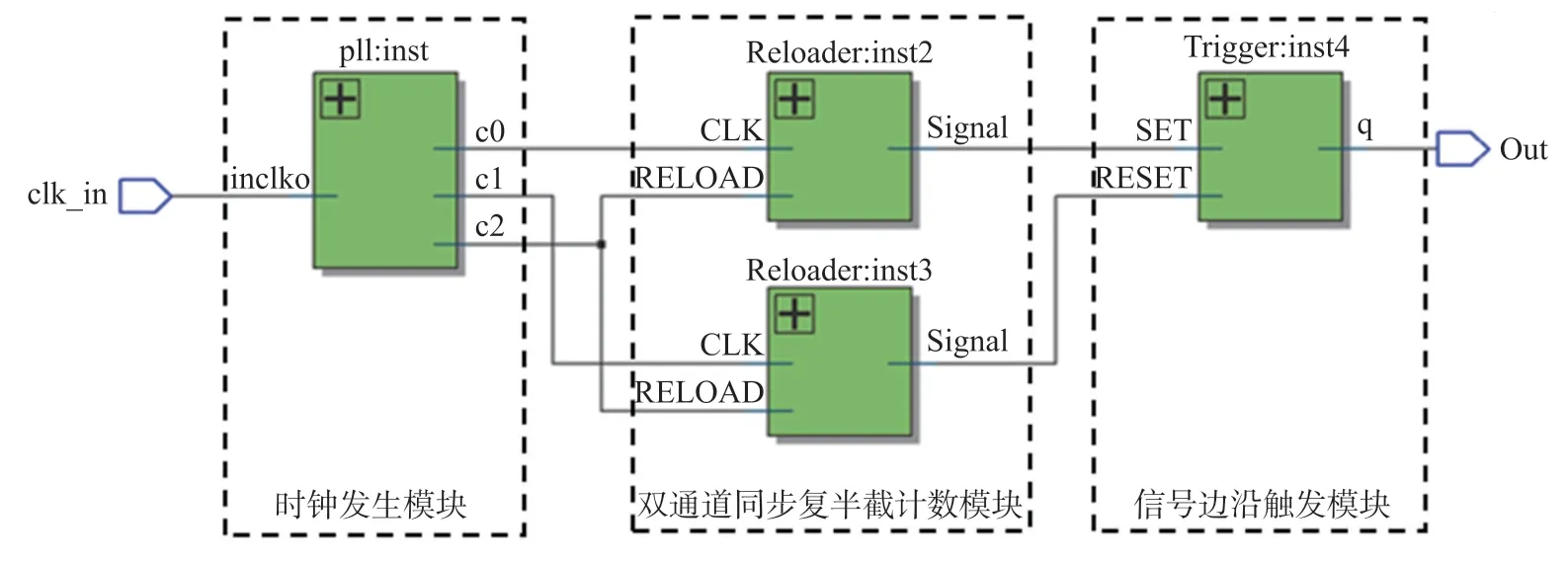

如图1 所示,双通道同步复装载脉冲发生方法首先产生两个频率相近的时钟信号CLK A、CLK B和一个1 MHz 的装载信号LOAD。CLK A 频率较高,作为同步复装载计数部分的第一通道Reloader_A 的计数时钟,CLK B 频率略低,作为第二通道Reloader_B 的计数时钟。两通道分别对各自的输入时钟脉冲进行计数,计数值分别为输入的A_Value 和B_Value,每当LOAD 时钟信号的上升沿到来时,A_Value 与B_Value 就会再次被同步地装载到两个计数通道中,重新开始下一轮计数。每次计数值到达装载的计数值A_Value 或B_Value 时,对应的计数通道就会产生一个指示信号Signal,通道Reloader_A产生的指示信号为SET 信号,通道Reloader_B 产生的指示信号为RESET 信号,由于计数时钟频率不同,产生的SET 和RESET 信号上升沿产生时刻会有一段相位差,在SET 信号上升沿和RESET 信号的上升沿触发输出信号电平翻转,就可以产生一个脉宽可调的瞬态脉冲信号。LOAD 信号不断地将两个通道的计数值同步复装载,这个脉冲信号就会以一定频率不断地出现,实现脉冲发生。双通道同步复装载脉冲发生时序图如图2 所示。

图1 双通道同步复装载脉冲发生方法示意图

图2 双通道同步复装载脉冲发生时序图

当产生的装载信号LOAD 上升沿到来时,计数值A_Value 与B_Value 就会同步被装载到两个通道中。两个通道分别使用CLK_A 和CLK_B 进行计数,每个时钟信号的上升沿计数值减1,当计数值变为0 时,两个通道分别输出SET 和RESET 信号,SET 信号的上升沿使输出OUT 置1,RESET 信号的上升沿使输出OUT 置0,产生瞬态脉冲信号。当LOAD 信号的下一个上升沿到来时,实现双通道计数值的同步复装载,重复脉冲信号的产生过程。

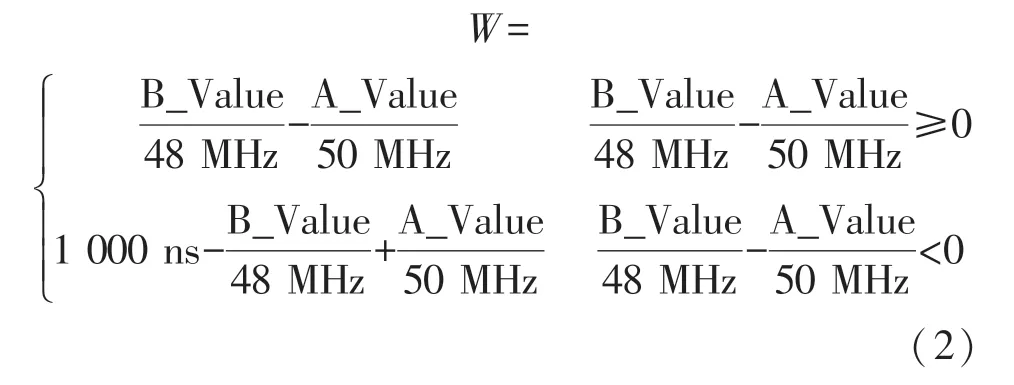

生成的脉冲信号宽度与输入的计数值(A_Value、B_Value)和输入时钟(CLK A、CLK B)的频率有关,输入时钟的频率决定脉冲信号宽度的最小分辨率,以48 MHz、50 MHz 为例,48 MHz 时钟计数一次需要的时间为1/48 MHz,50 MHz 时钟计数一次需要的时间为1/50 MHz,通过上面的分析,两个通道计数完成的时间差就是输出的最小分辨率,最小分辨率可以计算为

即生成的最小脉冲宽度为0.833 ns。

通过改变计数值生成的脉冲宽度W计算公式如下:

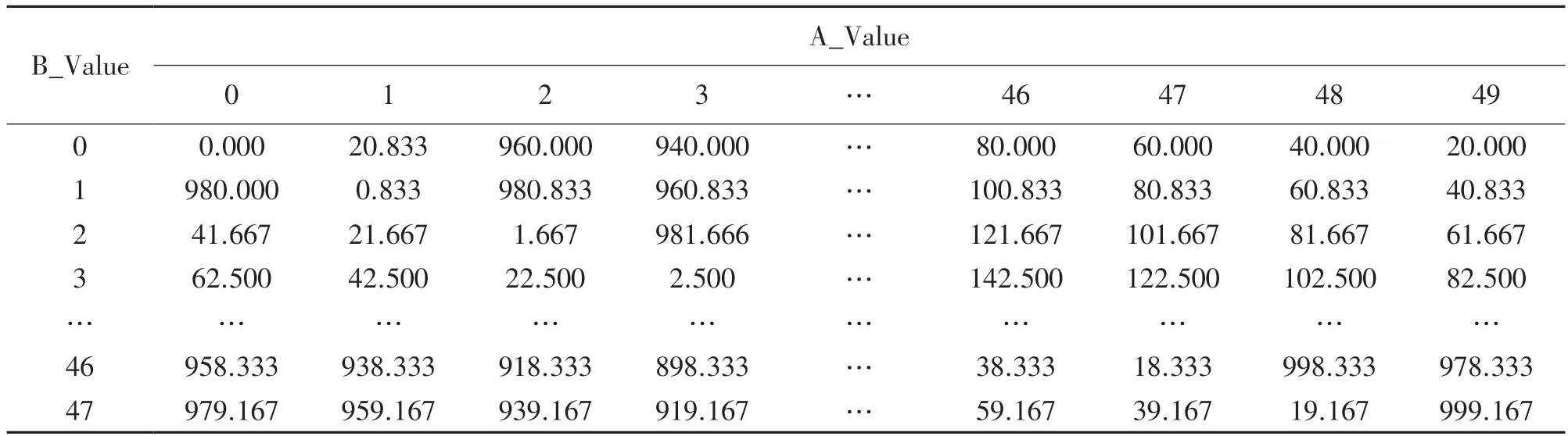

根据脉冲宽度计算公式,A_Value、B_Value 取各值时所对应的脉冲宽度如表1 所示。

表1 脉冲宽度与A_Value、B_Value 取值的关系 单位:ns

A_Value 和B_Value 取值均为0 时,脉冲宽度为0,不产生脉冲信号;当A_Value =B_Value 时,产生的脉冲宽度为A_Value(或B_Value)×0.833 ns;其他取值情况下,如果时钟频率取值为50 MHz 和48 MHz,初值装载信号为1 MHz,要使模块能在下一次初值重新装载前能够产生指示信号,计数值A_Value 和B_Value 的最大分别为49 和47,当A_Value 取最大值49,B_Value 取最大值47 时可以生成最大脉冲宽度,宽度为999.167 ns。

2 基于双通道同步复装载的瞬态脉冲发生系统设计

基于双通道同步复装载脉冲发生方法,本文设计了一个纳秒级瞬态脉冲发生系统,该系统的RTL视图如图3 所示。

如图3 所示,系统可以分为时钟发生模块、同步复装载模块和信号边沿触发模块。以下本文将对这三个重要模块设计进行详述。

图3 系统RTL 视图

2.1 时钟发生模块设计

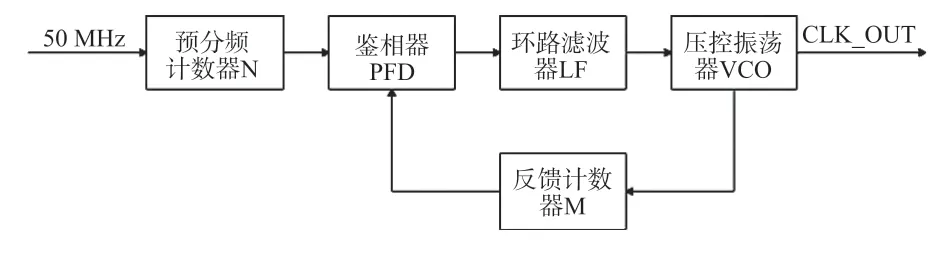

时钟作为时序电路的基础,在整个FPGA 程序开发过程中都十分重要。使用直接数字频率合成(Direct Digital Synthesis,DDS)技术,可以产生任意频率的时钟信号,多锁相环(Phase Locked Loop,PLL)也同样可以产生FPGA 工作频率以内的任何时钟信号组合。但是本文提出的双通道同步复装载脉冲发生方法对产生时钟的相位同步性要求极高,上述方法均无法保证信号的初相位完全相同。为了使时钟信号的相位相等、频率稳定,双通道同步复装载脉冲发生方法的时钟发生模块使用单个锁相环进行设计。由于使用单一锁相环生成的多路时钟会受到FPGA 内部结构制约,需要对生成的时钟频率进行精心设计。经过多次测试,生成的最佳时钟信号组合为48 MHz 和50 MHz。

如图4 所示,锁相环是一种闭环频率控制系统,本文设计的纳秒级脉冲发生器使用Altera 的FPGA芯片,可以通过IP 核对PLL 进行参数设置。首先将外部晶振产生的50 MHz 时钟通过预分频计数器(N=25)产生2 MHz 时钟送入鉴相器,鉴相器将反馈信号与输入时钟进行比较,发出控制信号经过环路滤波器驱动压控振荡器调整输出时钟频率,直到两个信号同步。当反馈回路中的反馈计数器M=24 时,输出时钟为48 MHz 时系统达到稳定,等效于对50 MHz 进行了25 分频、24 倍频输出48 MHz 时钟信号。

图4 FPGA 芯片PLL 结构图

由时钟发生模块产生的50 MHz、48 MHz 时钟将作为双通道同步复装载计数模块的工作时钟。

2.2 双通道同步复装载计数模块设计

双通道同步复装载计数模块由两个复装载计数模块组成,在本瞬态脉冲发生电路设计中起核心控制作用。为了生成频率稳定的脉冲信号,两个通道模块输出的指示信号要能够按一定周期同步稳定出现,而指示信号输出受脉冲计数值直接控制,因此,两个通道计数值能否同步复装载将对生成的脉冲信号造成重大影响。

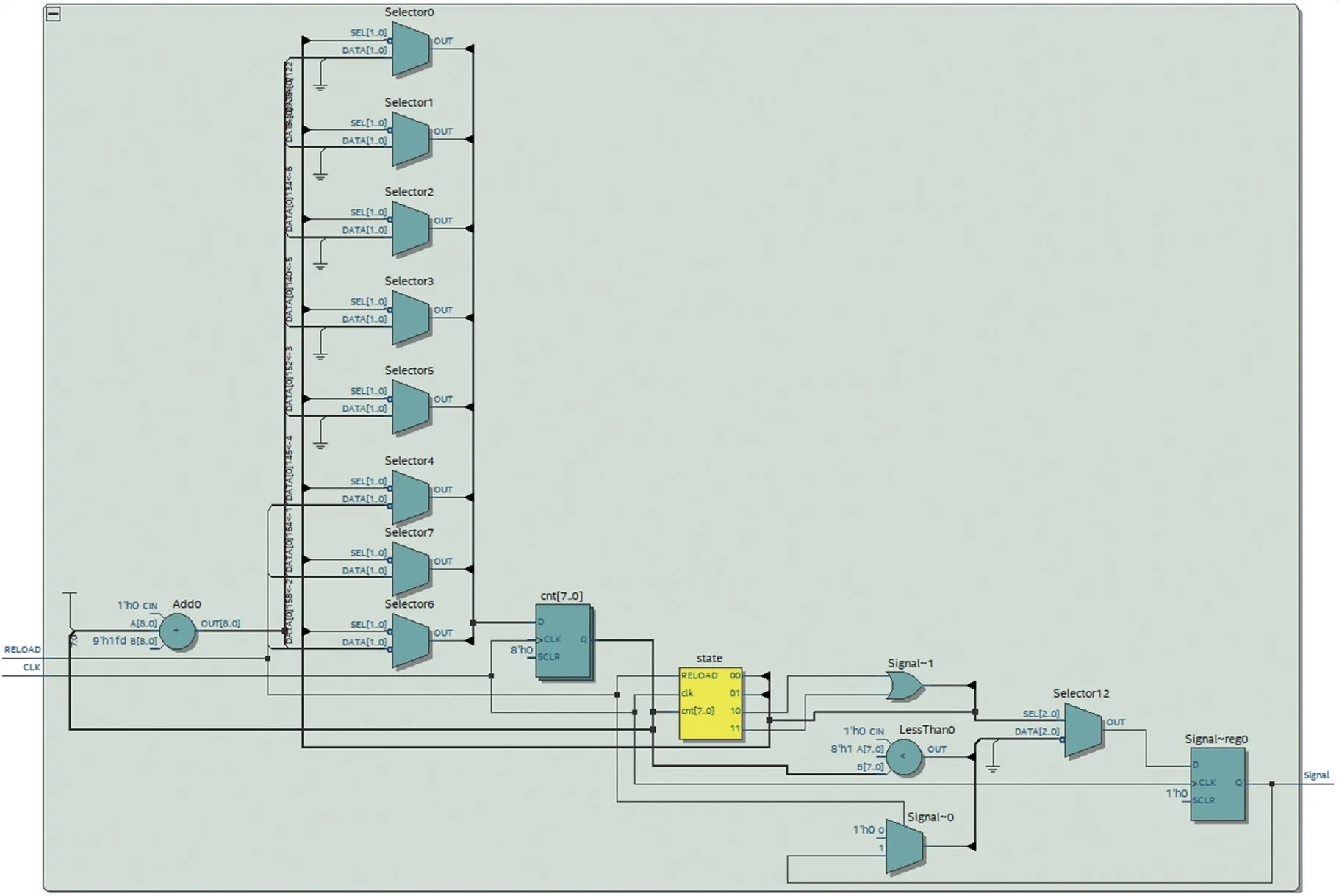

为了实现计数值的周期性同步复装载,本文给出一种复装载计数模块设计方法,其RTL 视图如图5 所示。

如图5 所示,复装载计数模块以寄存器state 进行状态机设计,状态机状态受到输入的RELOAD 信号和计数值cnt 共同控制。初始状态机工作状态为0,由Selector12 选择输出Signal 信号为0,八位计数寄存器cnt 的值每一位都受到选择器控制为一固定值保持不变,等待装载信号装载计数值。当RELOAD 信号上升沿到来时,状态机工作状态变为1,寄存器cnt 被赋予初值后在CLK 信号的上升沿进行递减计数,比较器在cnt 计数到0 时输出变化使得选择器Selector12 输出1 将指示信号Signal 变为高电平,同时状态机工作状态变为2。工作状态2保持一个CLK 时钟周期,将指示信号拉低后进入状态3。状态3 在监测到LOAD 信号的下降沿时,回到状态0,等待下一个装载信号,避免了cnt 寄存器在一个装载信号中被多次复装载。

图5 同步复装载模块的RTL 视图

本设计复装载模块的工作时序图如图6 所示,由LOAD 信号上升沿触发装载计数值Value 开始计数,在CLK 时钟信号的每个上升沿到来时,寄存器的值减1,当寄存器中的值减1 变为0 时,计数完成,输出指示信号,保持一个时钟周期后,等待下一次装载。当下一次LOAD 信号上升沿到来时,Value值被重新装载,再次开始计数,按一定周期生成稳定的指示信号。

图6 同步复装载模块工作时序图

当两个复装载计数模块的计数时钟信号初相位相同且使用同一个LOAD 信号进行计数值的复装载时,就构成了双通道同步复装载计数模块。

双通道同步复装载模块计数产生的两个指示信号Signal,通过信号边沿触发模块,生成对应的瞬态脉冲信号。

2.3 信号边沿触发模块设计

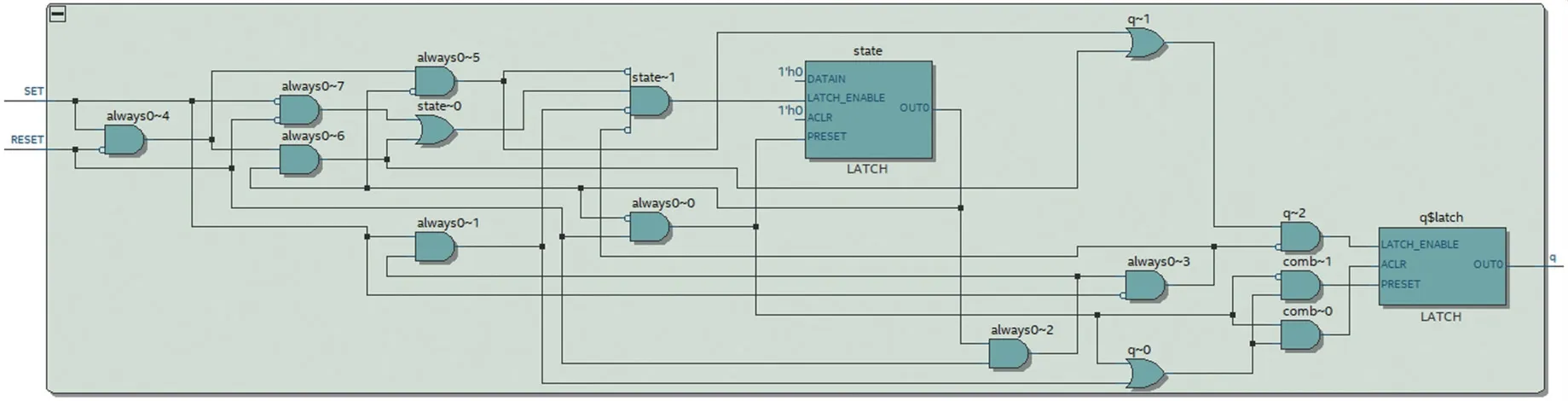

信号边沿触发模块的作用是输出瞬态脉冲信号,根据同步复装载计数模块的预设计数值的不同,产生的指示信号相位差也不尽相同。要实现表1 中任意宽度的脉冲信号,必须严格要求信号边沿触发模块实现在输入信号SET 上升沿时刻,输出信号变为高电平,在RESET 的上升沿时刻输出信号变为低电平。当两通道同步复装载计数器的输出指示信号,即SET、RESET 信号的上升沿时刻相距很近时,输出信号的高低电平就能在极短时间内完成翻转,生成极窄瞬态脉冲信号。本文给出一种可行的设计方法,RTL 视图如图7 所示。

图7 模块的RTL 视图

电路实际由基本逻辑门和锁存器组成,锁存器分别锁存信号state 和输出信号q。state 为状态量,表征RESET 信号的当前状态。当state 为1 时,表示RESET 信号的上升沿已经到来且RESET 仍保持高电平;当state 为0 时,表示RESET 信号为低电平。state 只有在RESET 信号状态变化时才产生变化,否则由锁存器进行锁存。SET、RESET 信号初始状态均为低电平,此时state 和输出q状态均为0。只要RESET 信号上升沿到来,输出q的锁存器复位引脚ACLR 就会被使能,q值被清零,然后state 被置1。而当SET 信号上升沿到来时,只要RESET 信号不同时出现上升沿,经过逻辑运算后,q锁存器的PRESET 总能变为高电平输出1。

本方案设计的信号边沿触发模块真值表如表2所示。

表2 信号边沿触发模块真值表

如信号边沿触发模块真值表所示,SET 信号为低电平,只有当RESET 信号到达上升沿时,输出信号为0,其他状态时输出保持原状态不变。在SET的上升沿处,只有RESET 信号也同时为上升沿模块输出0,其余状态全为1。SET 信号处在高电平或下降沿状态时,只有RESET 的信号的上升沿触发0 输出,其他状态下输出保持不变。由真值表可得,只有输入信号SET、RESET 的上升沿才能触发输出状态发生变化,SET 的上升沿使输出信号为1,RESET 的上升沿使输出信号为0,而当SET 和RESET 的上升沿一起到来时,输出信号状态变为0。

通过对以上各功能模块的设计,实现了纳秒级的脉冲发生。脉冲发生器首先由时钟发生模块产生50 MHz 与48 MHz 的两路频率相近的时钟信号,分别作为同步复装载模块Reloader_A、Reloader_B 的工作时钟。Reloader_A、Reloader_B 分别生成指示信号Signal_A 与Signal_B,若计数值A_Value =B_Value =1,Reloader_A 与Reloader_B 都将在一个工作周期后输出指示信号,由于工作频率不同,CLK_A的频率更高,所以Signal_A 的上升沿将先于Signal_B 到来,两者的时间差为0.833 ns。

将Signal_A 与Signal_B 输入信号边沿触发模块,Signal_A 作为SET,Signal_B 作为RESET。信号边沿触发模块只有在信号的上升沿才会触发输出变化,当Signal_A 的上升沿到来时,输出信号变为1,0.833 ns后,Signal_B 信号的上升沿将输出信号置0,这样就产生了一个宽度为0.833 ns 的窄脉冲信号。

3 实验结果与分析

3.1 实验结果验证

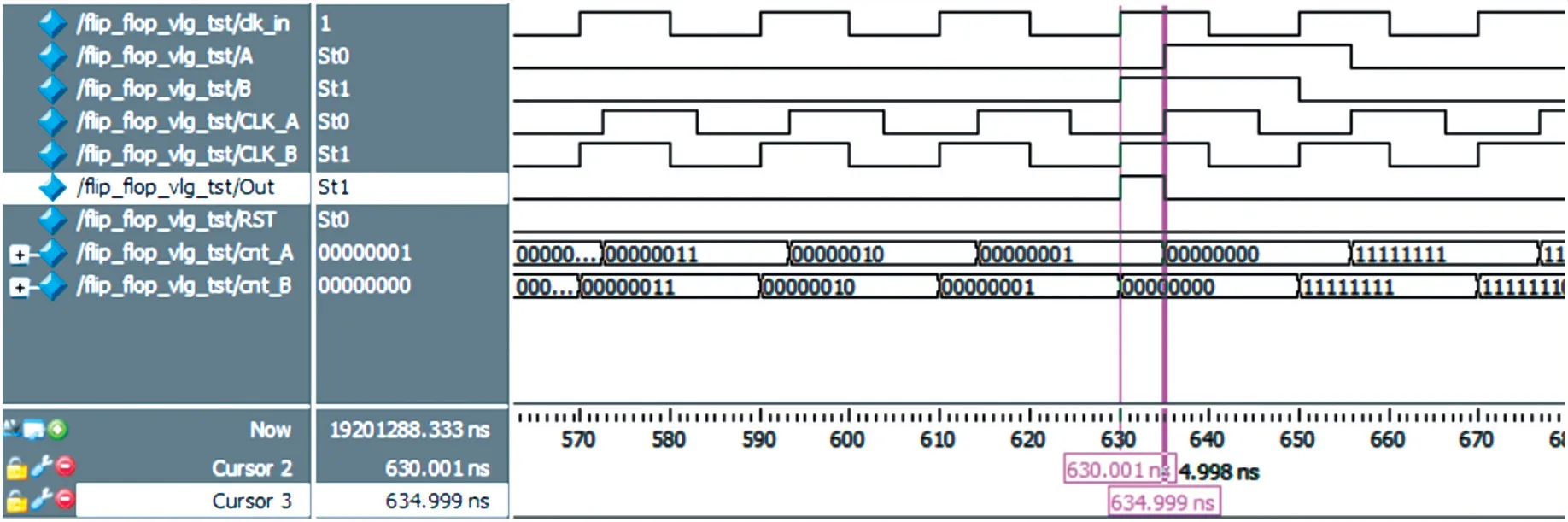

采用Modelsim 软件进行功能性仿真。为了测试脉冲宽度的最小精度,将同步复装载模块的计数值均设置为1,使用50 MHz 方波作为输入时钟。实验结果如图8 所示。

图8 Modelsim 最小分辨率仿真波形

当双通道同步复装载计数模块的初始计数值都为1 时,生成的脉冲宽度应为双通道同步复装载脉冲发生方法能产生的最小脉冲宽度,也是脉冲宽度调节的最小分辨率。根据脉冲宽度计算公式,生成的脉冲宽度应为0.833 ns,与Modelsim 仿真结果相同,最小分辨率仿真正确。

数字化档案带来了丰富的信息资源,同时也对档案信息的检索提出了挑战。传统的档案文件是按类型分类并依照著录规则进行著录,经人工整理按档号顺序有序存储的。

当计数值都设置为6 时,仿真波形如图9 所示。

图9 ModelSim 功能性仿真波形

由图9 可见,利用Modelsim 标尺计算出的脉冲宽度值显示为4.998 ns,而根据脉冲宽度计算公式,当初始计数值都为6 时,输出的脉冲宽度应为4.998 ns,结果完全一致,实验脉宽调制功能性验证结果正确。

下面使用示波器对FPGA 实际生成的脉冲信号进行测试。FPGA 使用Altera 的EP4CE15F23C8 芯片。示波器型号为横河DL9240,其模拟带宽为1.5 GHz,最高实时采样率为10 Gsample/s。下图脉冲信号的设定值分别为0.833 ns 和4.998 ns。

图10 与图11 分别为设定宽度0.833 ns 和4.998 ns的信号波形,每格代表的时间均为5 ns,通过对脉冲信号有效部分宽度测量,图中所示的实际脉冲信号与设定值吻合。示波器的结果显示该脉冲发生器实现了纳秒级脉冲信号发生及脉冲宽度调制。

图10 0.833 ns 脉冲信号波形

图11 4.998 ns 脉冲信号波形

3.2 实验数据分析

通过对上述实验数据的分析,双通道同步复装载脉冲发生方法与其他窄脉冲发生方法的各项性能如表3 所示。

表3 双通道同步复装载脉冲发生方法与其他方法生成脉冲参数

直接计数方法是利用FPGA 内部锁相环将外部晶振频率倍频,将其作为计数时钟进行计数,生成1 ns 分辨率的脉冲信号需要至少1 GHz 稳定工作频率,通用FPGA 显然难以达到要求。脉冲的编译码生成方法利用脉冲信号只有1 和0 两种状态,将脉冲信号以时间片的形式进行切割,每个时间片的脉冲状态用一位二进制数表示。通过上位机将二进制序列数据发送到FPGA 中就可以生成对应的脉冲信号。但是编译码的最小时间片精度受到FPGA 本身工作频率制约,难以实现更高的分辨率。

除此之外,双三级管并联电路利用LC 电路阻尼原理和双射频三极管并联产生的雪崩效应,产生了幅度较大的脉冲信号,但脉冲宽度也较大。而利用数字逻辑器件的竞争冒险实现窄脉冲发生的双非门结构设计虽然生成了极窄脉冲信号,但是其脉冲宽度受制于电路设计,无法进行调节。

直接计数法和脉冲的编译码生成方法是通过提高FPGA 自身工作频率来提高最小分辨率的。通常的FPGA 工作频率一般都在500 MHz 以内,脉冲宽度调制的最小分辨率不会小于2 ns。与其原理不同,本文设计的双通道同步复装载脉冲发生方法在有限的FPGA 工作频率下,使用双通道同步复装载计数模块分别对频率相近的48 MHz 和50 MHz 时钟信号计数并产生指示信号。两个通道的指示信号之间会因为游标效应产生相位差。利用相位差产生窄脉冲的等效工作频率可以达到1 GHz 以上,而与FPGA 本身的最大工作频率无关,因此最终能够达到0.833 ns 的纳秒级脉冲分辨率。不仅如此,双通道同步复装载脉冲发生方法的0.833 ns 最小脉冲宽度相比脉冲宽度不可调节的双三极管并联电路设计仍然具有显著优势。双非门结构设计可以生成最小脉宽为0.15 ns 的窄脉冲信号,但电路设计完成后,脉冲宽度无法调节,很难加以应用。本文的方法不仅实现了0.833 ns 的窄脉冲信号的发生,也实现了0.833 ns 的脉冲宽度调节精度。

4 结论

本文提了一种双通道同步复装载脉冲发生方法。由时钟发生模块产生两个频率相近的计数时钟和同步装载信号,输出给同步复装载计数模块。当同步复装载计数模块的计数值满足条件时,输出指示信号给信号边沿触发模块生成所需宽度的脉冲信号,实现了纳秒级脉冲信号的FPGA 直接输出。实验结果表明,双通道同步复装载脉冲发生的最小脉冲宽度为0.833 ns,脉宽调节精度也为0.833 ns,和现有的FPGA 脉冲发生技术相比,达到了更窄的脉冲宽度和更高的脉宽调节精度,和无法调节脉宽的窄脉冲发生技术相比,设计更为灵活。本文的方法实现了纳秒级的瞬态脉冲信号发生和精度更高的脉冲宽度调制。

双通道同步复装载脉冲发生方法实现了纳秒级的瞬态脉冲信号发生和脉冲宽度调制,达到了预期的设计目的。在此基础上,该方法还可以生成更高分辨率的脉冲信号。但是受目前示波器的带宽限制,难以对更高分辨率的脉冲信号进行准确观测,将在今后的研究中改进设计,进一步提高脉冲信号的分辨率。