遥测发射机本振源信号实现方法及应用分析

胡思猛 韦全亮 高大勇 曾祥松

【关键词】本振源;锁相环;发射机;频率

引言

本振源设计作为通用化电路,在研制过程中能够高效提出设计方案。对本振源的设计研究,徐林山[1]分析了本振源设计中影响信号的因素,采用PLL+DDS实现频率合成,并对本振源信号展开测试验证。周逍宙[2]研究了基于DDS的宽带低相噪本振源,阐述和分析了几种本振源方案的设计,并对实现的指标进行了验证。吴钢锋[3]提出了实现UHF 本振源的锁相环频率合成方案,并提供了必要的公式推导和计算机仿真。胡蒙筠[4]针对5G 毫米波通信系统对本振源频率、相位噪声、杂散抑制要求的提升,提出了一种结合ADF4002 和2 个ADF5355 频率合成器芯片,可同时用于中频和射频电路的高性能本振源。顾宇[5]在锁相本振源的设计中,使用ADS软件对压控振荡器的各种参数,如输出频率、输出功率、相位噪声等进行了仿真,应用软件设计了恰当的环路滤波器,这些软件的仿真为实际电路的实现提供了重要的参考。彭慧丽[6]采用低频高稳振荡与低噪声倍频相结合的方法,研制了一种高频高稳恒温晶体振荡器,很好地满足多领域应用对高频高稳定信号源的需求。

综述,相关研究人员做了大量本振源设计实现与应用工作。发射机本振源信号实现的关键在于晶体振荡器与PLL电路的选型搭配,建立准确的本振源信号实现电路有利于发射机调制电路快速设计,可作为典型应用电路嵌套使用。本文采用有源晶振提供基准信号、通过负反馈技术在PLL电路实现,采用集成方式的电路实现手段,对本振源生成电路进行模块化,并通过频谱分析仪测试以及产品应用,验证输出频率的正确性及有效性。

一、关键组成

本振源主要由晶体振荡器及锁相环电路组成,就发射机而言,本振源的设计通常主要考虑频段、频率精度、相位噪声、杂散抑制等指标,而频段是最优先考虑因素,因为不同型号的发射机需要的中心频率不同。而其它指标可通过后级电路滤波、匹配、接地等方法得到保证。

(一)PLL电路

锁相环是利用负反馈技术的高稳定度振荡电路,通常由电压控制振荡频率的VCO与晶体振荡器、频率稳定的基准信号与输出信号进行比较的鉴相器PD(PhaseDetector),以及将鉴相器的脉冲信号输出进行平滑处理的环路滤波器,分频器、基准信号振荡器等构成。

(二)基于PLL芯片PE3336的本振源

该电路方案为直接置数模式,将参考时钟频率通过锁相环电路倍频至射频需要频率,为产品提供对相位噪声要求不高的本振源。

工作原理:鉴相器PE3336 将参考时钟fr 进行R 分频得到鉴相频率fc,将VCO 反馈的频率fo 进行N 分频得到fp,fc 和fp 进行频率和相位比较,得到调谐电压,该调谐电压经过环路滤波器滤波,进入VCO 调谐,得到频率fo,并功分成2 路,其中1 路输出至后级电路,另1 路反馈至鉴相器进行N 分频得到fp,fc 和fp进行频率和相位比较,当差值无限小时,锁相环锁定。

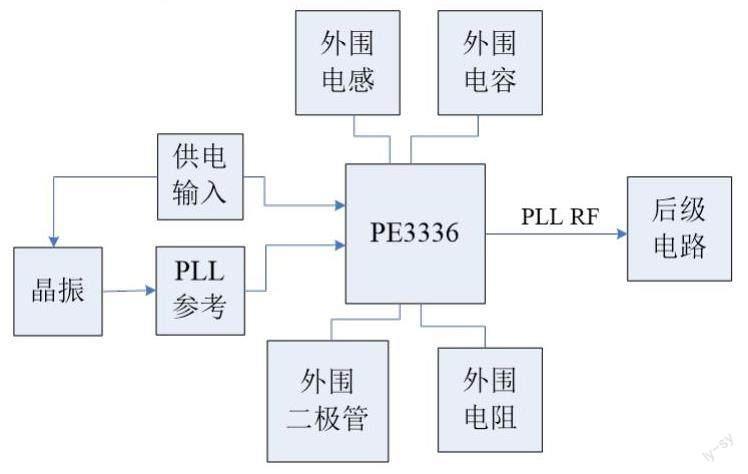

图 1 原理框图

图2 PE3336元件图

实现方法:根据锁相环参考时钟频率和输出频率,决定锁相环路的鉴相频率和环路带宽,利用PE公司提供的计算EXCEL 表进行计算,决定环路中关键电容及电阻的值。注意计算环路时,环路带宽取5kHz~10kHz 为宜,相位欲度取50°~70°为宜,鉴相频率不大于20MHz。 该方案实现原理框图如图1,PLL RF即为生成的本振源信号(后文同),主芯片元件图如图2。

(三)基于PLL芯片ADF4351的本振源

功能原理:该电路为小数N 分频锁相环电路,将参考时钟fr 锁定至产品需要的本振信号fL,为射频类产品提供35 MHz~4400 MHz 本振源信号,应用于射频类产品。

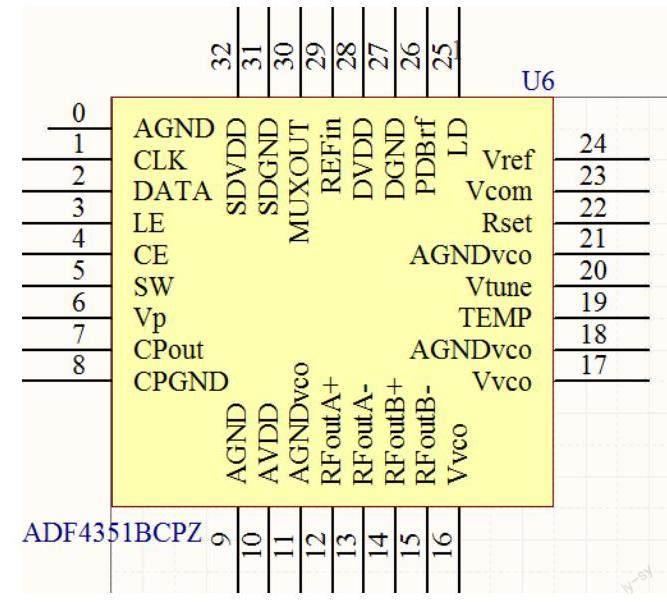

实现方法:该电路输出信号相位噪声需要调整时,可通过ADI 公司的ADIsimPLL ver 3.50 软件计算环路滤波器参数,电路设计时环路带宽初始值取10kHz。ADF4351输出功率可程序设定为:-4dBm、-2dBm、+2dBm、+5dBm,通过设置寄存器3 的DB3、DB4 位实现。ADF4351虽然为塑封器件,但其封装为LFSCP 形式,能够顺利通过超聲扫描,能满足要求较高的场合。该方案实现原理框图如图3,主芯片元件图如图4。

图3 原理框图

图4 ADF4351元件图

(四)基于PLL芯片Si4136的本振源

该电路为整数N 分频锁相环电路,Si4136为集成度完整的锁相环电路,内部包含鉴相器、环路滤波器、压控振荡器,应用于射频类产品,为产品提供本振源,该锁相环电路可同时提供2050MHz~2500MHz的射频信号和62.5MHz~1000MHz中频信号。

功能原理:为射频类产品提供本振源信號,将参考时钟fr 锁定至产品需要的本振信号fL 或fI。

实现方法:该锁相环电路为最简单锁相环电路,外围除电阻和电源去耦电容外,几乎不需要其它元器件,因此硬件确保无虚焊后不需要其它调试。在软件方面,注意Si4136 参考时钟fr 支持范围为2MHz~50MHz。当fr 为2MHz~25MHz 时,寄存器0 的Bit 6 位(参考时钟分频器)需值“0”,即XINDIV2 = 0,鉴相频率fc = fr/R,射频输出fL=(2N/R)×fr,中频输出fI=(N/R)×fr;当fr 为25MHz~50MHz时,寄存器0 的Bit 6 位(参考时钟分频器)需值“1”,即XINDIV2 = 1,鉴相频率fc =fr/R,射频输出fL=(N/R)×fr,中频输出fI=(N/2R)×fr。

该方案实现原理框图如图5,主芯片元件图如图6。

图5 原理框图

图6 Si4136元件图

二、应用要点分析

PE3336型:该电路为直接置数方式,M、A、R 寄存器通过上下拉电阻实现,若采用程序实现,/Bmode(16引脚)需接低电平,Smode 为“0”时为并行模式,为“1”时为串行模式,不使用引脚可以悬空。当锁相环失锁时,先用示波器检查参考时钟是否有输出,其次是环路是否存在虚焊、开路现象,若为高低温下锁相环路频繁失锁,则故障多为环路参数设置不当或有元器件在高低温下失效。注意:PE3336 工业级已经停产,Peregrine公司只生产军品级PE83336,国内中电24所有SB3336 可替代。

ADF4351型:该电路输出信号相位噪声需要调整时,可通过ADI 公司的ADIsimPLL Ver 3.50 软件计算环路滤波器参数,电路设计时环路带宽初始值取10kHz。ADF4351输出功率可程序设定为:-4dBm、-2dBm、+2dBm、+5dBm,通过设置寄存器3 的DB3、DB4 位实现。建议使用回流焊接,同时考虑到器件的返修性,该热焊盘中心可开一个大圆孔,支持手工焊接;ADF4351 虽然为塑封器件,但其封装为LFSCP 形式,能够顺利通过超声扫描。ADF4351 内部集成VCO,体积小,为小数N 分频锁相环,输出频段完全覆盖遥测产品频段。

Si4136型:注意射频输出VCO1 的输出频率范围为2300MHz~2500MHz,N 寄存器地址为Register3,R 寄存器地址为Register 6;VCO2 的输出频率范围为2050MHz~2300MHz,N 寄存器地址为Register 3,R 寄存器地址为Register 6。Si4136 外围电路最简单,电路布局占印制板面积小,对于低成本或要求不高的场合,锁相环电路首选Si4136。

三、验证及应用

以上三种方案实现的本振源信号,通过与固定中频进行混频后得到的射频输出频率,信号稳定、指标优良,并经过振动、温冲、电磁环境考核,已在多款遥测产品中使用。本文方案实现的本振源信号在频谱分析仪上的显示,信号输出后带有杂散信号,经过后级电路滤波、匹配信号链路等可以得到较为纯净的本振源信号。基于本文实现的本振源,混频后的射频信号在各种常用的试验环境下信号频率稳定,输出频谱产品实际应用中满足使用需求,如图7所示。发射机内部电路模块化设计、作为典型电路的推广、借用、嵌套使用,使得频率源生成电路的设计更加方便,当有需求输入时,根据射频信号频率,通过FL±FI=FO,可以反推本振源所需频率(FL为本振信号,中频FI通常固定,FO为射频输出中心频率),从而快速选取本振源设计方案,实现所需频率,为发射机整体电路设计提供了快捷方法,有利于产品方案快速落实,加速产品研制进度。

图7 本振源信号与杂散信号频谱图

结论

本文以锁相环芯片及电路应用为基础,分析了三种发射机常用的本振源设计方法,探讨了各个方案的适用性以及应用要点,主要得到以下结论:

(1)针对不同设计需求,选择适宜的本振源设计方法,可快速提出解决方案。

(2)对发射机内部本振电路进行模块化电路设计,通过使用有源晶振与锁相环结合的思路,得出不同的本振源信号,为遥测领域发射机本振源设计提供了理论支撑及方案选择参考。

(3)本振源设计方案在产品中的使用验证了思路的正确性,并以此高效的设计思想,促进了整机电路方案设计的效率提升,并为各产品其它部分电路的通用化、模块化设计提供了研制思路。