基于VPX的多模多频段微波收发组件设计与实现

吴华尧

摘 要:微波收发组件是通信系统中的重要部分,本文设计了一种基于VPX技术的多模多频段微波收发组件,采用了VPX标准总线结构,实现了其通用化和标准化。组件用于多种模式多种频段的软件无线电通信系统,系统用于无线传输高清视频图像。该组件接收噪声系数:≤1.8 dB,ACPR:≤-35 dBc,发射功率以及各次谐波抑制等均达到指标要求,满足通信系统的实际要求。

关键词:VPX;多频段;收发组件;软件无线电

VPX总线是在VME总线基础上提出的新一代高速串行总线标准,可以适应结构要求复杂、数据速率高的应用环境,而且可以满足多核多CPU(中央处理器)计算,以及 DSP(Digital Signal Processing,数字信号处理)数据处理,结合高性能FPGA(Field Programmable Gate Array,现场可编程阵列逻辑)),是国防及航空领域应用中模块化处理平台的发展趋势[1]。基于此,本文设计了一种多模多频段微波收发组件,用于多种模式多种频段的宽带软件无线电通信系统。接收噪声系数和发射功率等均达到指标,满足通信系统的工作要求。

1 微波收发组件的设计与实现

1.1 组件方案设计

微波收发组件拥有独立的收发通道,收通道对射频信号进行滤波、混频、放大、模数转换[2];发通道对数字I/Q数据进行数模转换,对射频信号进行滤波、放大。微波收发组件通过SRIO(Serial Rapid I/O,串行高速I/O)接口与图像信号处理组件进行I/Q数据交互,通过SMA(SubMiniature version A)接口与天线和多工器进行射频信号交互。

1.2 指标要求

工作频率:300-400 MHz,1 400-1 500 MHz,1 700-1 800 MHz。

自動增益调节范围≥60 dB(不包含AD9371内部的增益调节)。

噪声系数:≤1.8 dB。

抗烧毁能力:37 dBm功率输入5分钟时,接收机不损坏。

输出平均功率:≥8 W(300-400 MHz),≥4 W(1 400-1 500 MHz),≥1 W(1 700-1 800 MHz)。

ACPR:≤-35 dBc(中心频率10 MHz偏移,8 MHz信号带宽)。

二次谐波抑制:≥40 dBc;三至五次谐波抑制:≥70 dBc;其他谐波:≥60 dBc。

收发切换时间:≤3.0 μs。

1.3 组件硬件设计

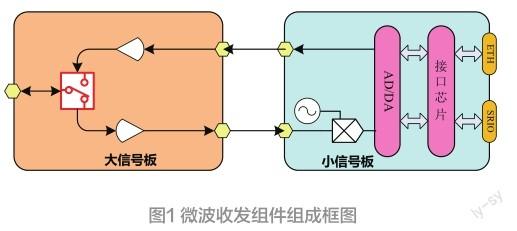

微波收发组件由大信号板和小信号板组成,通过板间连接器垂直相接,板间有金属屏蔽腔体隔离。依照VPX标准,采用3U标准的VPX板卡架构对该单元进行设计,如图1所示。

在发射模式下,小信号板主要用于将SRIO输入的波形数据进行数字模拟变换,变换后的零中频信号直接通过正交上变频输出到对应的射频频段,再通过射频前端对其进行功率放大后输出。

在接收模式下,外部输出的小信号,先经过大信号板的低噪放进行放大,从而确保收到的小信号的信噪比在后级相关处理后不至于进一步降低。放大后的信号进入小信号板,分别经过下变频,中频滤波后进入AD器件进行零中频下变频并AD采样。采样的数据通过SRIO通道送入图像信号处理组件进行解调分析。

1.3.1 小信号板设计

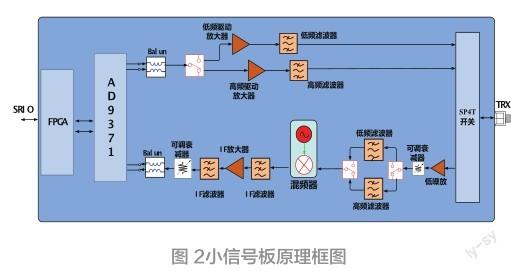

小信号板原理框图如图2所示,总体分为发射和接收通路。发射采用零中频方案。SRIO输入的波形数据经过FPGA转换后,再采用AD9371进行数模变换后通过巴伦和开关进入驱动放大器中,信号放大后进入滤波器,最后通过单刀四掷开关经过垂直互联射频口进入大信号板。

接收采用超外差接收机电路方案,通过两次变频将接收到的300-400 MHz和1 400-1 800 MHz射频信号变到零中频基带信号(I&Q信号)进行后续处理。300-400 MHz射频信号通过低噪放、数控可调衰减器、调谐滤波、放大进入第一混频器RFFC2071,该混频器本振频率1 130-1 230 MHz扫频,信号频率变为830 MHz固定中频(IF);再通过中频滤波放大,进入正交解调器AD9371,该正交解调器本振频率为830 MHz,得到零中频基带信号(I&Q信号),通过开关控制实现不同中频带宽的输出。通过耦合器和检波器实现通道功率电平的检测,完成自动增益的控制。

同理地,高频1 400-1 800 MHz射频信号通过低噪放放大后进入数控可调衰减器,数控可调衰减器可以根据信号大小调节信号强度,增大了接收路动态范围。然后信号再通过调谐滤波、放大进入第一混频器RFFC2071,该混频器本振频率2 230-2 630 MHz扫频,信号频率变为830 MHz固定中频;再通过中频(IF)滤波放大,进入正交解调器AD9371,该正交解调器本振频率为830 MHz,得到零中频基带信号(I & Q信号),通过开关控制实现不同中频带宽的输出。

最后基带信号通过AD9371的JESD204B接口输出,经过FPGA转换为SRIO高速接口与VPX背板上图像信号处理组件进行数据交互,从而完成视频图像信号的解析。

1.3.2 大信号板设计

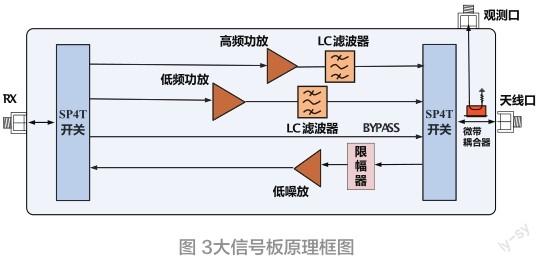

小信号板的信号通过板间垂直射频连接器进入大信号板,进入SP4T射频开关根据频段和功能分别切换进入不同通路。大信号板原理框图如图3所示,总体分为发射和接收通路。

发射信号分别进入高频或低频大信号功放,经过功放放大后进入LC滤波器进行滤波,主要滤除各次谐波分量。对于低频功放,为满足8 dB峰均比的信号发射需求,8 W输出的功率应采用1 dB压缩点100 W的LDMOS管进行设计确保;对于高频功放,为满足8 dB峰均比的信号发射需求,4 W输出的功率应采用1 dB压缩点为40 W的LDMOS管进行设计确保。在此功率输出情况下,所选高频和低频功放管的ACPR指标均小于-40 dBc,能够满足设计指标需求。

接收信号经过SP4T射频开关经过限幅器,限幅器主要用于保护接收电路,削弱大功率接收信号,可以满足抗烧毁能力[3]。经过限幅器后再进入低噪放放大,然后进入小信号板。

信号通过前级微带耦合器耦合进入小信号板的AD9371观测口(ORX),从而对天线口信号进行实时监测。

1.3.3 组件PCB设计

微波收发组件有数字电路和模拟电路两部分。按照不同电路类型,将他们分开布局,这样有利于最后地的分割,数字地紧贴在数字电路下方,模拟地紧贴在模拟电路下方[4]。这样有利于信号的回流和两种地平面之间的稳定。

布局布线时遇到走线困难,需要灵活调整器件位置,如大信号板射频开关为了布局走线需要将其旋转一定角度,既节省了空间,也使走线更加平直。

微波收发组件中内部进行屏蔽设计,数字信号和模拟信号,大信号和小信号用金属隔腔进行隔离防止信号内部互相串扰,影响功能性能[5]。

2 结构设计

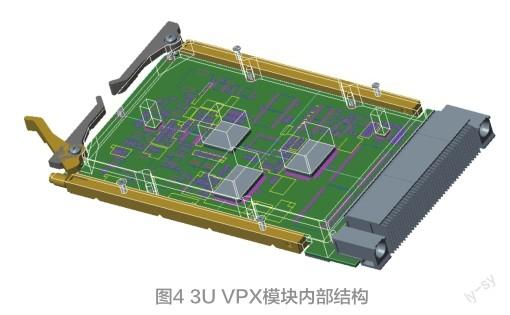

为满足产品的设计要求,为满足产品性能、重量和屏蔽的要求,壳子采用铝材制作。采用标准3U VPX导冷结构,所有尺寸按照系统要求尺寸进行设计,在印制板设计时,充分考虑器件的布局布线以满足尺寸要求。

3U VPX模块中有些器件(主要为集成电路和功率器件)的热功耗较大,因此对3U VPX模块的屏蔽盒结构做了特殊设计,将热功耗较大的位置做凸起设计(如图4所示),金属凸起与与器件表面之间的间距保持在0.8 mm,在装配前,在器件表面覆盖一层厚度为1 mm的导热硅片,装配后导热硅片被压缩,使得屏蔽盒、导热硅片、元器件充分紧配,有良好的热接触。

3U VPX模块两侧的锁紧条选用5段式热传导专用的锁紧条,表面平整度可达到0.1,最大限度增大了与机箱导轨的有效接触面积,减小热阻。同时,锁紧条表面进行了黑色阳极氧化,能够高效地将模块其他区域的热量吸引至锁紧条,通过导轨传递至整个机箱。

3 组件的实现与测试结果

将PCB板加工生产,装配入组件,分别使用矢量网络分析仪、频谱仪、信號发生器进行测试,测试结果表明,该组件ACPR:≤-35 dBc,噪声系数:≤1.8 dB,收发切换时间:≤3.0 μs,各次谐波抑制以及发射功率,抗烧毁能力均达到指标要求,满足通信系统的实际要求。

4 结语

本设计主要研究基于VPX的多模多频段微波收发组件,通过前期调研和系统分析进行方案设计,验证方案的可行性,在保证组件性能的同时,实现通用化。根据指标要求,在指定频段内,组件满足接收噪声系数、ACPR、发射功率、收发切换时间、谐波抑制的要求,具有一定的创新性实际应用意义。

参考文献:

[1] 安效君.基于VPX的高速跳频信号接收处理平台设计[J].计算机与网络,2021(7):44-46.

[2] 赵旺.北斗导航授时终端模块的设计与实现[M].成都:电子科技大学出版社,2020:16-23.

[3] 吴喆.基于SIP的射频宽带收发前端关键技术研究[D].成都:电子科技大学, 2018.

[4] 张振,范如,罗俊.一种S波段平衡式限幅低噪声放大器设计[J].微电子学,2012,42(4):463-467.

[5] POZAR D M.微波工程[M].张肇仪,周乐柱,吴德明,等译.北京:电子工业出版社,2007.