一种应用于高精度流水线ADC 的差分参考电压电路*

池哲涵,黎 飞,刘颖异,唐旭升,苗 澎

(东南大学微电子学院,江苏无锡 214135)

1 引言

随着现代电子信号处理系统如无线通信、雷达、信号检测等领域的飞速发展,不同电子系统对工作频率与信号质量的要求越来越高,使得设计符合系统要求的模数转换器(Analog-to-Digital Converter,ADC)越来越重要,难度也越来越大。对于高精度流水线ADC来说,运放的有限增益带宽、比较器失调、电容失配等非理想因素会恶化ADC 性能[1-2],决定其量化标准的参考电压的精确程度也会直接影响ADC 的转换精度。由于有限的驱动能力,参考电压电路不可避免地会引入误差,并且这类误差难以通过校正技术消除[3-4]。

针对参考电压电路对高精度流水线ADC 性能的影响,本文分析了一种传统参考电压电路结构,并采用源级推挽输出与电压负反馈结构输出缓冲器优化设计了一种应用于18 位20 MS/s 流水线ADC 中的参考电压电路。

2 参考电路结构与工作原理分析

高精度流水线ADC 的参考电压电路一般基于高精度、低温度漂移系数的带隙基准电路进行设计[5-6],包括电平移位电路、输出缓冲器。参考电压电路驱动流水线 ADC 乘法数模转换电路(Multiplying Digital-to-Analog Converter,MDAC)中的开关电容以及为子模数转换电路(Sub-Analog-to-Digital Converter,Sub-ADC)中的比较器提供稳定的参考电压。

2.1 输出缓冲器电路结构

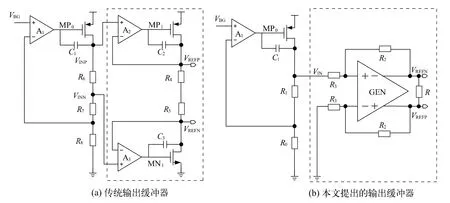

传统输出缓冲器结构如图1(a)所示[7-8],带隙基准电压VBG通过电阻分压负反馈结构的线性稳压电路输出高电压VINN与低电压VINP,并通过单位增益运放电路增大参考电压VREFP与VREFN的输出驱动能力。为了进一步提高输出缓冲器的驱动能力并消除传统输出缓冲器结构引入参考电压的非对称失调,采用的差分输出缓冲器结构如图1(b)所示,即基于源级推挽输出结构的全差分放大器电路设计,通过R2、R3分压构成电压负反馈产生高参考电压VREFP与低参考电压VREFN。

根据图1(b)输出缓冲器电路所示,AV为放大器GEN 增益,由放大器“虚短”、“虚断”特性可得:

图1 传统输出缓冲器与本文提出的输出缓冲器结构

根据式(1)可知,通过调整R2、R3电阻比例、输入电压VIN可以得到不同的差分参考电压。

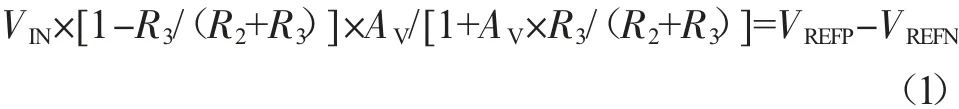

图2(a)为本文设计的采用源级推挽输出结构的全差分放大器电路结构简化图。在全差分放大器结构中,晶体管MP1、MP2与放大器A1、A2、晶体管MN1、MN2与放大器A1、A3形成反馈,构成推挽输出结构,该结构增大了输出的驱动能力。晶体管MN1、MN2与放大器A4构成共模反馈环路,稳定输出共模点。

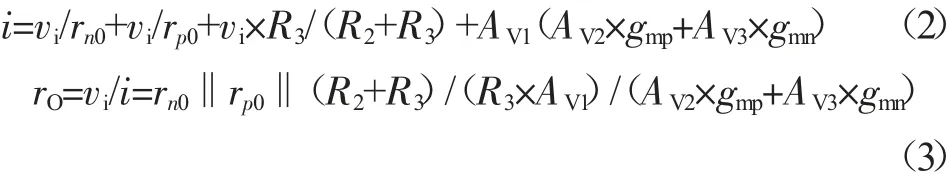

根据图2(b)输出缓冲器小信号电路分析该电路的输出阻抗,可得:

图2 输出缓冲器中放大器电路结构与小信号分析

其中,AV1为放大器A1增益,AV2为放大器A2增益,AV3为放大器A3增益;gmp为晶体管MP1跨导,rp0为MP1输出电阻;gmn为晶体管MN1跨导,rn0为MN1输出电阻。根据式(3)可以看出,输出缓冲器的输出阻抗大小主要取决于放大器的增益与输出晶体管的跨导。当放大器增益与晶体管跨导较大时,该结构能够极大地减小输出缓冲器的输出阻抗,增大驱动能力。

2.2 参考电路实现

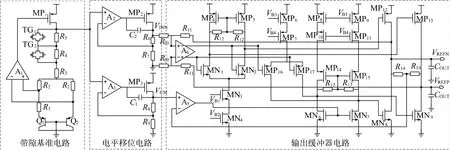

本文设计的参考电压电路为18 位20 MS/s 流水线ADC 提供参考电压,ADC 输入信号摆幅为4.32 V,共模点电压为3 V,参考电压电路正端参考电压输出5.7 V,负端参考电压输出0.3 V。参考电压电路总体结构如图3 所示。

图3 参考电压电路

带隙基准电路为参考电压电路提供精确带隙基准电压1.2 V。传输门TG1、TG2与R4、R5组成修调电路,通过修调电路保证带隙基准电压的准确性。电平移位电路将带隙基准电压转换为输出缓冲器所需要的输入电压与共模电压。输出缓冲器电路采用有源和无源结合的驱动方式[9],通过较大的负载电容稳定参考电压。从对电容充放电的角度来看,COUT存储的大量电荷快速补充MDAC 中电容上损失的电荷,抑制了参考电压的变化[10]。由于推挽结构中的反馈等效于增大了共源输出级晶体管MP12、MP13、MN8与MN9的跨导,减小了输出阻抗,保证输出电流能够补偿COUT上损失的电荷,增大了输出缓冲器对差分参考电压的响应速度。

3 仿真结果

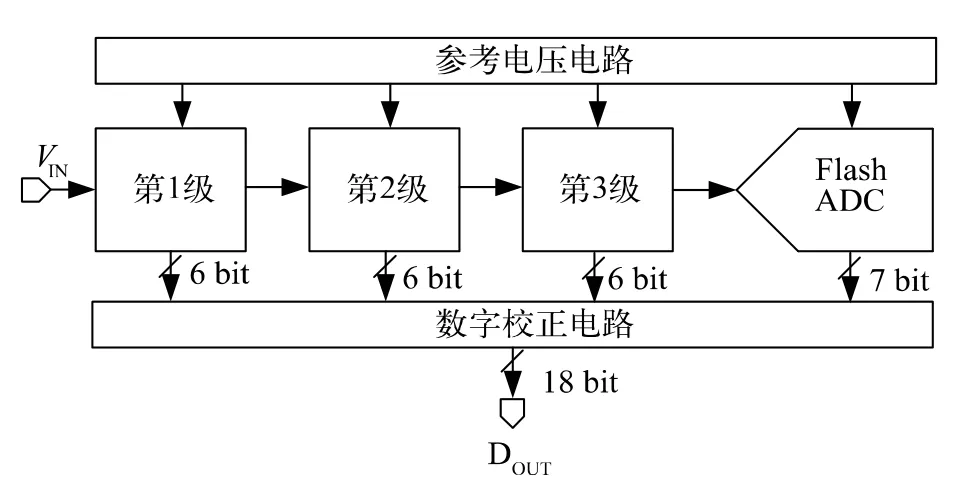

将本文设计的参考电压电路应用于一款18 位20 MS/s 流水线ADC 中,图4 为该ADC 功能框图,第一级为无采保结构6 位流水级电路,第二级和第三级精度为6 位,最后一级为7 位快闪结构。各级子电路输出经过数字校正电路处理后得到18 位量化输出。

图4 18 位20 MS/s 流水线ADC 功能框图

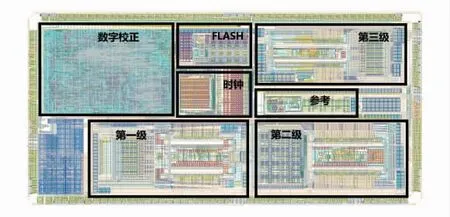

图5为采用180 nm 1P6M 5 V CMOS 工艺设计的18 位20 MS/s 流水线ADC 整体版图。整体ADC(包括焊盘)尺寸为2.50 mm×5.00 mm,其中参考电压电路尺寸为0.20 mm×1.05 mm。

图5 18 位20 MS/s 流水线ADC 版图

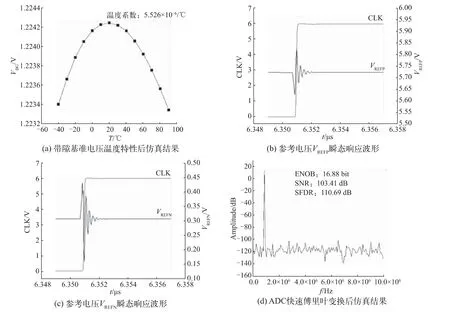

图6(a)为后仿真带隙基准电路电压输出波形的温度特性曲线,带隙基准电压稳定在1.22 V,-40~90 ℃范围内温度系数为5.526×10-6/℃。图6(b)为参考电压VREFP的瞬态响应波形,图6(c)为参考电压VREFN的瞬态响应波形,达到参考电压要求建立的精度所需要时间约为3 ns,满足参考电压建立速度要求,此时,参考电压电路消耗电流约为60 mA。应用所设计的参考电压电路,图6(d)为常温27 ℃时,18 位20 MS/s 流水线ADC 在20 MHz 采样频率下输入859.375 kHz 正弦信号的输出波形的快速傅里叶变换后仿真结果,ADC 的有效位数(Effective Number of Bits,ENOB)为16.88 bit,信噪比(Signal to Noise Ratio,SNR)为103.41 dB,无杂散动态范围(Spurious Free Dynamic Range,SFDR)为110.69 dB。

图6 后仿真结果

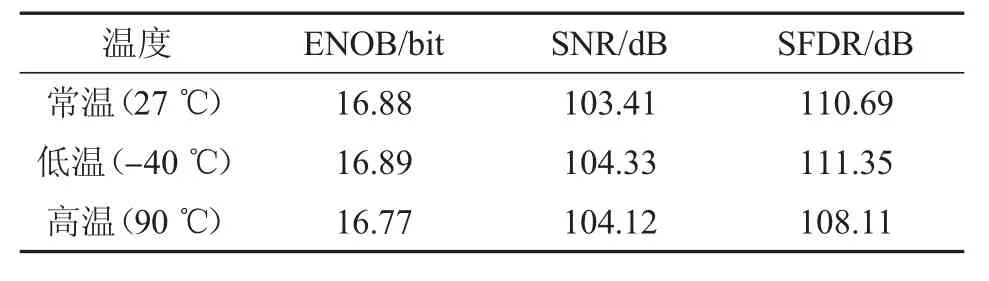

表1为低温、常温和高温情况下,18 位20 MS/s流水线ADC 在20 MHz 采样频率下输入859.375 kHz正弦信号的输出波形的快速傅里叶变换后仿真结果,从表1 可以看出,设计的参考电压电路能够满足该ADC 的性能要求。

表1 低温、常温、高温时ADC 性能后仿真结果

4 结论

本文采用源级推挽输出与电压负反馈结构,设计了一种低输出阻抗、高驱动能力的输出缓冲器,基于该缓冲器设计了一种差分参考电压电路,并应用于一款18 位20 MS/s 流水线ADC 中。通过有源与无源结合驱动稳定参考电压,其中带隙基准电压稳定在1.22 V,在-40~90 ℃内温度系数为5.526×10-6/℃,正端参考电压为5.7 V,负端参考电压为0.3 V。后仿真结果表明,该全差分参考电压电路能够满足所设计的高精度ADC 性能要求。