机载电子跨时钟域同步电路验证及可靠性分析

范毓洋, 邓智, 李子航

(1.中国民航大学 民航航空器适航审定技术重点实验室, 天津 300300; 2.中国民航大学 适航学院, 天津 300300)

随着机载电子设备复杂性增加、机载电子芯片设计规模的扩大,集成电路设计中跨时钟域信号传输也逐渐增多。而信号跨时钟域传输不可避免地会在电路中引入亚稳态[1],若亚稳态处理不当,则可能给电路带来数据丢失、位错、重汇聚等风险,造成设备关键功能的丧失或错误。如时钟检查电路功能丧失[2]、飞机显示图像异常、AFDX交换机数据错误等。更严重的是,若亚稳态沿信号通道上的寄存器级联传播,可能造成芯片烧毁的严重后果。如某航天器在为期一年多的地面测试中突然出现故障,经分析发现,航天器出现故障的原因是跨时钟域电路传输引入亚稳态,亚稳态传播导致片上大量MOS(metal oxide semiconductor)管同时工作致使电路板烧毁[3]。

目前电子设计技术的进步和一些机载电子设计部门的扩张,客观上也增大了设计中发生亚稳态问题的可能性。如一些硬件综合工具支持软件工程师使用高级语言设计硬件电路,与使用RLT代码进行电路设计相比,跨时钟域电路的亚稳态问题更容易被设计人员忽略[4]。另外,机载电子设计部门因为人员快速扩张,员工技术水平良莠不齐,不仅使得在设计过程中容易出现同步器功能设计错误,也使得同行评审质量下降,不能依靠评审有效发现问题。且随着特征尺寸的下降、新设计技术的出现[5],芯片电压下降、时钟频率和数据频率提高、同步路径增多,导致芯片中已有的功能正确的跨时钟域信号同步器的可靠性下降。若这些同步设计不经过可靠性评估而直接应用到航空领域,则会产生安全隐患。虽然目前跨时钟同步电路的问题存在的可能性增大,但是目前的机载电子的验证活动中,常常会忽视掉针对跨时钟域传输功能和可靠性的验证活动。

FAA Order 8110.105 A提及了机载电子硬件需进行最好或最坏情况下时序分析[6]。但是Order 8110.105 A及DO-254标准中都未具体提及如何验证跨时钟域时序问题[7]。而机载电子行业针对机载复杂电子硬件验证活动是基于需求开展的。时钟相关的需求一般只会描述各个时钟的时钟频率、占空比、抖动等内容。针对这些时钟需求的验证一般通过时序仿真和静态时序分析来进行覆盖。因此基于需求的验证及对应的验证方法并不能有效发现跨时钟域传输的问题。若未在设计活动中把概要设计或详细设计中明确的跨时钟域路径反馈到衍生需求,或未在概要设计中明确描述跨时钟路径及同步策略方法,则针对跨时钟域的验证活动很容易被忽视。若把亚稳态问题带到终端产品上去,则可能会使机载设备产生安全隐患。

因此,为了减少亚稳态问题发生概率,保证同步正确性,需要对跨时钟域电路可能带来的问题(同步器可靠性问题[8-9]、同步器结构问题[5,9-10]、跨时钟域数据传输协议问题[5,11]、重汇聚[5,12-13]问题)进行全面验证。而跨时钟域信号验证通常只能对多个实际电路进行长期测试以发现亚稳态隐患。但由于亚稳态造成的故障具有偶发性和不可重现性,极大增加了电子硬件的研制时间和验证成本。如果直接使用国外专用CDC分析软件(如spyglass,questa-CDC),在高安全等级机载电子电路验证活动(例如DAL A,B)中需承担工具成本及使用此工具所需的工具鉴定[14]活动所带来的时间和经济成本。另外,由于航空单粒子问题,常常要求使用三模冗余对跨时钟域模块进行加固设计[15],但目前的专用CDC分析软件不支持三模跨时钟同步电路验证,容易出现错误的验证结果,给验证活动带来问题。

针对此情况,本文对跨时钟域同步可能存在的问题开展全面的验证方法研究,提出了一套基于传统FPGA(field programmable gate array)设计工具、功能仿真工具的RTL级验证、板级加速测试和计算评估相结合的跨时钟域验证的解决方法。该方法有较强的实用性和适用性,能够有效弥补专用工具缺陷,在机载电子设计早期发现并评估潜在的跨时钟域传输风险,达到降低安全隐患的目的。

1 方法概述

完整的跨时钟域同步电路验证及可靠性分析方法主要包括RTL级验证、板级加速测试、计算评估三部分,具体验证流程如图1所示。

图1 验证流程图

RTL级验证(包括结构分析、协议验证、重汇聚验证)旨在证明跨时钟域信号传输所使用的同步方法功能正确,保证了单比特的使能信号或多比特的数据信号能传输到目的时钟域,且不出现数据丢失。

板级加速测试通过构建加速亚稳态生成环境获取亚稳态相关数据,并根据板级测试所得亚稳态相关数据计算出亚稳态参数值。

对于航空机载设备电路的设计,需对这些功能正确的同步电路的可靠性进行分析。为评估电路可靠性,需通过亚稳态参数计算同步电路的MTBF(mean time between failure)。从而最终判断出设计中使用的同步策略是否可接受。

如果在RTL级验证或计算评估中发现问题应及时提出问题报告,依据问题报告提出更改请求,增加对应的衍生需求。并依据需求修改对应的概要设计及设计代码。最后将修改后的代码重新进行RTL级验证、板级加速测试、MTBF计算评估,如果发现问题应继续提出问题报告并修改直至得到可接受的同步策略。

2 RTL级验证

在电路RTL设计及功能仿真完成后,需要针对跨时钟域信号进行结构分析、协议验证和重汇聚验证,作为静态时序分析的补充。其中结构分析用以确保同步电路具有正确的同步电路单元,协议验证对同步电路是否满足相应的传输协议进行检查,重汇聚验证判断数据在目的时钟域内是否存在重汇聚问题。

2.1 结构分析

能够将数据正确跨时钟域传输的同步电路(如握手协议、异步FIFO等同步电路)都包含至少连续2级且中间无组合逻辑运算的寄存器级联的结构单元,本文把其定义为同步单元(或电平同步电路),如图2所示。

图2 同步单元

结构分析主要确定跨时钟域路径上是否含有该同步单元的结构以降低亚稳态传输概率,进而确定设计所采用的同步电路结构或方法,可通过使用常用的EDA工具来快速分析。如在Xilinx的Vivado开发环境下,对RTL级代码进行综合后可得到原理图,在原理图上同时选定不同时钟域的时钟信号,便可快速定位出数据跨时钟域交互模块。定位出CDC设计模块后,便可分析该模块所采用的同步策略、模块是否含同步单元、同步路径是否含组合逻辑。如果没有正确的同步电路结构,则说明需要增加合适的同步电路使数据正确传输。

2.2 协议验证

电路具有正确的同步电路结构,并不能保证该数据可以正确地传输到目的时钟域,还需满足相应的传输协议。为快速验证电路是否符合传输协议,可使用传统的仿真软件,并在基于断言的仿真测试平台上进行动态仿真。为模拟出真实环境,保证数据在任何情况下都满足传输协议,动态仿真的输入激励须覆盖需求规定的所有情况。在进行动态仿真时,如果传输的数据在某一时刻不满足相应的传输协议,则断言宣告失败,说明该数据不能被正确地跨时钟域传输,需重新修改同步策略直至验证通过;如果断言成功,则表示该同步电路能正确地将数据传输到目的时钟域。

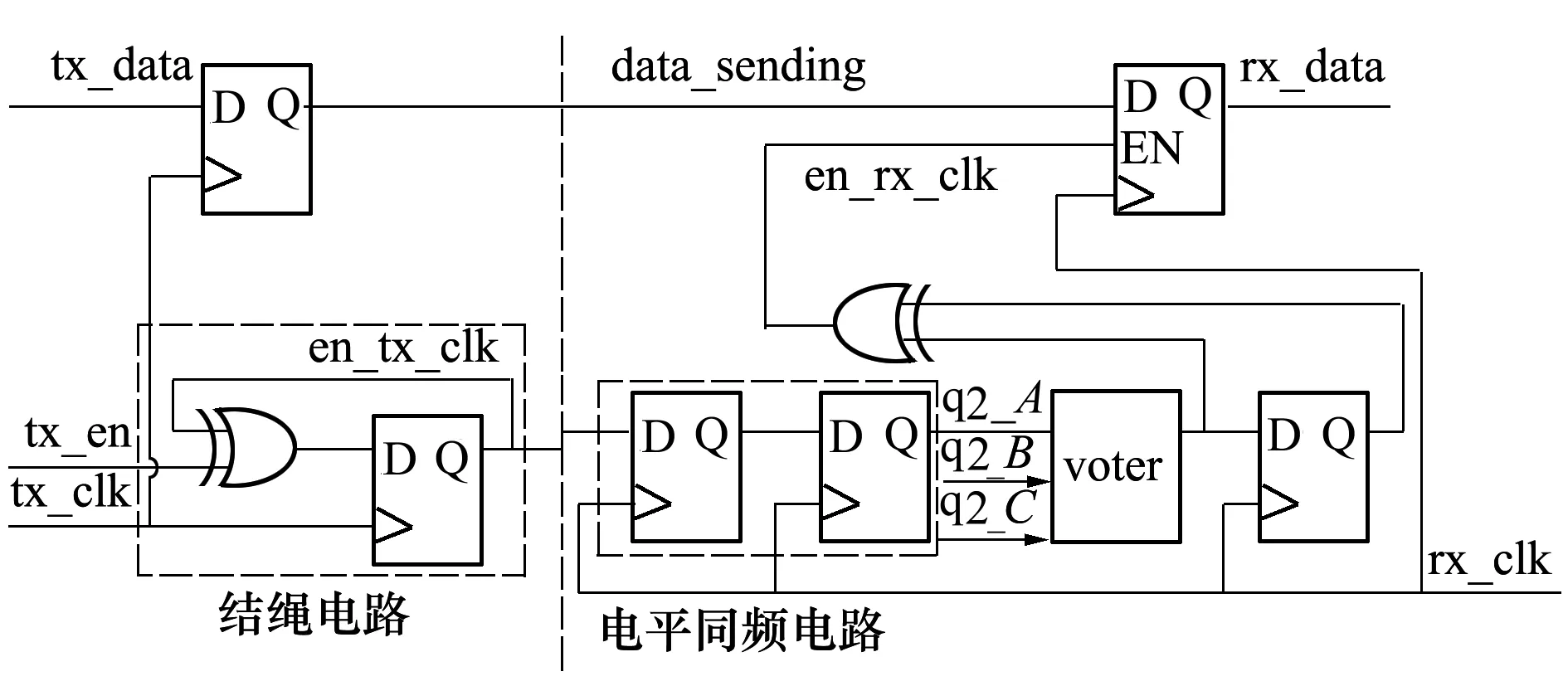

本文以适用于三模冗余的多周路径(multi-cycle-path,MCP)传输电路为例,说明CDC电路的传输协议验证过程。适用于三模的MCP电路如图3所示,发送电路在更新数据tx-data的同时发出脉冲信号tx-en。tx-en经过结绳模块后变为电平信号en-tx-clk。q2-A为同步后的en-tx-clk信号,q2-B、q2-C则为另外2个冗余电路的电平同步后信号。3个信号经过voter表决后通过边沿检测生成en-rx-clk信号,并把其作为data-sending的读时钟域接收寄存器的使能信号。

图3 多周路径传输路径电路

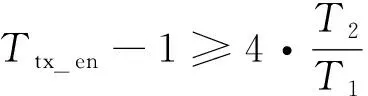

假设发送时钟域中的脉冲信号间隔为nT1(T1代表发送时钟周期),考虑到亚稳态的情况下,接收时钟域中的数据信号必须经过1个发送时钟周期和至少4个接收时钟信号的上升沿,才能保证该组数据的正确传输,即nT1>4T2+T1(T2代表接收时钟周期)。因此,使能信号tx-en的间隔应满足公式(1)。

(1)

式中:Ttx-en-1表示tx-en信号下降沿到下一个tx-en上升沿之间包括的最少发送时钟周期,在此期间tx-en应保持低电平。

发送数据tx-data在整个数据发送过程中均应保持稳定,协议可以表示为公式(2)。

(2)

Tdata表示发送数据tx-data需要在多少个发送时钟周期内保持稳定。

根据上述分析,使CDC数据正确传输发送数据和脉冲信号间隔断言表示如下,仿真波形如图4所示。

property DATA-SEND;

endproperty:DATA-SEND

property TX-EN;

endproperty:TX-EN

图4 电路断言波形图

2.3 重汇聚验证

当数据经过不同的同步电路后,无法保证同步电路的路径、环境(如时钟相位、寄存器电压、电磁干扰)及器件工艺参数完全相同,因此经过不同同步电路的传输数据可能会出现不可预测的提前或延迟。在目的时钟域内,如果经过不同跨时钟域路径传输的数据进行组合逻辑运算,可能会造成整个电路的功能错误。为避免电路出现无有效保护的重汇聚运算,须对设计进行亚稳态重汇聚验证。重汇聚验证可基于传统仿真工具,通过随机注入延迟来判定电路对亚稳态的容忍度。如果进行延迟注入后仿真结果与预期一致,则表明该电路符合需求。与协议验证一样,重汇聚验证需要仿真测试平台的输入激励覆盖需求规定的所有情况。

下面描述的亚稳态注入方案与已有研究的注入方法相比[12]主要区别是固定了注入随机延迟的变化频率,注入随机延迟的时机由状态机进行控制。该方法保证了进行一次使能信号传输时,随机延迟的注入不会突然变化而导致单比特使能信号缩短。相比于已有研究论文,其能应用在如对接收使能信号有长度要求(一般为2个接收时钟长度)的三模冗余电路。需注意的是,一般情况下在目的时钟域的重汇聚是不允许的,但在抗单粒子翻转使用的三模冗余设计中,不同同步路径会在三模投票电路处出现计划内的汇聚点[13],一些专用的跨时钟域分析工具如Questa CDC可能误报该错误。使用本文的亚稳态注入方法,可以对该投票电路功能在翻转场景下是否失效进行动态判别。避免一些静态跨时钟域分析工具直接对该汇聚现象报错的情况出现。

图5 亚稳态注入电路

如图5所示,亚稳态注入位置选取在跨时钟模块信号传输完成后三模冗余投票之前的节点,本设计使用状态机确保3个亚稳态注入点注入亚稳态时,该信号不会被截短导致三模冗余验证不能通过。且在动态仿真过程中,为保证验证的全面性,需要收集功能覆盖率情况。确认在验证过程中覆盖了亚稳态的一路注入、两路同时注入、三路同时注入的情况。使验证活动更为完整可靠。

协议验证和重汇聚验证可以使用相同的输入激励,因此可以在一次仿真验证过程中同时检查电路的传输协议和重汇聚问题。

3 加速测试和可靠性分析评估

本节通过构建加速亚稳态的生成和采集电路获取亚稳态相关数据,并根据板级测试所得亚稳态相关数据计算出亚稳态参数值,使用该亚稳态参数值,就可以计算出电路全部跨时钟域路径的TMTBF(平均无故障时间)值。

3.1 加速测试方法

跨时钟域传输时通过单触发器后发生亚稳态的概率常使用公式(3)进行评估[15]:

(3)

式中:tτ为亚稳态解决时间,即预留给触发器使其从亚稳态恢复到稳定的时间;τ为触发器的亚稳态解析时间常数;Tw为亚稳态窗口时间常数;fc为设计的接收时钟频率;fd为设计的异步信号变化频率,即输入的异步信号翻转率。

对于具体的电路设计来说,参数fc,fd和tτ已知。因此要对MTBF进行计算的关键是确定触发器的亚稳态参数Tw和τ。

对公式(3)两边取自然对数,得到如下公式:

(4)

易知方程(4)是一条直线,其自变量为亚稳态决断时间tτ,因变量为ln(TMTBF),直线斜率k为1/τ,截距为-ln(Tw·fc·fd)。得到τ的计算公式,如公式(5)所示

(5)

得到Tw的计算公式,如公式(6)所示

(6)

所以可以通过改变tτ,测得到不同tτ下的TMTBF值,拟合出tτ-ln(TMTBF)直线,从而算出Tw和τ。目前半导体器件的亚稳态参数测试方法都是基于该测试理论。

基于该测试理论,FPGA芯片厂商推荐使用的亚稳态参数的测试电路为半周期测试电路[8],通过改变时钟周期的频率改变tτ。本文推荐使用器件的时间管理模块以实现tτ更精确的控制,以便获得更多更广泛的数据和更高的测试效率。亚稳态参数测试需采集大量的亚稳态数据,为计算TMTBF值,需测得亚稳态发生次数和其对应的时间。在设计亚稳态采集电路时,测试前规定亚稳态采集停止次数S。开始亚稳态采集时,计时计数器开始计时,当亚稳态采集次数计数器达到亚稳态采集停止次数S时,使计时计数器停止,并把该时间T记录下来。S/T即可计算得出采集到2次亚稳态的平均时间间隔。通过改变tτ,经过不同次的测试计算获得对应的TMTBF值。需注意的是,测试时要使亚稳态采集点在FPGA上的位置尽可能分散。

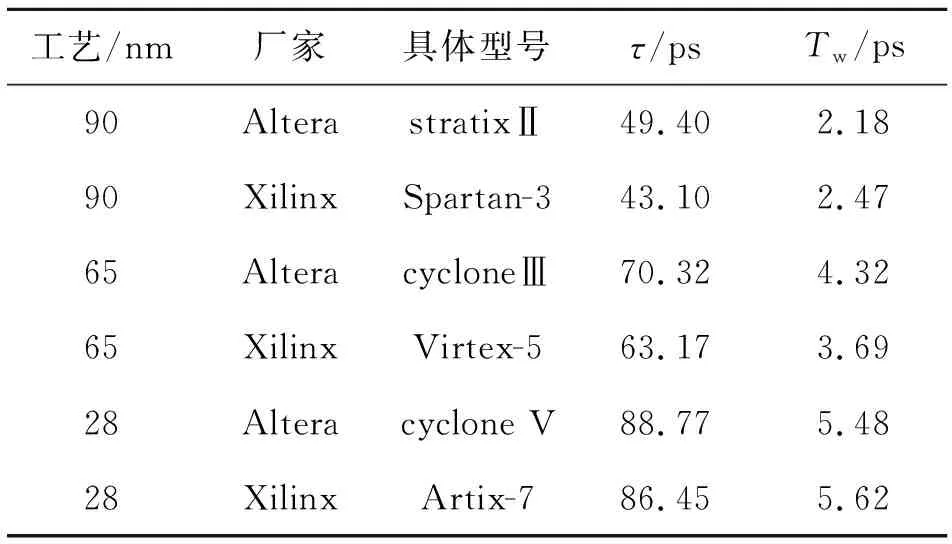

为方便在使用某些器件时进行跨时钟域的可靠性评估,本文对6种典型FPGA芯片的亚稳态相关参数进行采集计算。在不同采样点多次规定次数进行亚稳态采样后,对数据点进行最小二乘法直线拟合,绘制出6种典型芯片亚稳态参数采集Matlab图(图中tτ和TMTBF的单位为ps)如图6所示。

图6 不同芯片亚稳态参数采集图

对多组数据拟合成直线,计算得到的亚稳态参数值如表1所示。

表1 被测芯片亚稳态参数值

3.2 计算评估

不同的同步策略解决亚稳态的核心原理都是增加亚稳态的解决时间,核心电路为同步单元结构。其中双级同步单元的MTBF计算公式如公式(1)所示。

当双级同步单元不能满足MTBF的需求时,可以提高同步单元的串联级数来增大亚稳态的实际解决时间。多级触发器风险评估公式(7)[16]

(7)

式中,M为一个同步单元中寄存器个数。

FPGA整体的同步电路的MTBF值由设计中所有的跨时钟域同步单元决定。一个同步单元失效率F(Pn)为1/TMTBF(M),Pn表示第n个同步单元。整个设计由亚稳态导致的失效率是把所有同步链的失效率相加,如公式(8)所示。假设FPGA整体设计含N个同步单元,其MTBF计算公式如公式(9)~(10)所示:

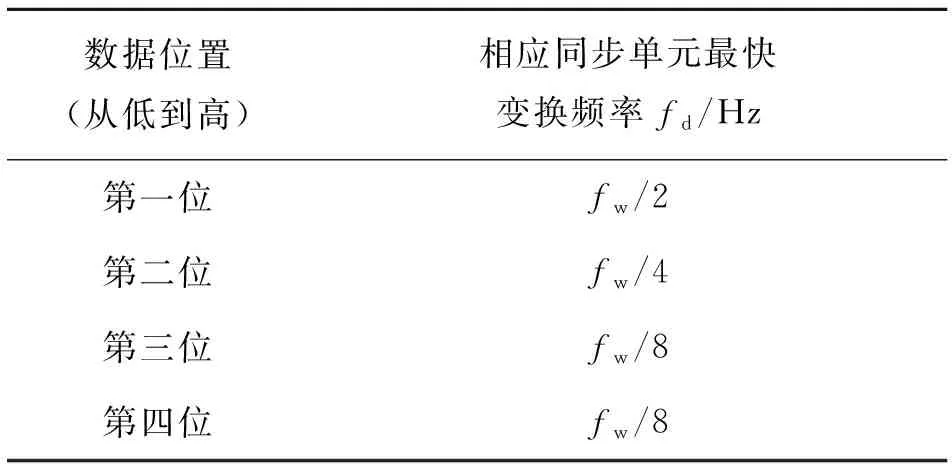

在计算跨时钟域同步电路可靠性时,需关注两点:第一是同步单元数目的确定;第二是对数据变换速度fd的确定约束。在确定同步单元数目时,要注意每种同步电路含有的同步单元的个数不同,同步电路与其含有的同步单元不是一一对应关系(如握手同步策略,异步FIFO同步策略)。在确定公式使用fd数值时,如果数据变换速度fd未知,一般fd可按照发送时钟域的时钟频率fw估计,这样计算出的MTBF值可认为是保守的可靠性值。但在某些场景可对fd进行更精确约束时,建议使用更精确的方法约束fd最高变换频率,以求得更符合实际的MTBF值。下面举例说明如何确定计算MTBF所需的同步单元的个数N和fd的值。假设一个电路设计中含有一个异步FIFO,其指向数据存储器的地址采用二进制码编写。其中,异步FIFO中的写满标志判断需要把读地址同步到写时钟域,读空标志需要把写地址同步到读时钟域[17]。当读写地址码进行跨时钟域传输时,需把二进制编码转化为格雷码。若地址总线位宽为W,由于读写地址都要同步,因此该异步FIFO中具有2W个同步单元,即N=2W。确定N之后,需确定约束每个同步单元的fd。对于地址总线为W的异步FIFO,存在2W个写地址,其中最高位为状态位,2W-1个地址对应实际存储器的地址。自然二进制码转换成二进制格雷码,其法则是保留自然二进制码的最高位作为格雷码的最高位,而次高位格雷码为二进制码的高位与次高位相异或,而格雷码其余各位与次高位的求法相类似。经分析计算,第n位格雷码最快变换频率如公式(11)所示。

(11)

以W=4为例,代入公式(11),可得到各同步单元最快变换频率表。

表2 4位格雷码同步单元最快变换频率表

依据表2中的各同步单元最快变换频率fd,便可以使用公式(7)进行单个同步单元TMTBF计算。之后使用公式(10)进行该异步FIFO的TMTBF计算。

通过计算所得的MTBF值即可判断同步电路是否符合可靠性要求。如不符合,需修改同步电路设计,增加相应同步单元内寄存器的级数。

4 结 论

本文介绍了一种适用于机载复杂电子硬件的基于传统工具的RTL级验证、板级加速测试和计算评估相结合的跨时钟域验证及可靠性评估方法,可以在设计早期发现三模场景和普通场景下的跨时钟域信号的隐患。对于含跨时钟域同步电路的电子设计,电路验证应关注跨时钟域路径上的同步电路结构,数据传输要求,目的时钟域重汇聚等问题。

对于应用在DAL A/B的机载复杂电子硬件的跨时钟域同步电路,则需在RTL级验证通过后,对亚稳态参数未知的芯片进行实际板级加速测试,最后根据测试结果计算评估其TMTBF值,判断同步器的可靠性是否符合需求。另外,本文提供了Altera和Xilinx公司的共6款不同特征尺寸的亚稳态参数测试参考值,使验证人员能更方便快捷地进行该器件的跨时钟域可靠性评估计算。建议该方法可作为静态时序分析工作的补充,共同完成对电路的时序分析工作。