基于FPGA 的船只目标ISAR 实时重聚焦处理实现

田 坤,刘 霖,曹 越,江 率

(1.中国科学院空天信息创新研究院,北京 100094;2.中国科学院大学电子电气与通信工程学院,北京 100094)

随着海上船只目标数量逐年增加,对于探测装备的高分辨成像、识别和分类要求越来越高。相比于传统的光学成像,合成孔径雷达(Synthetic Aperture Radar,SAR)[1-2]成像具有不受气候变化影响、能够全天时工作的独特优势,因此在雷达探测领域受到广泛应用。然而在SAR 对船只目标成像过程中,由于船只复杂的运动特性及其与雷达之间的相对运动令方位回波数据的相位出现相对偏移,使得目标成像结果散焦,从而导致成像分辨率相对于岛屿、港口、礁石等静止海上目标大幅下降[3]。

目前,针对船只SAR 图像散焦问题,大体存在两类自聚焦方案:参数化自聚焦[4]和非参数化自聚焦[5]。其中,参数化自聚焦方法基于现有的回波模型对原始数据提取所需参数并用于散焦相位误差校正。具体参数化自聚焦算法包括子孔径相关算法[6]、多子孔径自聚焦算法[7]和三阶多项式傅里叶变换算法[8]。子孔径相关算法通过把整块图像分割为互不重叠的子孔径图像,并运用互相关法估计相位误差进行校正,然而该方法只对二次相位误差项有效,当高阶误差较大时,子孔径相关算法效果下降严重。多子孔径自聚焦算法在前一算法基础上,进一步将子孔径相位误差合成,进而对整幅图像进行补偿,但是计算开销严重。三阶多项式傅里叶变换则是对三次相位误差进行估计,具体是采用Hough变换估计距离走动率和径向速度,并通过相位补偿法校正距离徙动,可以更快估计目标运动参数。非参数化自聚焦算法不需要参数化的数据模型即可校准相位误差,具体包括相位梯度自聚焦算法(Phase Gradient Autofocus,PGA)[9-12]、基于最小熵准则的自聚焦算法[13]、秩一相位估计算法(Rank One Phase Estimation,ROPE)[14]等。PGA 是工程中较常采用的相位校正方法,该算法通过估计图像中孤立强点目标的相位误差梯度求解相位误差,并采用迭代方法进行修正。但是在相位梯度估计中对信号多普勒的补偿不够准确,结果存在误差。ROPE 采用交替迭代对信号进行估计,可以更精确地估计相位误差,缺点是该算法只能应用到每个距离单元只有一个特显点的信号模型。

现今,现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)[15]因其硬件运算资源丰富、可并行处理、功耗低、运算速度快等诸多优点而在实时信号处理系统中大量使用。现有的SAR 图像自聚焦方法存在一个普遍的缺点,算法复杂程度高,FPGA 硬件实现难度太大,无法在单片FPGA 上进行实现。

该文针对SAR 图像船只目标散焦难点问题,结合实际FPGA 硬件平台给出一种可在单片FPGA 上实现的低复杂度实时重聚焦处理优化算法。该方法基于逆合成孔径雷达(Inverse Synthetic Aperture Radar,ISAR)成像原理进行重聚焦处理,主要分为两部分,首先,对距离向数据作包络对齐处理;然后结合PGA 算法和ROPE 算法的优点进行相位校正,实现聚焦补偿。接着依据FPGA 并行流水工作特点,对所提方法通过高层次综合(High-Level Synthesis,HLS)[16-18]设计IP core 并对其优化,最后使用硬件描述语言完成实时重聚焦处理系统在FPGA 硬件平台上的搭建。采用实测SAR 雷达成像数据对所设计系统进行验证,结果满足指标要求。

1 ISAR实时重聚焦处理算法

ISAR 实时重聚焦处理算法流程如图1 所示。

图1 ISAR实时重聚焦处理算法流程图

ISAR 实时重聚焦处理算法大体可分为两部分:包络对齐和初相校正。其中,包络对齐是将原始SAR 图像沿距离向对齐以补偿时延误差;而初相校正则是在方位向对目标徙动所产生的多普勒偏移进行校准。下面将对上述算法进行简要介绍。

1.1 积累互相关法实现包络对齐

目前,SAR 雷达多为正侧视工作模式,当船只以缓慢速度运动时,雷达接收到的相邻回波信号间的距离偏移量很小,因此得到的一维距离像包络十分相似。更准确地说,它们的互相关系数通常可达到0.95 以上[19-20]。对于此种类型的船只回波信号进行包络对齐,传统的相邻互相关法即可对该方法通过计算相邻回波间的互相关函数,并寻找其峰值对应的补偿量完成相邻回波对齐。互相关函数计算公式如下:

其中,R(s)为互相关函数,是相邻回波,r为回波距离。但该方法在使用过程中会出现包络漂移和突跳误差等问题。因此,在该方法处理后添加修正步骤,具体方法为在相邻互相关法对准基础上,先对回波信号进行积累,然后将其与基准系数相乘,该文将该系数设为0.95。该修正操作一方面可以避免突跳误差带来的影响,另一方面也可有效抑制包络漂移现象。

1.2 PGA-ROPE算法实现初相校正

PGA 算法采用了线性无偏最小方差准则,得到误差相位的一阶导数ϕε(t)的估计值为:

式中,s(t)、s*(t)表示回波信号与其复共轭,K表示距离单元数量。对公式求积分可得到相位误差。

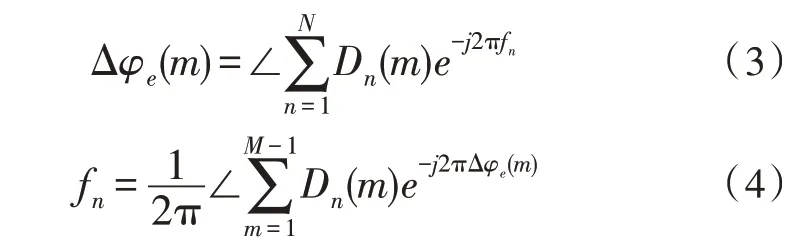

ROPE 算法通过交替迭代计算相位一次差分及多普勒频率。

其中,Δφe(m)表示一阶相位误差,fn表示多普勒频率,n是距离单元序号,n=1,2……N,N为每个脉冲包含的距离单元总数,m是回波脉冲个数,m=1,2……M-1,M为成像处理的脉冲总数,Dn是相位差分矩阵。

传统的PGA 算法在处理过程中仅通过循环移位操作将回波信号频谱搬移至多普勒零点进行校正,未考虑多普勒频移对相位校正所带来的影响,因此校正后的相位仍存在一定的剩余误差。而ROPE 算法在估计时考虑多普勒频率,因此能够较准确地消除多普勒频移的影响。可是,ROPE 算法只适用于特定的工作模型,应用范围有限。结合二者的优点,设计出一种PGA-ROPE 算法,该算法基于PGA算法框架计算出一阶相位误差,再使用ROPE 算法精确地估计相位误差,从而大大提高了校正精度。对校正完成的数据作方位向FFT 成像处理得到重聚焦图像。

2 ISAR实时重聚焦处理系统软件设计

ISAR 实时重聚焦处理系统主要包括四大部分:数据收发模块、数据存储模块、重聚焦处理模块和控制模块。具体处理系统框架如图2 所示。

图2 ISAR实时重聚焦处理系统的框架

首先在接口部分通过Aurora 接口接收数据进入FPGA;然后在ISAR 成像处理部分进行处理,根据数据包协议对图像数据与参数进行分离与预处理操作,再将图像数据存储至DDR,参数存储至RAM;接着基于参数信息提取切片数据,作ISAR 成像处理;最后,通过Aurora 接口将处理后的结果输出。在FPGA 处理过程中,所有数据及状态信号在控制部分调度下通过AXI 总线与各子部分进行交互。ARM 和FPGA 之间的信息传递通过共享DDR 实现。具体各模块设计将在下面依次说明。

2.1 数据接口模块

FPGA 通过光纤接口实现与外部的数据交换,考虑到所应用场景为实时处理系统,需要满足低延迟、高带宽、高速率的性能要求,数据接口选择使用Aurora 协议,具体结构设计如图3 所示。Xilinx 公司提供IP核供用户使用。通过配置IP core,传输位宽为256 bit 的数据,使用4 个GTY 通道,每个通道速率为5 Gbps,工作模式为全双工模式。由于传输数据和系统内部处理数据位宽不一致,因此在接收之后与发送之前,需要增添FIFO 用于数据缓存和位宽转换。

图3 Aurora接口示意图

2.2 数据存储模块

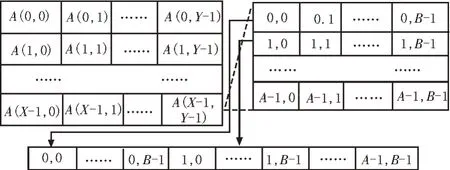

在ISAR 实时重聚焦处理实现过程中涉及到数据存储和转置操作,少量参数信息存储至RAM,大量数据存储至DDR 中。数据处理有行进列出,列进行出,为了提高数据存储效率,在设计时采用分块矩阵设计的方式。具体的分块方式如图4 所示,将数据矩阵划分成X×Y个子矩阵,每个子矩阵中有A×B个数据,将每个子矩阵按行展开存入DDR 的一行中,在进行数据转置时DDR 的跨行写和读操作次数近似相等,这种方法让距离向的数据和方位向的数据访问效率实现一种平衡,从而提升DDR 读写的总体效率。

图4 分块子矩阵示意图

2.3 数据处理模块

2.3.1 预处理单元

使用Verilog 语言实现数据、参数分离单元。根据传输协议,读取传输数据包的指定位置数据,提取参数信息片段和图像数据片段,并将其分离。分离后的各个参数存储到RAM 中的不同地址;再检测特定数据帧头序列,检测到之后读取图像数据并写入DDR 指定地址进行存储。

2.3.2 切片数据提取单元

使用HLS 设计IP core 实现切片数据提取单元。从RAM 中读取参数信息,根据参数从DDR 中提取需要处理的切片数据块,并将切片数据块补零至512×1 024,补零结果写入到DDR 中。输入输出接口为实数、虚数组合的复数数据类型,需要使用数据打包指令进行打包,数据读写接口设计成AXI 接口实现与AXI 总线连接。

2.3.3 包络对齐单元

使用HLS 设计IP core 实现包络对齐单元。包络对齐分为插值处理和包络对齐两部分,分别设计两个IP core,实现对应功能。数据均从DDR 进行读写,接口设计成AXI 接口。一次插值处理和对齐校正只处理一个距离向数据,整个过程为迭代循环处理,要提高处理速度,只能缩短每次迭代运算时间,因此,采用数据流优化指令增大数据吞吐量和数据流率。

2.3.4 初相校正单元

使用HLS 设计IP core 实现初相校正单元。根据算法原理设计结合算法IP core 进行初相校正。因为算法为迭代循环处理,所以使用数据流优化指令进行优化。数据输入输出仍需要从DDR 中读写,接口设计为AXI 接口。

2.3.5 成像量化单元

使用HLS 设计IP core 实现成像量化单元。对数据在方位向作FFT 进行成像处理,再做量化处理,量化精度为32 位。量化完成的数据传递到Aurora 接口模块。整个过程为循环处理,采用数据流优化。DDR 读取数据设计为AXI 接口,输出端口设计为AXI Stream 接口。

2.4 控制模块

使用Verilog 语言编写程序实现控制模块。控制实时重聚焦处理系统各个模块之间的协同工作,完成控制数据流向、地址分配、状态转换。控制模块接收各个模块的完成信号,状态机控制切换至下一个状态,发出模块处理的控制信号,同时传递给各个模块需要的参数和RAM、DDR 读写数据的起始地址。

3 ISAR实时重聚焦处理系统硬件验证

ISAR 实时重聚焦处理系统在Xilinx 公司生产的Virtex Ultrascale+系列FPGA 芯片XCVU9P 上实现。Virtex UltraScale+系列芯片提供了最高的性能和集成能力,包括最高的串行I/O 和信号处理带宽以及最高的片上存储器密度。作为功能最强的FPGA 系列,UltraScale+系列FPGA 芯片完全可以实现ISAR重聚焦处理需求。

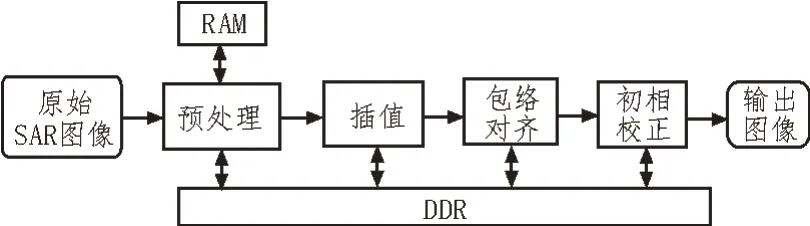

ISAR 实时重聚焦处理系统硬件实现数据处理流图如图5 所示。

图5 数据处理流图

ISAR 实时重聚焦处理系统经过综合实现后,资源使用情况统计如表1 所示。

表1 资源使用统计表

通过上表可以看出,该算法可以在一片芯片上进行实现,总功率约为7.997 W,其中动态部分占67%,约为5.326 W,静态部分占33%,约为2.671 W,ISAR 实时重聚焦处理系统的功率很低。

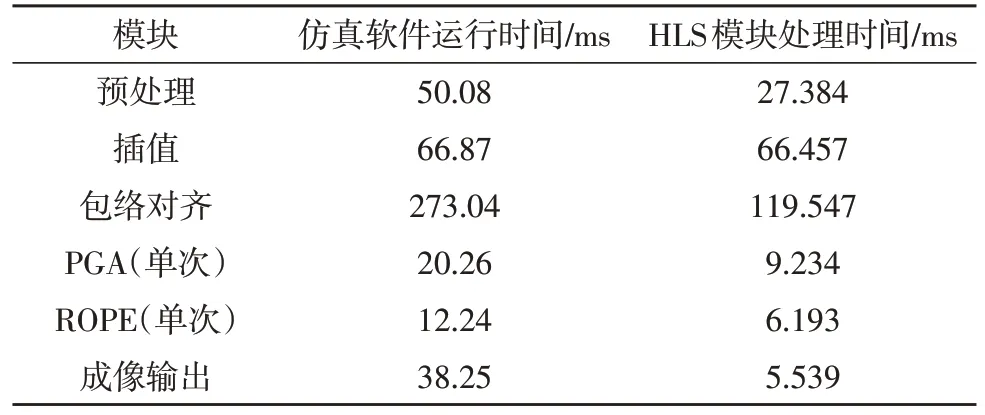

对系统实时性进行分析,仿真软件运算处理时间与HLS 编写模块所用时间对比如表2 所示。处理切片数据距离向点数为512,方位向点数为512。仿真软件运算处理平台为Intel Core i7-6700,主频3.4 GHz,内存48G,系统Window10 64 位。

表2 模块运算处理时间对比

系统处理一个切片数据需要进行一次预处理,一次插值,一次包络对齐,4次PGA和5次ROPE,总共耗时约为0.3 s,仿真软件处理一次耗时约为0.58 s。相比仿真软件处理平台,所设计系统运算处理速度更快,可以达到实时性要求。

对重聚焦效果进行对比,使用实测1 m 分辨率图像数据进行处理。与原始SAR 图像相比,船只目标经过重聚焦处理,轮廓结构清晰可见,重聚焦效果良好,解决了船只目标SAR 图像散焦的问题。

使用图像熵值作为衡量图像聚焦程度的标准,图像熵值越大,聚焦效果越好,经计算,不同图像熵值对比结果如表3 所示。从表中可以看出,经过重聚焦算法处理之后,图像熵值明显提升。

表3 图像熵值对比

4 结论

在船只目标SAR 成像过程中,散焦问题会使成像质量受到严重干扰,该文在传统聚焦方法的基础上,给出一种可应用在FPGA 硬件平台上的重聚焦处理算法。依据此方案设计了一套完整的实时重聚焦处理系统。该系统可在单片FPGA 上实现,并且功率低。测试结果表明,ISAR 实时重聚焦处理系统重聚焦效果良好,同时满足实时处理所需要求,验证了系统方案的可行性。目前,该系统已成功应用于某处理平台。