基于FPGA和PCIe总线的电子星模拟器设计

唐永学,朱桂梅,聂瑞千

(1.北京轩宇空间科技有限公司,北京 100190;2.丹娜(天津)生物科技股份有限公司,天津 300467)

0 引言

随着近期“嫦娥”系列月球探测器、中国空间站核心舱、“天舟”系列货运飞船、“神舟”系列载人飞船的陆续成功发射,证明中国航天技术水平走在了国际前列。航天事业的步伐不断的前进,对卫星执行任务的要求越发复杂、任务完成精度越高[1]。为了完成更为精确地姿态确定,星敏感器作为目前使用最广泛、测量精度最高的天体敏感器,可以为飞行器提供精确的三轴姿态信息[2]。

星敏感器自身存储有全天区的导航星图[3],在工作过程中,通过其光学系统拍摄所对应的天球上的恒星,得到观测星图,将观测星图与导航星图进行特征匹配,从而得出卫星本体的坐标系的姿态。姿态确定的输入信息是姿态敏感器的测量数据,输出是卫星的三轴姿态参数[4]。

为满足高精度的姿态测量要求,国内外的卫星控制系统都采用高精度星敏感器进行姿态测量。如国外的微型X 射线太阳光谱仪卫星[5],三轴姿态控制精度为0. 004 2°、0. 011 7°和0. 006°,姿态测量精度为0. 001 83°/s、0.007 3°/s 和0.001 05°/s 。国内的资源三号卫星[6],控制系统稳定度达到5×10-4°/s,惯性姿态测量精度达到了0.005°。电子星空模拟器是与星敏感器配套的地面测试设备。它可根据输入的惯性姿态数据,实时生成与该姿态对应的星图,按照接口时序向星敏感器线路盒输出,使星敏感器线路获得所需的电子图像,从而达到实时动态模拟在轨星敏工作过程。

文献[7]主要介绍了高精度静态星模拟器的组成、工作原理,完成了光学系统设计以及星点板设计。文献[8]设计了一种基于长焦距高成像质量准直光学系统的甚高精度动态星模拟器。文献[9-10]主要设计的是基于CCD的星图模拟器,上述文献均是侧重于光学系统的研制。文献[11]设计了一款电子星空模拟器,但是主要侧重于星图生成研究,未对硬件原理做介绍。本文主要从电子星模拟器的软硬件组成进行了详细的设计,通过LVDS将电子图像作为星敏感器的输入,参与控制系统联试,验证了星敏感器在轨工作性能。

1 系统原理与组成

作为应用最为普遍和关键的星敏感器地面标定设备,星模拟器的主要任务是,在实验室里生成静态或者动态星图。按照使用用途将星模拟器分为静态星模拟器、动态星模拟器和电子星模拟器。

静态星模拟器产生一幅固定天区的星图,不能测试星敏感器的动态性能,也不能参与闭路测试。静态星模拟器主要用来考察星敏感器的光路和电路性能。

动态星模拟器用于星敏感器动态性能的测试和标定,可以考察星敏感器动态光学和电性能。动态星模拟器需要实时更新显示星表中的星图,对星图质量具有较高要求,具有光学系统,要求安装精度高,成本较高[12]。

电子星模拟器产生星敏感器线路所需的电子图像。电子星模拟器没有复杂的光学系统,电子图像传送至星敏感器的CPU板,供CPU板软件处理,从而达到实时动态模拟在轨星敏工作过程的目的,验证星敏感器的在轨工作性能。电子星模拟器具有成本较低,无安装要求,精度较高的优点。

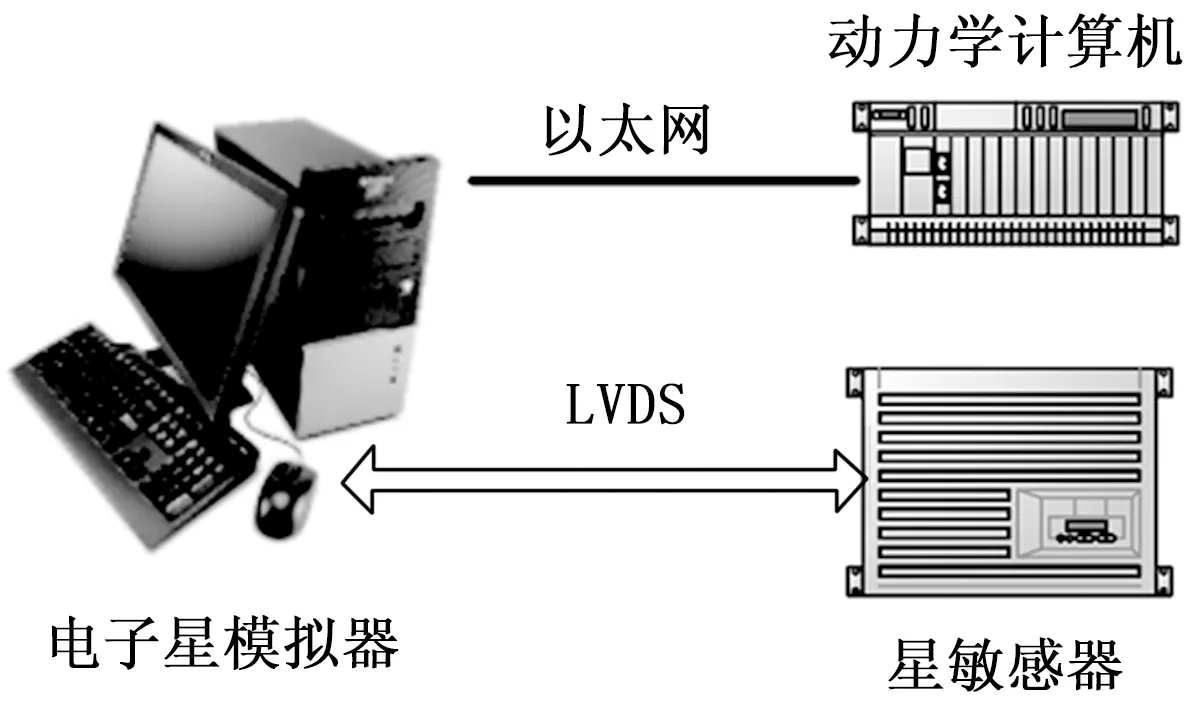

电子星模拟器由控制计算机及相关连接电缆组成,其工作原理如图1所示。电子星模拟器由高性能PC机、图像处理板、硬件底层驱动程序(FPGA程序、硬件驱动程序等)和人机交互界面软件等组成。电子星模拟器控制计算机不仅可以自动生成星图,也可以接收动力学计算机的输入指令生成星图,因此要求电子星模拟器控制计算机与动力学计算机间的通讯协议应简单、直接。

图1 电子星模拟器系统组成框图

地面动力学按照10 ms仿真周期计算出惯性四元数,并通过以太网将四元数发送给电子星模拟器,电子星模拟器根据输入的四元数,查找星图表,实时生成与该姿态对应的星图,并将该星图转换为电子图像通过LVDS电缆输出。星敏的采样周期为200 ms,可见电子星模拟器输出的姿态频率远高于星敏采样频率,同时电子星模拟器可设置不同工况下电子星模拟器产生星图[13-14]。电子星模拟器图像分辨率支持1 024*1 024;图像位宽支持12 bit;能够同时完成帧频10 Hz的图像上传及采集。

2 电子星模拟器硬件设计

电子星模拟器包括测试计算机、LVDS图像卡和对应测试电缆组成。其中,电子星模拟器接受指令并按照指令生成图像,通过LVDS图像卡提供给星敏感器,也可以通过LVDS图像卡接收来自星敏感器发来的图像并存储。电子星模拟器总体结构如图2所示。

图2 电子星模拟器总体结构

电子星模拟器具体功能要求如下:

1)采用PC机扩展卡的形式,可选用PCI/PCIe接口扩展卡;

2)图像为1 024×1 024×12 bit;

3)支持同时激励2台星敏感器;

4)能够同时完成帧频10 Hz的图像上传及采集;

5)要求板卡支持最大带宽同时读写不低于20 Mbps;

6)要求板卡支持LVDS发送与接收;

2.1 电子星模拟器图像处理卡

图像处理卡主要实现LVDS、LVTTL及其RS422差分电平接口,通过PCIe 总线与PC机通讯,实现与星敏感器接口时序,以及图像的上传与下载功能。具体性能如下:PCIe板卡尺寸167.65 * 106.65 mm;符合PCIe V1.1规范,支持PCIe 1 Lane接口;支持DMA读写功能,50 MHz系统时钟实测最大读带宽130 Mb/s,写带宽84 Mb/s,可支持66 MHz系统时钟,最大读写带宽可达150 Mb/s;板载1 GB DDR2颗粒,用作FIFO缓存;采用FPGA芯片,可根据实际需要实现特定时序接口;采用高速电磁隔离,最大传输延迟7 ns;最大可承受脉冲电压6 kV;最大支持20/20 LVDS输入/输出接口,符合IEEE 1 596.3 SCI /TIA/EIA-644规范;支持 4/4 路3.3 V LVTTL输入/输出接口。

此板卡使用FPGA芯片,连接前端接口,控制后端输出,可灵活配置输出接口时序,增加了板卡通用性以及灵活性。鉴于板卡带宽较高,使用SDRAM缓存,防止图像传输过程发生带宽受限或者数据溢出现象。板卡具体原理如图3所示。

图3 板卡原理框图

由于电子星模拟器的实时性需求较高,LVDS数据搬移时的逻辑时序要求较高,FPGA核心电路主要完成设备硬件时序和相关的数据控制处理。设计中采用Altera公司的CycloneIII系列的EP3C40F484C8N,该芯片具有39 600个逻辑单元,高达1 134 Kb RAM资源,可以满足电子星模拟器信号控制和图像处理等需求,集成的存储器控制模块速率可达525 Mb/s,可以用来外接高速大容量DDR2 SDRAM做缓存。

FPGA在本次设计中主要作为控制芯片使用。它的具体作用有以下几个:

1)控制LVDS芯片的工作;

2)利用外部晶振和内部DLL(延迟锁相环)为内部电路和LVDS驱动接收芯片提供精确的时钟信号;

3)控制DDR2 SDRAM模块及相应二选一数据流模块;

4)PCIe总线Local端总线操作模块。

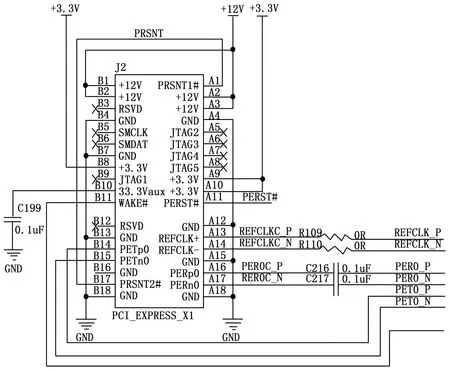

2.1.1 PCIe接口设计

本设计中与FPGA通讯选用PCIe-Local bus,采用PCIe x1接口,在满足带宽要求的基础上,具有更好的适用性。PCIe接口采用PEX8311[15],性能如下:PCIe-Local bus,支持2.5 GHz PCIe x1接口,符合PCIe V1.0规范;支持32位 C/J模式Local bus,最大支持66 MHz时钟;支持SPI接口EEPROM配置寄存器(PCIe端和Local端);1.5 V、2.5 V供电电压,3.3 V IO电压;PBGA 337封装,21 mm*21 mm。根据PCIe V1.0规范,PCIe x1可支持最大传输速率为2.5 Gbps,由于其8/10编码机制,有效带宽最大为200 Mbps(2 Gbps)。根据PLX公司给出的实测数据PEX8311实际传输速率为:读速度大于 160 Mbps,写速度大于 150 Mbps。此数据完全能满足板卡对于数据传输带宽的要求。

PCIe主要有以下信号:TX+/- 、RX+/- 、CLK+/- 、RST 三对差分信号和一个单端的复位信号。发送信号连接到PEX8311的接收端,接收信号连接到PEX8311的发送端,CLK信号连接到PEX8311的时钟信号CLK,RST 信号连接到PEX8311的复位信号。接口电路如图4所示。

图4 PCIe接口电路

PEX8311外接两个EEPROM,一个用于配置PCIe初始化寄存器,另外一个用于配置Local bus。可根据实际需要对PCIe/Local bus进行配置。使用ATMEL公司的64 Kb SPI接口EEPROM(AT25640)用于配置PCIe寄存器信息,使用Microchip公司2 Kb EEPROM(93LC56)配置Local端寄存器信息。

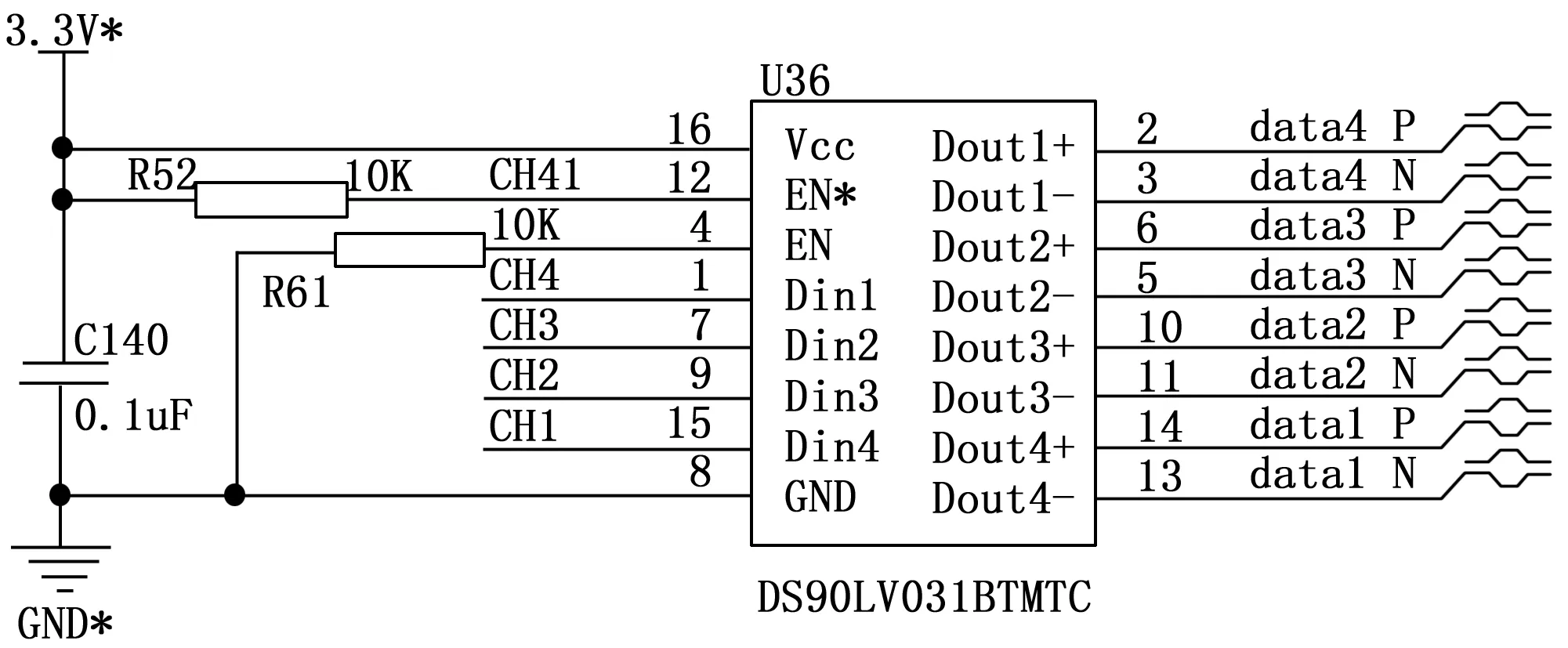

2.1.2 LVDS接口设计

采用TI公司的DS90LV031/DS90LV032作为LVDS接口芯片,可以兼容星上LVDS接口。接口电路如图5所示。

图5 LVDS接口电路图

具体性能如下:大于400 Mbps(200 MHz)转换速率,4通道高速数字隔离器件;0.1 ns的典型差分延迟;2 ns最大传输延迟;3.3 V电源供电;±350 mV差分信号;低功耗(3 V工作时13.2 mW静态功耗);可与外部5 V LVDS芯片交互;兼容IEEE 1596.3 SCI LVDS标准;兼容TIA/EIA-644 LVDS标准。

2.1.3 系统时钟设计

时钟部分主要是PCIe时钟、FPGA时钟以及Local bus时钟。PCIe时钟由PCIe插槽提供。FPGA与Local bus使用50 MHz时钟,由50 MHz晶振经过时钟buffer CY2305SC输出。

2.2 电子星模拟器主机

电子星模拟器主机负责人机交互、图像生成、图像采集、存储显示等,是测试软件运行的载体以及LVDS图像卡、串口通信卡的安装平台。为了能更好的进行图像处理,在计算机CPU选择时着重考虑处理速度,目前选择i7系列CPU,主频为3.4 GHz,四核八线程,以满足图像处理速度; LVDS图像处理卡为PCIe接口,因此在选择主板时应选择有PCIe的主板;选择1T以上存储空间的硬盘。根据上述要求,选择惠普的商用电脑ProDesk 480G6。

3 电子星模拟器软件设计

3.1 图像处理卡发送模块设计

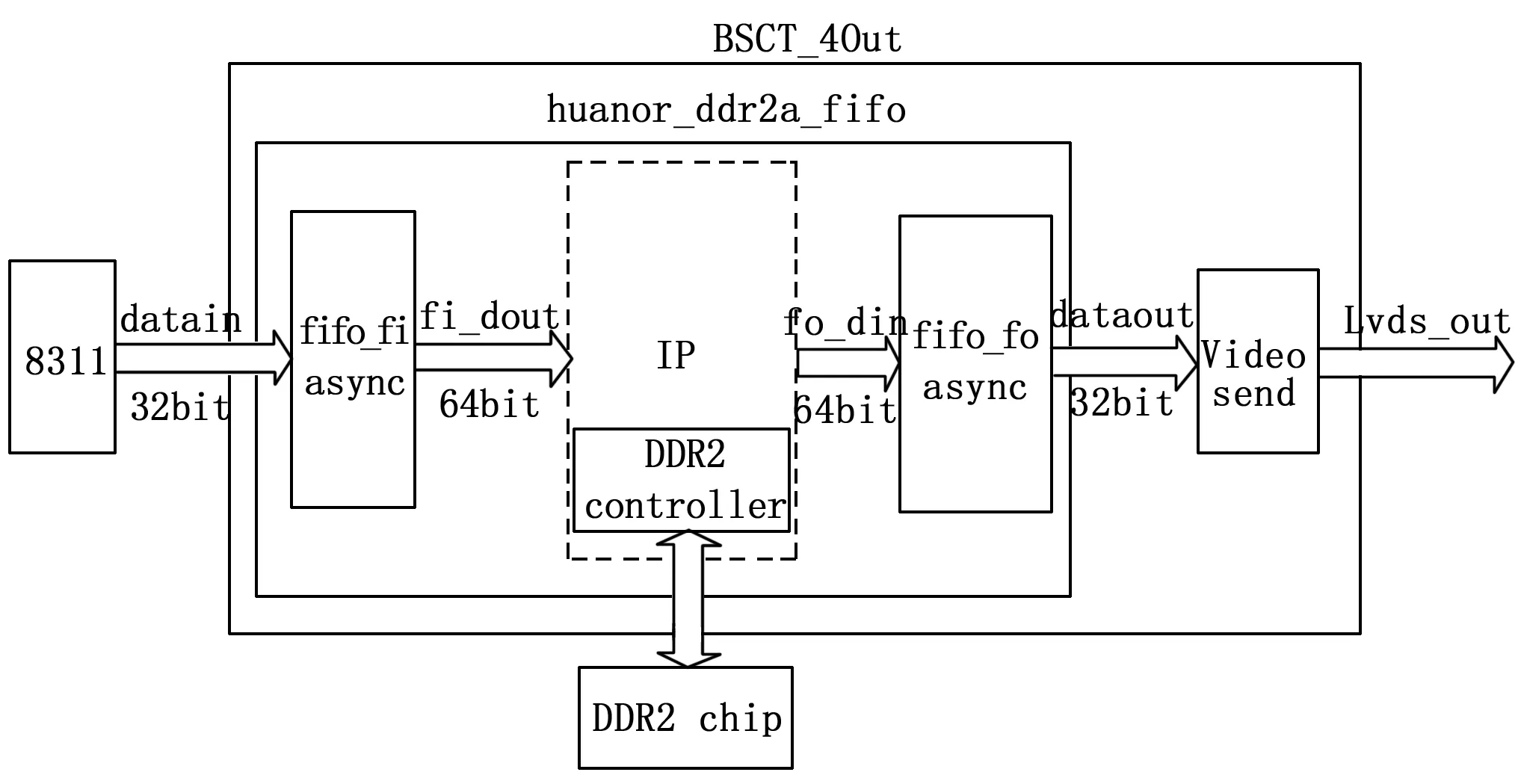

FPGA程序在Altera的Quartus II环境下开发[16-17],发送模块FPGA实现如图6所示。发送图像时,上位机通过PEX8311以50M的时钟向异步fifo_fi连续写入32 bit的图像数据。

图6 发送模块FPGA实现框图

fifo_fi为64bit位宽,当fifo_fi里面的使用地址大于等于64并且接收到DDR2的local_ready信号时,突发地向DDR2内写入64个64bit的数据,完成后DDR2内写数据地址加64(dr_wr_adr += 64);

fifo_fo为64bit位宽,当fifo_fo里面的使用地址小于896,并且接收到DDR2的local_ready信号,以及DDR2内写数据地址大于读数据地址(dr_adr_dt = dr_wr_adr - dr_rd_adr)64,3个条件同时满足时,突发地从DDR2内读64个64bit的数据到fifo_fo中,完成后DDR2内读地址加64(dr_rd_adr += 64)。

异步fifo_fo的输出位宽为32bit,以50M时钟将32bit的图像数据输入给video_send模块,该模块在时钟上升沿发送数据。

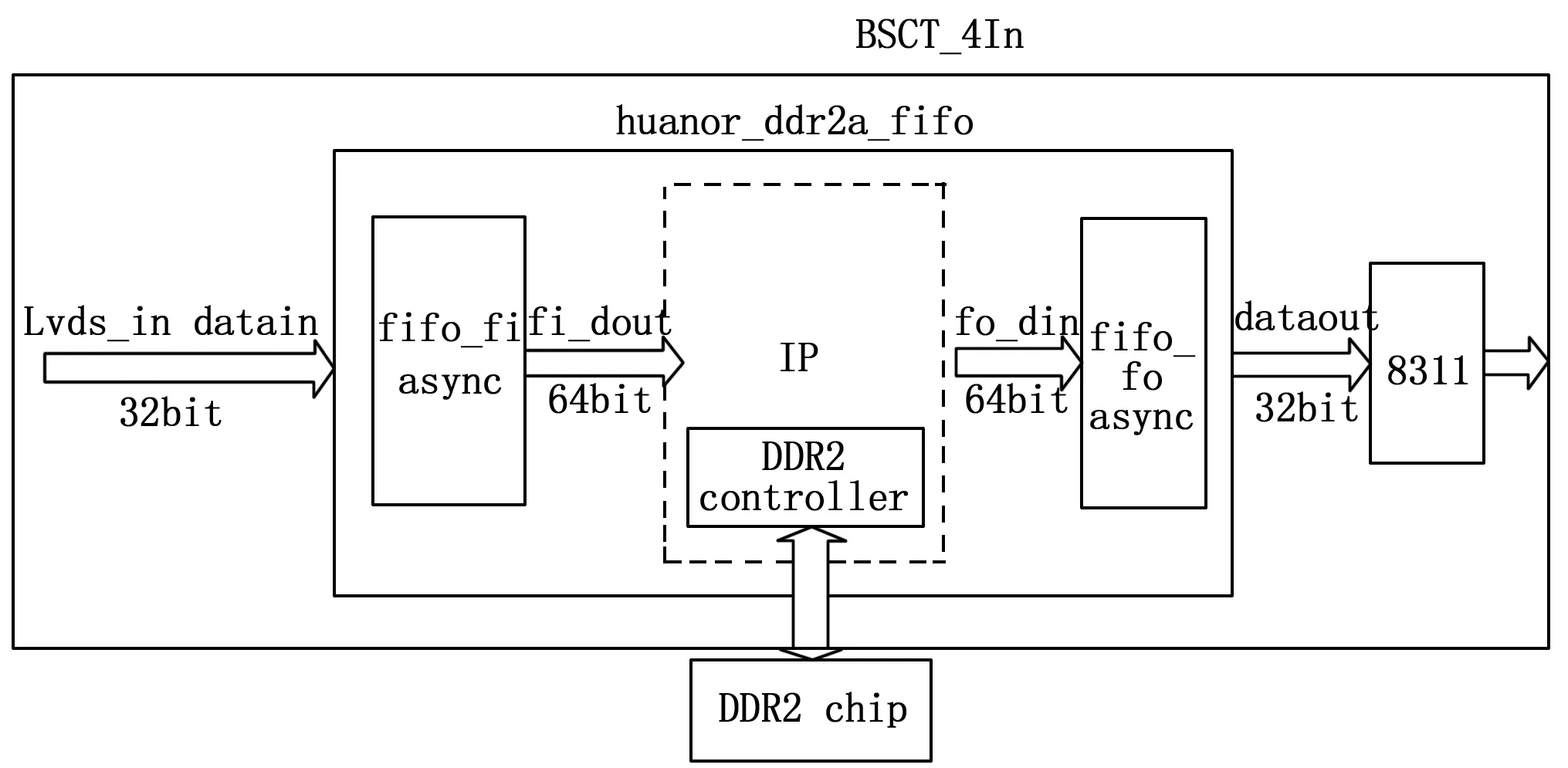

3.2 图像处理卡接收模块设计

接收模块的FPGA实现如图7所示,图像数据经过LVDS接收,接收图像时钟的下降沿取数,将接收到的数据相应的存入32bit数据的低16bit和高16bit,接收完一个32bit数据即产生一个写DDR2_FIFO请求,将数据存入fifo;上位机DMA读请求即fifo的读请求,将数据读出到接收缓冲区,然后软件进行显示及保存图像操作。

图7 接收模块FPGA实现框图

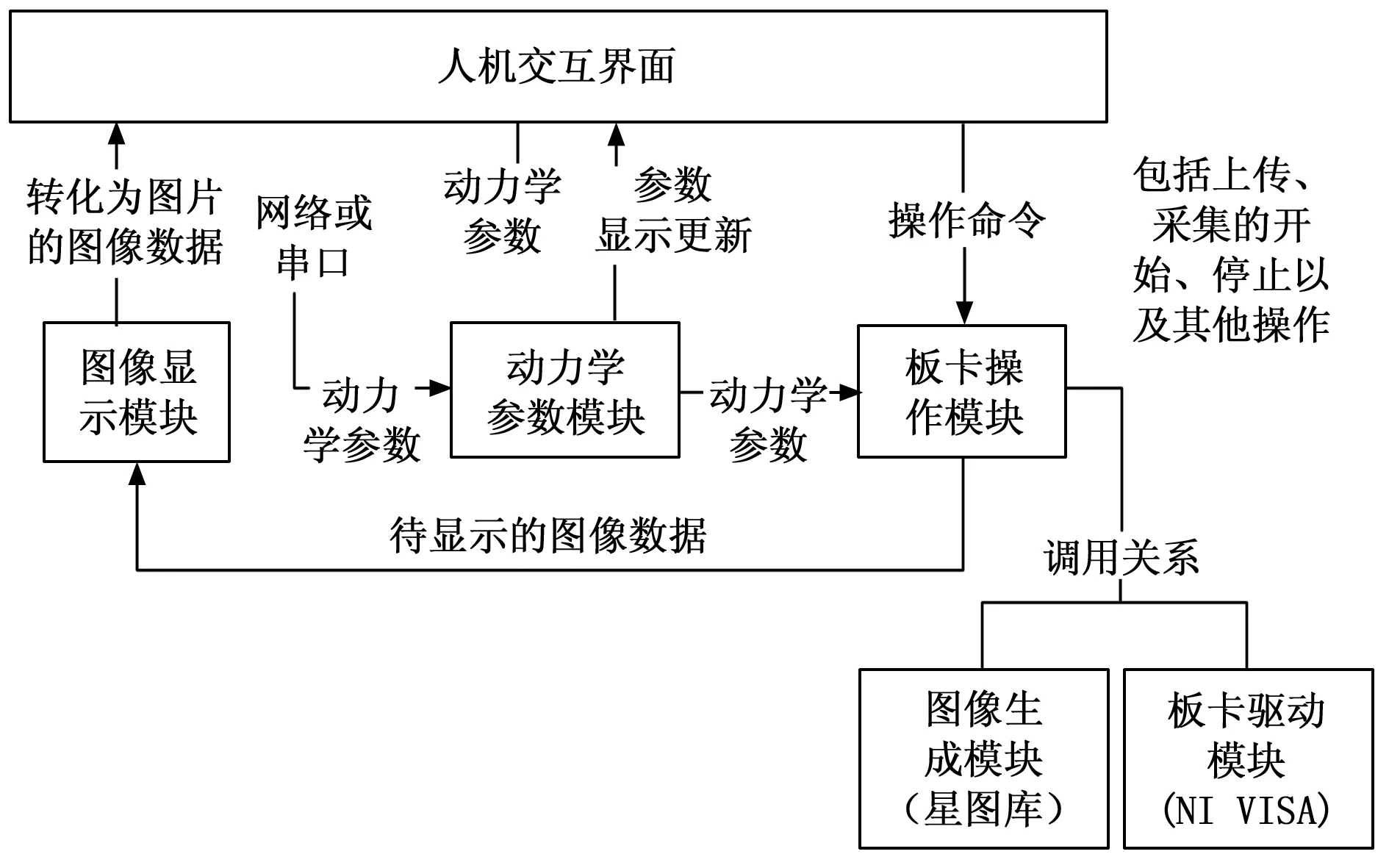

3.3 人机界面软件设计

电子星模拟器软件采用Microsoft Visual Studio 2010编写,程序语言为C#以及VC++,软件运行在Windows 7操作系统下;使用NI VISA来驱动LVDS图像处理卡。人机交互界面、图像显示模块、动力学参数模块均是使用C#开发。人机交互界面使用了WPF界面开发以及Prism框架。板卡操作模块、图像生成模块、板卡驱动模块是使用C/C++开发。这样的方案考虑了板卡操作的性能优化,以及界面开发的便捷性。C#调用C/C++动态库的接口,采用调用方清堆栈的方式进行[18-20]。

3.4 软件结构及功能模块

电子星模拟器软件与动力学地面设备传递动力学参数使用以太网传输模式。

软件的功能模块主要包括:人机交互、板卡操作模块、图像生成、图像发送、图像采集、动力学参数接收/生成及图像显示等功能。

1)人机交互模块。基于灵活配置的软件框架实现基本的按钮控件、编辑框控件、主界面的显示控件、开始/停止图像数据输出、开始/停止图像数据采集、动力学参数显示等。

2)板卡操作模块。主要实现功能是:初始化LVDS图像板卡发送功能、采集功能以及中断功能;维护板卡操作线程;在板卡操作线程中将模拟星图数据通过LVDS板卡发送图像数据,并通过板卡采集图像数据。此模块使用VC++开发接口,以便于C#调用为原则进行设计;调用图像生成模块和板卡驱动模块;调用NI VISA接口来操作板卡。

3)图像生成模块。主要功能是根据动力学参数以及其他系数(星点参数、标定系数等),调用星图库生成模拟星图数据。星图库采用北京控制工程研究所的星图库,专门为小型长寿命星敏电子星模模拟器提供,目前提供的库生成的星图为1024×1024×12 bit。

4)动力学参数接收/生成模块。根据界面用户选择初始化相应的串口或网口,根据界面用户选择开启接收线程(从串口或网络接收动力学参数)或生成线程(本地生成动力学参数);维护动力学参数的实时性。使用C#开发;生成动力学参数主要是四元数根据当前设定的角速度进行积分、计算。

5)图像显示模块。主要实现功能是:将RAW数据格式转换BMP格式;BMP格式数据到显示窗口的转换;定时图像更新;图像分析,放大缩小,灰度值显示。使用C#开发,窗口位图按照BMP格式数据输出。各软件模块的关系如图8所示。

图8 软件模块关系

4 实验结果与分析

根据指标要求,电子星模拟器能够完成10 Hz的图像上传及采集要求,即电子星模拟器接收到动力学计算机的四元数后,将生成的星图上传给星敏感器的时间≤100 ms。影响响应时间的因素主要有:星图生成时间,写DMA时间,Windows线程调度引起的线程等待。在2通道发送、采集均开启的情况下,通过48小时拷机实验,利用软件输出的数据文件进行统计:星图生成时间均小于5 ms;通过PCIe总线通过DMA写2 MB数据时间约为23.8 ms;Windows线程调度时间小于75 ms。故满足系统设计指标。

在某卫星控制分系统地面测试中,将电子星模拟器接入闭环测试回路,在测试过程中,将同一时间段的地面动力学输出给星敏的理论数据和星敏采集到的姿态信息数据进行分析,经过数据分析,理论值和采集值的最大误差为0.000 7,小于0.07%,此误差对于闭环测试系统姿态确定的影响可忽略不计。电子星模拟器性能满足要求,证明了电子星模拟器的实用性和有效性。

5 结束语

本文设计完成了电子星模拟器的软硬件,此电子星模拟器在某卫星控制分系统地面测试中成功的进行了闭环试验。为更充分的验证卫星控制系统方案的可行性,以及确定姿态的工作情况,将电子星模拟器应用于卫星控制分系统的闭环测试中,在地面模拟了星敏在轨识别的星图,测试结果表明电子星模拟器动态响应迅速、工作稳定、误差小,该电子星模拟器具有通用性,可广泛应用于控制系统闭环测试中。