液晶盖板检测系统的多轴运动控制器设计

朱 哲,徐巧玉,王军委,张 正

(1.河南科技大学 机电工程学院,河南 洛阳 471003;2.洛阳银杏科技有限公司,河南 洛阳 471003)

0 引言

液晶盖板检测系统通过运动控制单元控制执行机构,完成对液晶盖板抓取和检测平台位姿调整,实现液晶盖板的检测工作。由于运动控制单元的实时性和可靠性受到系统架构、电路设计等因素的影响,导致液晶盖板检测系统检测的速度和精度较低,因此亟需对其运动控制单元进行研究。

目前,根据控制核心不同,国内外对运动控制单元的研究有3类[1-4],由于基于嵌入式的运动控制具有使用灵活、可靠性高和可移植性强等优点,已成为主要的研究方向。文献[5-11]设计了基于STM32+数字信号处理器(digital signal processor,DSP)作为主控制器,现场可编程逻辑门阵列(field programmable gate array,FPGA)作为从处理器的运动控制器,有效实现了多路电机的同步控制,但采用串行处理的方式易影响其异步控制精度。文献[12-13]提出基于RT-Thread嵌入式实时系统,采用STM32系列微控制器,利用嵌入式操作系统实时性的特点,采用定时器中断的方式输出脉冲驱动电机,该方案能很好地实现多路电机的实时协调控制。文献[14-16]以高级精简指令微处理器(advanced RISC machine,ARM)为主处理器、FPGA为从处理器,利用μC/OS-II作为操作系统的设计方案实现多轴运动控制,但是其硬件设计不适用于液晶盖板检测系统中。

针对上述运动控制器实时性、可靠性差等问题,为实现液晶盖板检测系统的多轴运动控制,本文设计了一种液晶盖板检测系统的多轴运动控制器。本文的运动控制器采用ARM+FPGA的双中央处理器(central processing unit,CPU)架构,在ARM上搭建RT-Thread环境,完成以太网数据通信、指令处理、状态监控和速度规划等功能。对功能划分为线程,由线程优先级抢占调度实现实时控制,FPGA负责输出脉冲、状态反馈和采样处理等工作。运动控制器采用修正梯形加减速算法进行速度规划,保证了执行机构运行的平稳性;同时,硬件电路采用集成化、模块化的设计,保证运行的可靠性。运动控制器利用ARM多线程处理和FPGA并行处理的优势,实现对4个执行机构的实时和可靠控制。

1 系统总体方案设计

为了实现液晶盖板检测系统对多路执行机构实时和可靠的控制,本文采用ARM+FPGA的架构搭载RT-Thread实时操作系统,进行了运动控制器设计,系统总体方案框图如图1所示,主要包括:以太网单元、主控单元、从控单元和接口驱动单元。

图1 系统总体方案框图

以太网单元:采用百兆网卡实现运动控制器与上位机通信,用于上位机对执行机构的控制数据的传输。

主控单元:ARM作为主控单元,采用STM32H750芯片,主要负责对上位机指令处理、数据计算,并控制FPGA程序运行;基于修正梯形加减速算法进行速度规划,针对液晶盖板检测控制参数进行修正,控制执行机构平稳运行。

接口驱动单元:通过硬件电路实现控制单元和执行机构之间的过渡连接,用于驱动控制信号,并实现控制单元与执行机构之间的电气隔离。

工作流程:本运动控制器由上位机控制,STM32通过以太网单元接收上位机控制指令,从中提取轴号、速度、位置和转向等控制参数。STM32基于修正梯形加减速控制算法规划出脉冲运行的控制量,通过通信接口发送到FPGA。FPGA根据STM32的控制参数运行程序,产生的控制信号经接口驱动电路输出给执行机构;同时STM32读取FPGA的运行状态值,实现对执行机构运行的监控,在上位机的监控指令下反馈执行机构运行信息。

2 硬件设计

根据运动控制所要实现的功能进行模块、集成设计,硬件设计框图如图2所示,主要包括以太网通信模块、STM32与FPGA的通信模块、接口驱动模块。

图2 硬件设计框图

2.1 以太网通信模块

以太网PHY芯片采用SMSC公司的LAN8720A,其内置10-BASE-T/100BASE-TX全双工传输模式,通过精简介质独立接口(reduced media independent interface,RMII)连接STM32的局域网(local area network,LAN)总线,以太网通信模块结构图如图3所示。运动控制器作为传输控制协议(transmission control protocol,TCP)客户端,个人计算机(personal computer,PC)作为服务器,实现数据的传输。

图3 以太网通信模块结构图

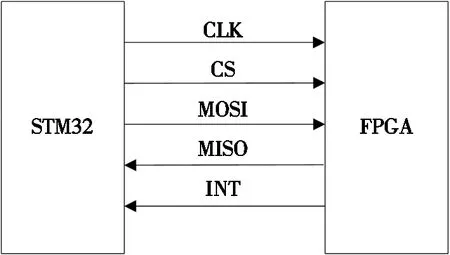

2.2 STM32与FPGA通信模块

STM32与FPGA通信模块通过高速串行外设接口(serial peripheral inteface,SPI)总线实现,SPI时钟由STM32锁相环将外部25 MHz晶振倍频至130 MHz提供,保证了STM32与FPGA通信的可靠性。通过配合一个输入/输出(input/output,I/O)作为中断信号引脚,实现数据通信。STM32与FPGA通信接口如图4所示。

图4 STM32与FPGA通信接口

2.3 接口驱动模块

(Ⅰ)差分驱动电路。在差分驱动电路设计中,由FPGA产生的脉冲、方向信号通过CA-IS3760数字隔离芯片后传输给AM26C31,由AM26C31将单端信号转为差分信号,输入给伺服驱动器。

(Ⅱ)光耦隔离电路。在实现原点和限位开关等输入信号的硬件设计中,采用双向整流输入的模式,经过TLP290-4双向光电耦合器输入到FPGA中,可适应不同型号的开关。

为控制与收集垃圾堆体内部降解产生的渗沥液与填埋气,在独立的垃圾堆体单元内部设置导气集液井,将垃圾堆体内部的渗沥液与填埋气收集,并统一进行处置[7],最终消除垃圾堆体对周围环境的污染隐患。

(Ⅲ)差分接收电路。编码器产生3路(A+/A-、B+/B-和Z+/Z-)差分信号,经AM26C32将每组差分信号转为单端信号后输入到FPGA中,可监控执行机构位置和速度的运行状态。

3 软件设计

软件设计由两大模块组成:嵌入式实时操作系统软件设计模块和运动控制软件设计模块。

3.1 嵌入式实时操作系统软件设计模块

RT-Thread操作系统的搭建:首先,根据意法半导体STM32CubeMX初始化代码生成器制作板级支持包(board support package,BSP)工程,通过Env工具对RT-Thread进行菜单配置,再由Python脚本SCons工具完成RT-Thread操作系统的移植,搭建流程如图5所示。

图5 RT-Thread操作系统搭建流程

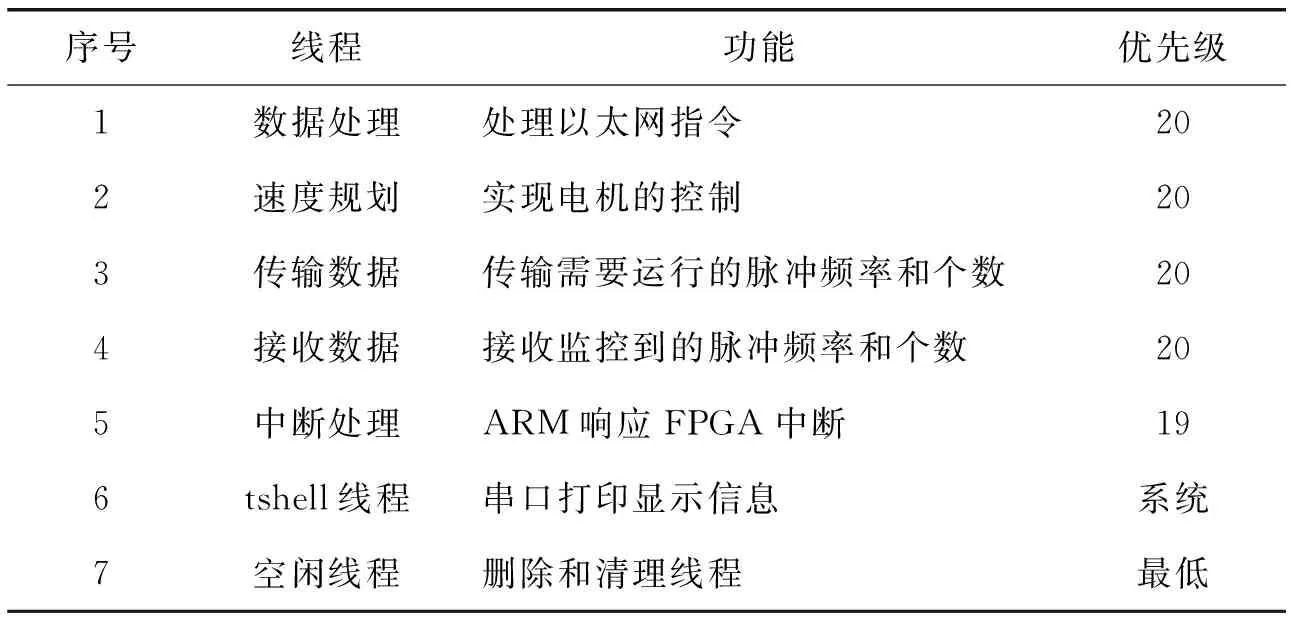

线程功能划分:在RT-Thread环境中以线程的方式实现任务,因此对线程的划分及优先级的分配是实现运动控制器实时控制的关键,优先级的数值越小,其逻辑优先级越高,线程功能及优先级说明见表1。

表1 线程功能及优先级说明

3.2 运动控制软件设计模块

液晶盖板检测系统运行控制由STM32与FPGA作为控制单元控制执行机构,因此运动控制软件设计模块主要包括控制程序设计模块和速度规划模块。

3.2.1 控制程序设计模块

程序流程:STM32通过识别上位机控制指令,根据修正加减速算法进行速度规划,由FPGA产生脉冲和方向信号。运行过程中由FPGA发起中断请求,STM32响应后将脉冲控制参数通过SPI总线依次发送给FPGA。运动控制器输出的脉冲频率实现轴的速度控制,脉冲个数实现轴的位置控制,方向信号实现轴正反转的控制。程序流程图如图6所示。

图6 程序流程图

控制指令处理:为保证控制的有效性,对STM32与FPGA的一帧控制数据进行设计,控制指令说明如表2所示。

表2 控制指令说明

FPGA运行脉冲逻辑:FPGA通过读写脉冲参数输出脉冲,因此FPGA为每个轴例化4个单口RAM存储区,作为缓存、读取离散后的脉冲参数。每个RAM块可以储存128个宽度为16 bit的数据,其中RAM_V1、RAM_V2储存脉冲频率,RAM_P1、RAM_P2储存脉冲个数。FPGA读写RAM块结构图如图7所示,读写操作以组进行,在读取一组数据过程中,FPGA发出中断信号,请求STM32发送另外一组的数据。运动控制器通过独立访问每个轴相对应的RAM块进行循环读写的方式,保证了4路脉冲输出的有效性。

图7 FPGA读写RAM块结构图

3.2.2 速度规划模块

由于液晶盖板检测系统抓取轴存在移动距离长、速度快的特点,所产生的振动是整个系统振动的主要来源,所以针对此过程进行速度规划控制,实现运行的平稳。同时为减少抓取时间损耗和平稳运行,对整个运行操作进行调整:气动吸盘从P0处抓取液晶盖板后上升至H/2高度P1后,执行机构开始水平运行;当经P2位置达到P3位置后,气动吸盘开始向下放置液晶盖板;当液晶盖板达到P4处,执行机构水平运行停止,气动吸盘将液晶盖板放置于P5点,执行机构以同样的方式从P5点到达P0点完成回程工作,从而避免了在转角处的振动和冲击。液晶盖板抓取轨迹路径如图8所示。

图8 液晶盖板抓取轨迹路径

目前常用的速度规划算法有梯形曲线控制算法和S形曲线控制算法,由于梯形曲线控制算法具有计算量小、实现简单等特点而广泛应用,但存在速度不平滑、加速度不连续等缺点;S形曲线控制算法具有很好的速度和加速度的连续性,但其计算量大,实现过程复杂[17-21]。针对以上问题,为了实现运动控制的平稳性,文本采用修正梯形加减速算法进行速度规划,运行位移曲线、速度曲线和加速度曲线如图9所示。

(a) 位移曲线

图9中,0~t1为加加速段、t1~t2为匀加速段、t2~t3为减加速段、t3~t4为匀速段、t4~t5为加减速段、t5~t6为匀减速段、t6~t7为减减速段,amax为最大加速度,Vmax为最大速度。由图9所知:实现了运行曲线速度平滑、加速度连续、计算量小和容易实现的效果。通过公式推导,加减速过程中时间关于加速度、速度、位移表达式分别如式(1)、式(2)和式(3)所示:

(1)

(2)

S(t)=

(3)

其中:a为加速度,pulse·ms-2;amax为最大加速度,pulse·ms-2;v为速度,pulse·ms-1;S为位移,pulse;t为时间,ms;T为整个运行时间,ms;nT为加加速段、减加速段、加减速段和减减速段的时间,ms;n为修正系数;T0为匀加速段和匀减速段的时间,ms;T1为匀速段的时间,ms。

在速度规划过程中,如果对给定参数进行修正后,实际控制总位移s小于修正后位移s时,则设定修正系数n=0.25,T0=0,T1=0。

4 实验结果分析

为验证运动控制器性能,首先通过MATLAB软件运行加减速控制算法,验证脉冲运行的平稳性,再搭建液晶盖板检测平台进行运动控制器实际控制实验。液晶盖板检测运动控制器硬件平台如图10所示。由上位机根据检测系统规划运动控制指令后,通过以太网总线将4路执行机构位置和速度的要求传给运动控制器,由运动控制器输出脉冲信号控制4路执行机构同时运行。经过实验,该运动控制器的数据通信、执行机构控制等功能得到了充分验证。

4.1 速度规划测试实验

运动控制器平稳运行测试主要通过在MATLAB软件中运行速度规划算法控制程序,输出脉冲各阶段的运行参数,通过曲线拟合后与速度规划算法曲线相对比,从而验证运动控制器的平稳性。在速度规划算法中,写入第1组测试数据:位移s=10 000 pulse,速度v=200 pulse·ms-1,加速度a=25 pulse·ms-2,修正系数n=0.125;写入第2组测试数据:位移s=1 000 pulse,速度v=100 pulse·ms-1,加速度a=25 pulse·ms-2,修正系数n=0.05,MATLAB软件运行曲线如图11所示。

图10 液晶盖板检测运动控制器硬件平台

(a) 第1组测试数据加速度曲线 (b) 第2组测试数据加速度曲线

由图11a和图11b可知:第1组测试中加速度曲线分5段运行,amax=23.747 6 pulse·ms-2; 第2组测试中加速度曲线分7段运行,amax=25 pulse·ms-2。测试曲线符合修正梯形加减速规划算法,加速度曲线运行连续,从而实现脉冲平稳运行的效果。

4.2 运动控制器运行实验

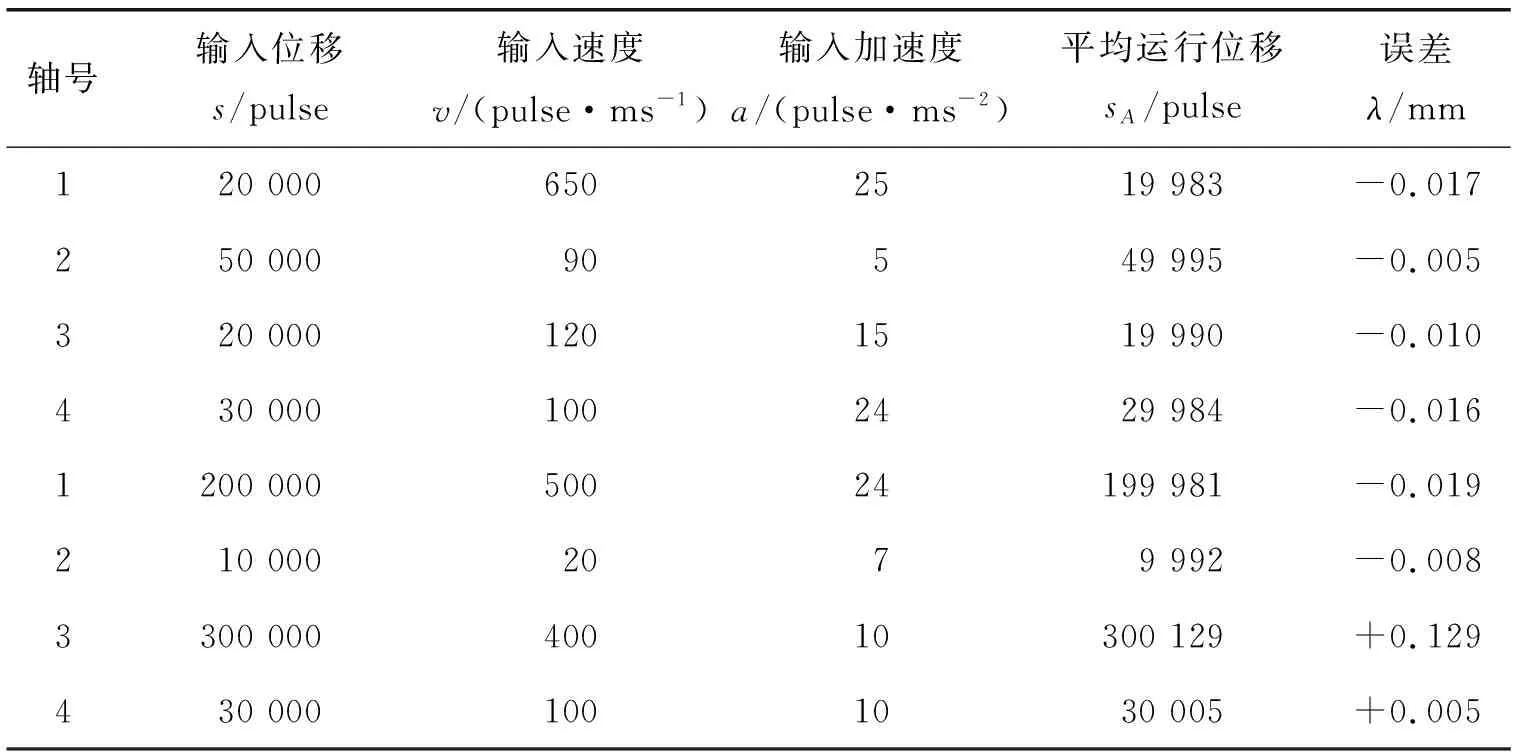

运动控制器实时性、可靠性实验以控制4路台达ASDA-A2系列伺服驱动器和伺服电机组成的执行机构作为实验对象,脉冲当量为1 000 pulse·mm-1。实验过程中,由上位机发送各轴控制参数,运动控制器控制执行机构运行,同时由台达监测软件得到实际运行位移,将两者差值进行对比,实验测试结果如表3所示。

表3 运动控制器实验记录表

由表3可知:运动控制器实际控制误差λ为±0.129 mm,满足实际应用误差。

5 结论

本文设计了液晶盖板检测系统的多轴运动控制器。采用ARM+FPGA的双CPU架构,在ARM上搭建RT-Thread环境,通过百兆以太网接口与PC通信,完成对4路执行机构的实时控制;该运动控制器通过修正梯形加减速算法进行速度规划,使运行具有良好的平稳性。该运动控制器应用于4轴液晶盖板检测系统,实现位置控制误差为±0.129 mm,初步验证了该控制器的控制实时、可靠,满足对液晶盖板检测系统运动控制的需求。