硅基太赫兹频率源关键技术研究进展综述*

冯林平,易 翔,朱浩慎,廖绍伟,车文荃,薛 泉✉

(1 华南理工大学 广州 510641 2 广东省毫米波与太赫兹技术重点实验室 广州 510641)

引言

太赫兹波是频率范围为0.1 THz~10 THz、波长范围(0.03 mm~3 mm)介于无线电波和光波之间的电磁辐射。这个频段是人类迄今为止了解最少、开发最不充分的电磁波资源。它是覆盖很广泛并且很特殊的一个频谱区域,其低频段与电子学领域的毫米波频段相互重叠,而高频段与光学领域的红外频段重叠。太赫兹频率范围处于电子学和光子学的交叉区域,具有携带信息丰富、亚皮秒量级脉宽、高时空相干性、低光子能量、穿透性强、使用安全性高、定向性好、带宽高等特性,因此太赫兹技术在国土安全、天文、医疗、生物、计算机、通信、科学研究等领域有独特的学术价值和广阔的应用前景,被誉为未来改变世界的十大技术之一。太赫兹科学技术已经成为国际上优先发展的学科领域和各国争相抢占的科技制高点,是当前最受关注的国际学术前沿领域之一,它的发展对提高国家科技实力、促进国民经济发展、维护国土安全和社会安定都具有前瞻性、战略性和全局性的重大意义。

太赫兹频率源是研究太赫兹频谱特性及其应用的基础,是太赫兹系统最基本的核心元件,对太赫兹的应用发展起着决定性作用。尽管太赫兹技术具有广阔的应用前景,但太赫兹频段仍是电磁频谱中开发和应用较少的频段。其中,缺乏稳定可靠的太赫兹频率源是太赫兹技术发展面临的最大瓶颈之一。因此,太赫兹频率源的研究和应用成为十分紧迫的需求。图1 所示为瓦片式太赫兹相控阵,信号经过移相器、倍频器以及天线进行收发。

目前,商用的太赫兹频率源前端电路主要采用较昂贵的III-V 族半导体技术,如砷化镓(GaAs)和磷化铟(InP)技术,这些技术的高成本严重制约了太赫兹技术的发展和应用。近年来,随着硅基半导体工艺的不断进步,场效应管的沟道长度不断减小,CMOS 和SiGe BiCMOS 器件的截止频率/最大振荡频率(ft/fmax)分别达到了300 GHz/450 GHz[1]和505 GHz/720 GHz[2],因此硅基工艺上实现太赫兹频率源已经成为可能。相比传统的III-V 族半导体工艺,硅基工艺具有价格低廉、易于与数字电路集成、可靠性高等优势,具备把太赫兹集成产品推广到广大的消费类电子市场的潜力。正是因为其存在着的巨大应用需求和商业前景,当前学术界和工业界都掀起了硅基太赫兹集成电路研究的热潮[3,4]。

近年来,国内外均开展了太赫兹频率源的关键电路的研究,虽然已取得了一些成果,但仍有大量的工作需要开展。特别是国内在这一领域起步较晚,开展的研究工作尚不够深入,并且研究进展受限于半导体等工艺技术。近几年来,人们对太赫兹频率源中的关键电路,如倍频器、振荡器、天线、太赫兹辐射源和辐射源阵列等开展了较为深入的研究,下面将对国内外的研究现状进行回顾与总结。

1 太赫兹倍频器

较早应用于太赫兹频段的倍频器研究主要以III-V 族半导体为主。由于III-V 族基板具有高的绝缘性,因此以III-V 族材料为基板的高电子迁移率晶体管HEMT(High-Electron-Mobility Transistor)及异质结双极晶体管HBT(Heterojunction Bipolar Transistor)可实现较低的插入损耗,且III-V 族工艺下制作的无源器件具有较好的品质因数。近年来,随着硅基工艺的截止频率越来越高,采用硅基实现太赫兹倍频器的研究越来越多。由于倍频方法产生的太赫兹信号具有稳定性好、主振荡频率较低、工作频段较宽、调制度较深等优点,因此常常被优先釆用。国外对太赫兹倍频器电路的研究较早,在工业界以及学术界,众多学者以及工程师们对各种新原理、新方法、新结构、新工艺进行了深入研究,并将其应用到各种类型的太赫兹频率源系统中,取得了不少令人瞩目的成果。2011 年,德国的OJEFORS E 采用0.13 µm SiGe HBT工艺基于多倍频器链路级联方式实现325 GHz太赫兹源,输出功率-3 dBm,直流功耗420 mW,3 dB带宽范围为308 GHz~ 328 GHz[5]。为了提升功率效率和带宽,2013 年,美国的HAN R N 等人,采用CMOS工艺的变容二极管实现了480 GHz的太赫兹频段的二倍频器,该电路拓扑结果简单,使基波信号在输出端口等幅反向抵消,输出二次谐波信号,其显著的特点是直流功耗很低[6],如图2 所示。2018 年,德国NIKPAIK A 等人采用65 nm CMOS 工艺设计了D 波段(129 GHz~171 GHz)的四倍频器,实现了42 GHz的3-dB 带宽,是目前已经报道的最宽带宽,且具有1.7%的转换效率、2.1 dBm的饱和输出功率、5 dB的最大转换增益[7]。

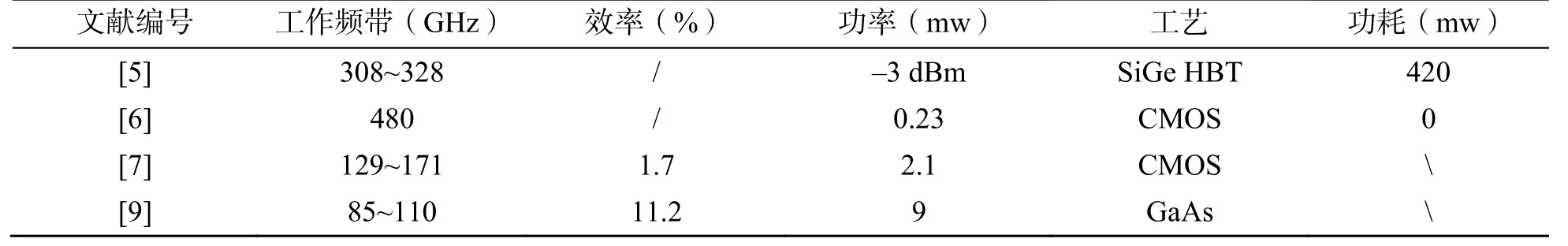

2011 年,中国工程物理研究院的王磊和熊永忠等人利用0.13 μm SiGe HBT 技术研制成功一个单片D 波段(120 GHz~140 GHz)二倍频器。测试结果表明,输入功率约-1 dBm 时,输出频率为134 GHz处获得的最小变频损耗约为3.2 dB,效率约为5.8%,输入功率约为3.1 dBm;在输出频率为132 GHz处获得最大输出功率-1.4 dBm,效率约为7%[8]。2014 年,中国科学院上海微系统与信息技术研究所孙晓玮研究员课题组采用0.1 μm GaAs pHEMT 工艺设计了W 波段(85 GHz~110 GHz)的二倍频器。在100 GHz的工作频率处其输出功率和效率性能优良,最大效率为11.2%,饱和输出功率9 dBm;在85 GHz~110 GHz 频率范围基频信号抑制在-30 dB 以下[9]。2016 年,清华大学王志华教授课题组采用65 nm CMOS 工艺设计了注入锁定的二倍频器。在3.4 dBm~4.1 dBm 注入功率下,其锁定的频率范围为69.2 GHz~94.6 GHz[10]。由于国内的工艺、加工精度、器件等与国外相比具有一定的差距,导致国内的太赫兹倍频器在带宽、倍频损耗、集成度方面等各项指标都没有达到国际先进水平。虽然研究人员提出了一些太赫兹倍频器设计方法,但依然存在许多问题函待解决。鉴于这种局面,我国需要加大对太赫兹倍频器的研究力度。部分太赫兹倍频器参数对比见表1。

表1 部分太赫兹倍频器对比Table 1 Parameters of Terahertz frequency doubler

2 太赫兹振荡器

与太赫兹倍频器相比,太赫兹振荡器具有面积小、能量转换效率高和不需要输入驱动的优点,但其不足之处是调谐范围较窄、频率稳定性差。随着硅工艺的迅速发展,在硅工艺如CMOS 和SiGe BiCMOS工艺上实现太赫兹振荡器已经成为可能。由于硅基工艺的性能劣势,硅基太赫兹振荡器电路的研究开展得相对较晚,研究难度较大,目前的研究进展离III-V 族半导体还有一定的差距。但是,硅基半导体的研究已经逐渐成为热点,每年召开的集成电路设计领域最著名的学术会议(ISSCC、VLSI、CICC、ESSCIRC、RFIC 以及A-SSCC 等)中,关于硅基太赫兹电路的论文在逐渐增多,电路的性能也在逐渐提高。虽然随着半导体器件的体积在不断缩小,但是CMOS 器件最大振荡频率的提升仍然有限。因此为了实现更高的振荡频率,大部分CMOS 太赫兹信号源采用谐波振荡器。2008 年,美国佛罗里达大学SEOK E 等人采用45 nm CMOS 工艺、交叉耦合结构实现了一款工作频率为410 GHz的推推式(push-push)压控振荡器。在1.5 V 电源电压下,其功耗为16.5 mW,通过天线对信号进行输出,辐射功率为-47 dBm,调谐范围为0~2 GHz。虽然这款振荡器与之后实现的CMOS 太赫兹信号源相比性能一般,但它在当时已为CMOS 太赫兹信号源的发展奠定了重要基础[11]。2014 年,台湾国立中央大学Li C H 等人采用40 nm CMOS 工艺实现了一款工作频率在340.6 GHz的三推式(triple-push)振荡器,在0.9 V电源电压下,其功耗为34.1 mW,输出功率为-11.1 dBm,不具备调谐功能;该振荡器电源电压升至1.3 V时,其振荡频率为340.1 GHz,功耗为78.3 mW,输出功率为-9.1 dBm。该电路采用三推式(triple-push)振荡器结构实现了差分输出[12]。2018 年,奥地利AHMED F 等人采用SiGe HBT BiCMOS 设计了300 GHz太赫兹推推式(push-push)振荡器,其最大的输出功率为0.2 dBm,噪声系数为-105 dBc/Hz,频率调节范围为0.9%。该振荡器有比较好的输出功率、频率调节范围以及能换效率。其中一块振荡器在1V的供电下,实现了67.8 GHz~81.4 GHz的频率调节范围,对应-108-113 dBc/Hz @10-MHz 噪声范围,以及13-dBm的直流功耗[13]。

2017 年,清华大学王志华教授课题组设计了接近半导器件最大振荡频率的振荡器,工作在192.3 GHz,在1.2 V 供电下最大输出功率-10.4 dBm,噪声-100 dBc/Hz @ 10 MHz[14]。2018 年,东南大学洪伟教授课题组采用0.13µm SiGe BiCMOS 工艺研制出243 GHz 振荡器,在0.94 V 供电下,其最大输出功率为-1.4 dBm,频率调谐范围为5.18%,能换效率1.95%[15]。同年,华南理工大学薛泉教授课题组提出了无变容管的振荡器技术,如图3 所示,实现了振荡器的频率调节和相位噪声的最优化设计[16]。部分太赫兹振荡器对比见表2。

表2 部分太赫兹振荡器对比Table 2 Parameters of Terahertz frequency multiplier

3 太赫兹天线

太赫兹天线是太赫兹辐射源的重要组成部分。近几年以来,随着太赫兹技术的发展,国内外关于太赫兹天线的报道也非常多。之前已有的硅基太赫兹阵列的文献报道中均采用了传统的电波天线结构来实现太赫兹波的接收。德国乌珀塔尔大学Pfeiffer 教授团队于2008 年利用0.25 µm 工艺在600 GHz 实现90 µm的偶极子天线,天线单元增益为5 dBi[17],随后使用半波长差分贴片天线构成650 GHz 焦平面阵列,天线单元增益为2.1 dBi,带宽为7%[18]。美国REBEIZ G 教授团队于2013 年利用BiCMOS 工艺实现360 GHz 椭圆槽环天线,单元天线增益为4.5 dBi,辐射效率为62%[19]。2016 年,以色列SOCHER E教授利用65 nm CMOS 工艺在296 GHz 使用环形天线实现2×3 阵列[20]。2018 年,美国JALILI H 等人采用0.13 µm SiGe BiCMOS 设计了基于偶次谐波直接耦合馈电的2×2的340 GHz 片上贴片天线,有效地避免了馈电网络的损耗和寄生效应[21]。

2015 年,南京理工大学吴文教授团队采用0.13 µm SiGe BiCMOS 设计了340 GHz 高增益高效率太赫兹三维天线结构[22],该天线加载了基片集成波导作为背腔,因此天线的副瓣比较低。2017 年,华南理工大学薛泉教授课题组提出分布式封装天线的全新设计概念,如图4 所示,该设计充分利用芯片和封装的结构优势,采用空间电磁波耦合互连,克服传统片上天线在太赫兹频段介质、金属损耗大,以及天线与激励源互连损耗大的缺点[23]。2018 年,东南大学洪伟教授课题组提出了片上的介质谐振器天线[24]。部分太赫兹天线参数对比见表3。

表3 部分太赫兹天线对比Table 3 Parameters of Terahertz antenna

4 太赫兹辐射源

通常太赫兹辐射源是太赫兹系统的核心模块。产生太赫兹辐射源的方式主要是太赫兹多倍频器链或谐波振荡器的信号通过天线辐射出去。早期大多数太赫兹辐射源的研究大多数基于III-V 族半导体工艺,具有性能高、价格昂贵、集成度和良率低的特点。相较而言,硅基工艺具有低成本、高集成度和小型化等优势,目前国际上采用硅基工艺实现太赫兹辐射源已取得诸多进展。2008 年,美国的SEOKL E 等报道了采用45 nm CMOS 工艺的410 GHz 太赫辐射源,该辐射源中使用了推推振荡器(push-push oscillator),馈入一对差分信号抵消振荡器基波成分使其工作在二倍频,从而在一定程度上克服半导体器件最大振荡频率的限制[25]。2012 年,美国加州理工学院HAJIMIRI A 教授课题组提出一种波束可控太赫兹辐射源,该辐射源工作在280 GHz,采用45 nm SOI CMOS 工艺,集成分布式有源天线、压控振荡器、注入锁定三倍频器等关键器件,通过精确控制相位实现了80°方位角和俯仰角的二维波束扫描[26]。其集成有源分布式天线是该项目的一大特色,能够有比较高的辐射效率。2015 年,美国康奈尔大学AFSHARI E 报道了一种340 GHz 基于65 nm CMOS 工艺的太赫兹辐射源,通过控制相邻单元的耦合实现了频率锁定调谐和波束的独立控制[27]。2019 年,比利时鲁汶大学REYNAERT P 设计了基于40 nm CMOS 工艺530 GHz的太赫兹辐射源,该辐射源通过两次注入锁定技术补偿相位误差以及幅度波动,从而实现相位的精准控制E 面的波束扫描;该辐射源的辐射功率为-12 dBm,转换效率为0.24%[28]。

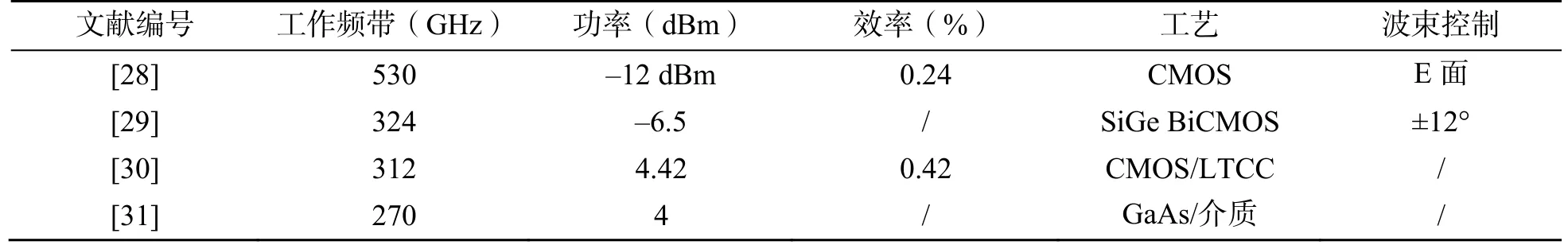

由于国内太赫兹辐射源方面研究起步相对较晚,并受限于半导体工艺以及加工技术等,技术水平与国外相比还有一定差距,但是在该领域也开展了一些研究工作,并取得了较大的成果。2015 年,中国工程物理研究院的熊永忠教授报道了基于0.13 µm SiGe BiCMOS 工艺相控发射机架构的太赫兹辐射源,实现了最大EIRP 10.6 dBm 以及±12°波束扫描范围[29]。2017 年,华南理工大学薛泉教授课题组提出基于分布式封装天线的硅基65 nm CMOS 工艺的312 GHz 太赫兹辐射源,该团队提出的辐射激励芯片+封装分布式天线的全新设计理论极大地提高了芯片与天线互联的自由度,降低了太赫兹频段严重的互连损耗和辐射损耗,有效地提高了辐射增益[30],如图5 所示。2018 年,东南大学毫米波国家重点实验室洪伟教授课题组使用0.1 µm GaAs 工艺,使用9 次倍频和片上介质谐振天线的270 GHz 太赫兹辐射源,实现了4 dBm的输出功率[31]。部分太赫兹辐射源参数对比见表4。

表4 部分太赫兹辐射源对比Table 4 Parameters of THz radiation sources

5 太赫兹辐射源阵列

由于目前器件在太赫兹频率下输出功率仍较低,为了增大总体辐射功率,太赫兹辐射源阵列应运而生。国外对基于阵列天线的太赫兹辐射源关键器件和电路的研究较早,在工业界以及学术界,众多学者以及工程师们对各种新原理、新方法、新结构进行了深入研究,并将其应用到各种类型的电路中,取得了不少令人瞩目的成果。2011 年,德国ÖJEFORS E 等人采用0.25 µm SiGe CMOS 工艺提出基于多倍频链路的820 GHz 太赫兹辐射源,在823 GHz 最大的EIRP 功率为-17 dBm,但是该辐射源阵列的带宽较小,架构比较复杂[32]。2014 年,德国的PFEIFFER U 等人提出了基于0.13 µm SiGe BiCMOS的谐波振荡器级联的4×4的可重构辐射源阵列,频率调谐范围为519 GHz~536 GHz,最大辐射功率为-11.3 dBm,能换效率为0.4%[33]。2017 年,美国Aghasi H 等人报道了0.13 µm 工艺的0.92-THz SiGe的四倍频太赫兹辐射源阵列。同时该团队基于非线性理论提出一种通用设计方法,实现振荡器谐波的最大功率最优化,其最大的辐射功率为-10 dBm,直流功耗为5.73 mW[34]。

2014 年,德国的PFEIFFER U 等人发表了采用0.13 μm SiGe BiCMOS 工艺的三推式(triple-push)振荡器实现的0.53 THz 太赫兹源阵列,其频率调谐范围为519 GHz~536 GHz,EIRP 功率为25 dBm,能换效率为4%[35]。2017 年,美国的JALILI H 等人发表了基于0.13 μm BiCMOS 工艺的4 次谐波耦合振荡器的2×2的辐射源阵列,实现了E 面128°和H 面53°的波束扫描宽度以及-12.8 dBm的辐射功率[36]。2018 年,比利时GUO K 等人报道了基于28 nm Bulk CMOS的530GHz的太赫兹辐射源阵列。该辐射源阵列使用交叉耦合谐波振荡器和介质透镜天线,实现了-22 dBm的输出功率以及0.332%的能换效率。2018 年美国HAN R 等人报道了基于0.13 µm SiGe BiCMOS 工艺的1 THz 辐射源阵列,利用多功能可扩展阵元形成阵列,最大辐射功率为-11 dBm,直流功耗为1.1 W[4],如图6 所示。目前,国内对太赫兹辐射源阵列的研究工作还处于起步阶段,仍需要在理论分析和设计方法上进行深入研究。

6 结束语

随着太赫兹技术的发展,得益于太赫兹频段丰富的频谱资源和相对宽的频带,太赫兹频率源表现出广泛的应用前景,如超高速短距无线/有线通信、雷达、医疗、成像和遥感传感器等。目前国外在这一方向的研究较为深入,但国内相关研究刚刚起步,还缺乏对基础理论及应用的系统性研究。因此,深入开展太赫辐射频率源关键技术的理论及应用研究,探索太赫兹频率源关键核心电路以及太赫兹辐射源阵列电路的分析方法与设计,并对理论方法的有效性进行实验验证,具有十分重要的理论意义和实用价值。