全数字无线电能传输频率跟踪控制方法

张欣, 倪豪, 褚志齐, 李方洲, 李春智

(天津工业大学 天津市电气装备智能控制重点实验室,天津 300387)

0 引 言

无线电能传输(wireless power transport,WPT)技术可以实现电气隔离,摆脱有形介质将电能从电源端传递至用电设备的一种电能传输方式。由于其传输电能方便灵活,具有广阔的应用前景[1]。目前能够实现无线电能传输的方式主要有电磁辐射式、电场耦合式、磁场耦合式、超声波等[2-3]。磁耦合谐振式WPT则利用强磁耦合谐振技术,使其具有传输距离远,传输功率大等优点,因此得到了众多关注[4-5]。感应耦合式无线电能传输技术中也有磁谐振,可以降低电能传输过程中的无功损耗,提高WPT系统的传输效率。在电能传输过程中,工作温度、寄生参数和收发线圈距离等改变以及加入外界异物都会引起谐振频率的变化,在电源频率不变的情况下,系统会发生失谐,导致传输效率和功率大大降低[6-7]。

为了避免系统失谐,提高传输功率和效率,目前主要有阻抗匹配和频率跟踪控制两种方法。文献[8-11]均采用自适应阻抗匹配的方法改变系统的网络参数来解决失谐问题。但是这种方法会使系统的其他参数也发生改变,在实际工程中互操作性不强。文献[12-14]采用补偿电容阵列的方法来调谐,方式较为复杂,不易实现,而且电容值之间的步长较大,因此调谐精确度有限。频率跟踪控制较前两种方法实现简单,跟踪速度快,调整精度高等优点,因此成为了研究的热点。文献[15]采用模拟锁相环实现了频率跟踪,但是模拟锁相环电路设计复杂,抗噪性能差且中心频率不可变,锁相范围较窄。文献[16]采用基于最大接收电压的频率跟踪控制方法,该方法监测接收端的电压,根据电压的反馈信息来调整发射源的频率,但是这种频率跟踪的方法精确度较低。文献[17]提出了一种基于短路电流检测的新型频率跟踪方法,该方法可以在多个振荡周期内实现精确的频率校正,但是这种方法抗干扰性不足。文献[18]采用DSP & FPGA编程方法实现频率跟踪控制,但是其跟踪的频率范围有限(100~500 kHz)。文献[19]通过FPGA编程的方法实现了一种全数字锁相环,分析了锁相环的数学模型,但是只是对频率跟踪控制进行探讨,没有研究频率跟踪范围,也没有相应的程序保证系统(ZVS)软开关的实现。文献[20]采用了一种微分锁相环的失谐控制策略对系统谐振频率进行跟踪,减小了无线电能传输系统功率的波动程度。

本文针对无线电能传输过程中的频率失谐现象,基于FPGA设计了一种具有动态分频和动态时滞功能的自适应模值全数字锁相环(all digital phase locked loop,ADPLL),对发射线圈电流频率和相位进行跟踪。动态分频功能使锁相环中心频率也能随着线圈的谐振频率波动而变化,提高了锁相范围;自适应模值功能可以根据相位差动态调节K模值,解决了传统锁相环锁相精度和锁相速度之间的矛盾;动态时滞功能可以对系统阻抗角进行控制,保证系统在不同工况下都呈弱感性,以实现ZVS软开关;利用FPGA实现的频率跟踪系统为全硬件结构,比传统的频率跟踪系统的跟踪速度更快。将该锁相环应用于感应耦合式WPT技术,实现了全数字无线电能传输控制系统。

1 基于双边SS-WPT系统模型

1.1 耦合电路模型

无线电能传输主要有四种基本拓扑结构,分别为串-串(SS)型,串-并(SP)型,并-串(PS)和并-并(PP)。其中SS型最为结构简单,易于分析[21]。因此本文采用SS型拓扑结构。

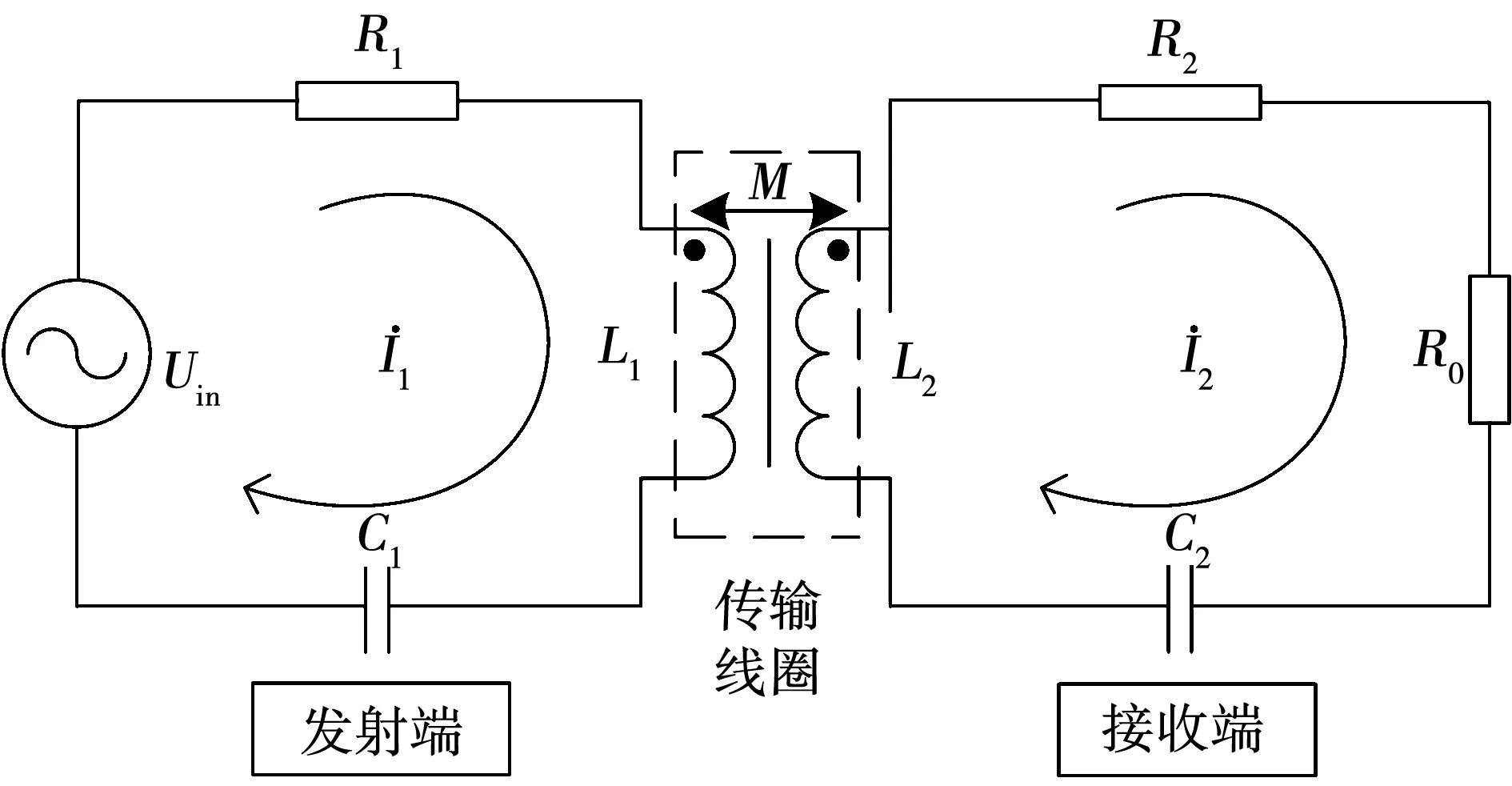

图1为SS型拓扑结构等效模型。其中:C1、C2分别为发射端和接收端的补偿电容;L1、L2分别为接收线圈和发射线圈电感;M为线圈互感;R1、R2分别为发射线圈和接收线圈的电阻;R0为负载电阻。

图1 SS型拓扑结构等效电路Fig.1 SS topology equivalent circuit

1.2 频率跟踪控制原理分析

由图1可得,发射线圈等效阻抗为

(1)

接收线圈等效阻抗为

(2)

根据图1,采用回路电流法可得回路电流方程:

(3)

联立方程可得发射线圈和接收线圈的回路电流为:

(4)

(5)

由此可得,发射端输入效率P1、负载R0的接收功率P2分别为:

(6)

(7)

系统的传输效率为

(8)

当系统处于串联谐振状态时虚部为0,Z1=R1,Z2=R0+R2,此时最高传输效率为

(9)

当电源输出频率与两线圈谐振频率相等时,可以实现电能最大效率传输。

接收线圈对发射线圈的引入阻抗

(10)

发射线圈的引入阻抗

(11)

原边电压与电流的相位角可通过Zin得出

(12)

其中互感

(13)

谐振角频率为

ω=2πf。

(14)

从上式可以看出,系统阻抗角φ与ω、L1、L2、C1、C2、R1、R2、R0和k这些参数都有关系。系统在工作过程中,这些参数的变化都会引起系统阻抗角的变化,因此如何对系统阻抗角进行控制,使其不会因为参数的变化而变化至关重要。

2 FPGA频率跟踪方法

2.1 全数字锁相环的结构和数学模型

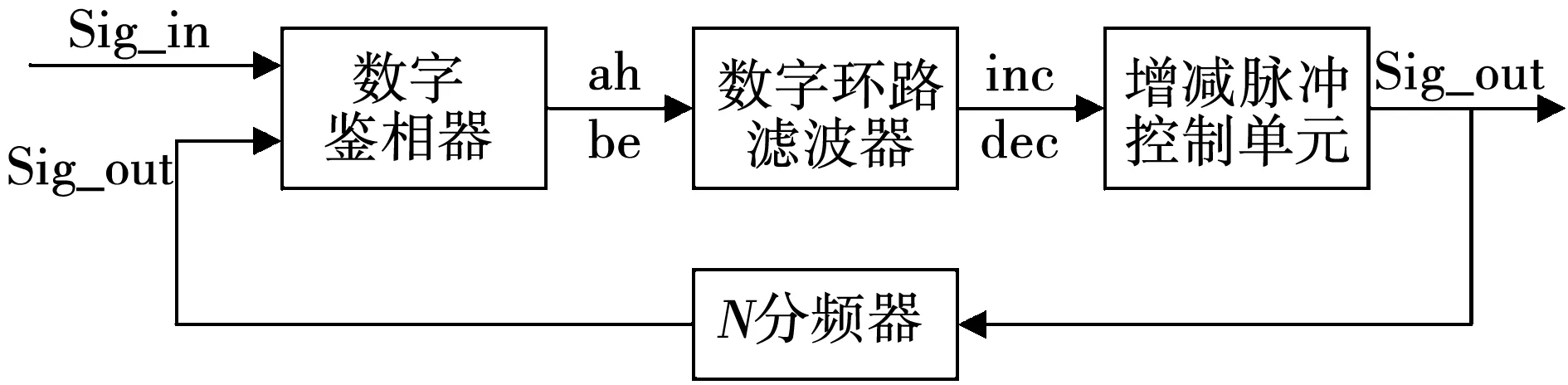

图2为全数字锁相环的基本结构图,主要由数字鉴相器、数字环路滤波器、脉冲增减控制单元和N分频器组成。

图2 全数字锁相环基本结构图Fig.2 Basic structure diagram of all-digital phase-locked loop

全数字锁相环工作过程为:数字鉴相器对输入信号Sig_in和反馈信号Sig_out进行相位比较,并根据反馈信号超前或滞后输入信号输出相位超前信号ah和相位滞后信号be。数字环路滤波器会根据接收到ah信号和be信号,输出进位脉冲信号inc和借位脉冲信号dec,脉冲增减控制单元会根据inc信号和dec信号进行增减脉冲处理,经过N分频器后反馈回数字鉴相器。

根据其输出特性,得出其传递函数为:

(15)

(16)

化简后得

(17)

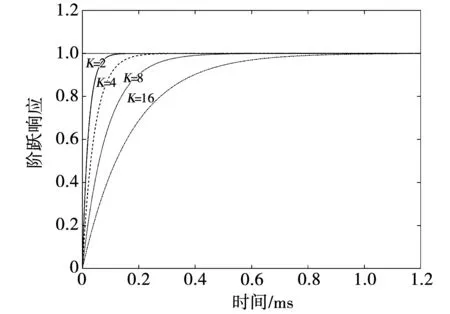

其中:f0为系统时钟频率;K为数字环路滤波器的计数器模值;N为分频系数。对本锁相环进行研究,取f0为50 MHz,N为1 074,选择不同的参数值K,利用Matlab对上述数学模型的不同K值进行阶跃响应仿真,仿真结果如图3所示。

图3 锁相环的阶跃响应仿真图Fig.3 Simulation diagram of the step response of the phase-locked loop

传递函数H(s)为惯性环节,要获得良好的响应效果,要取合适的T值。由一阶惯性的幅相特性可知,截止频率会随着T减小逐渐增大,转折频率会逐渐增大。从时域和频域来看,系统的带宽越大,时域的响应速度也就越快,系统跟踪输入信号的能力就越强。由式(16)可知,K值越小,在高频率的采样系统中,高控制频率的系统性能越好,所取得的控制效果越好。

由仿真结果可知,当K=2时锁相环的响应速度最快,但是调整步长最大,锁定时的相位误差也最大。随着K值的增加,系统的响应速度变慢,但是调整步长变小,锁定时的相位误差也随之减小。由此可知:模值K的取值可以根据数字鉴相器输出的误差大小来而定。当误差较大时,应该选择较小的K模值,可以缩短捕获时间;当鉴相误差较小时,应该选择较大的K模值,可以提高锁相精确度。因此,可以根据鉴相误差的大小,设计一种自适应K模值的锁相环系统,实时动态调整K模值的大小,以解决锁相时间和锁相精确度之间的矛盾。

2.2 自适应模值全数字锁相环

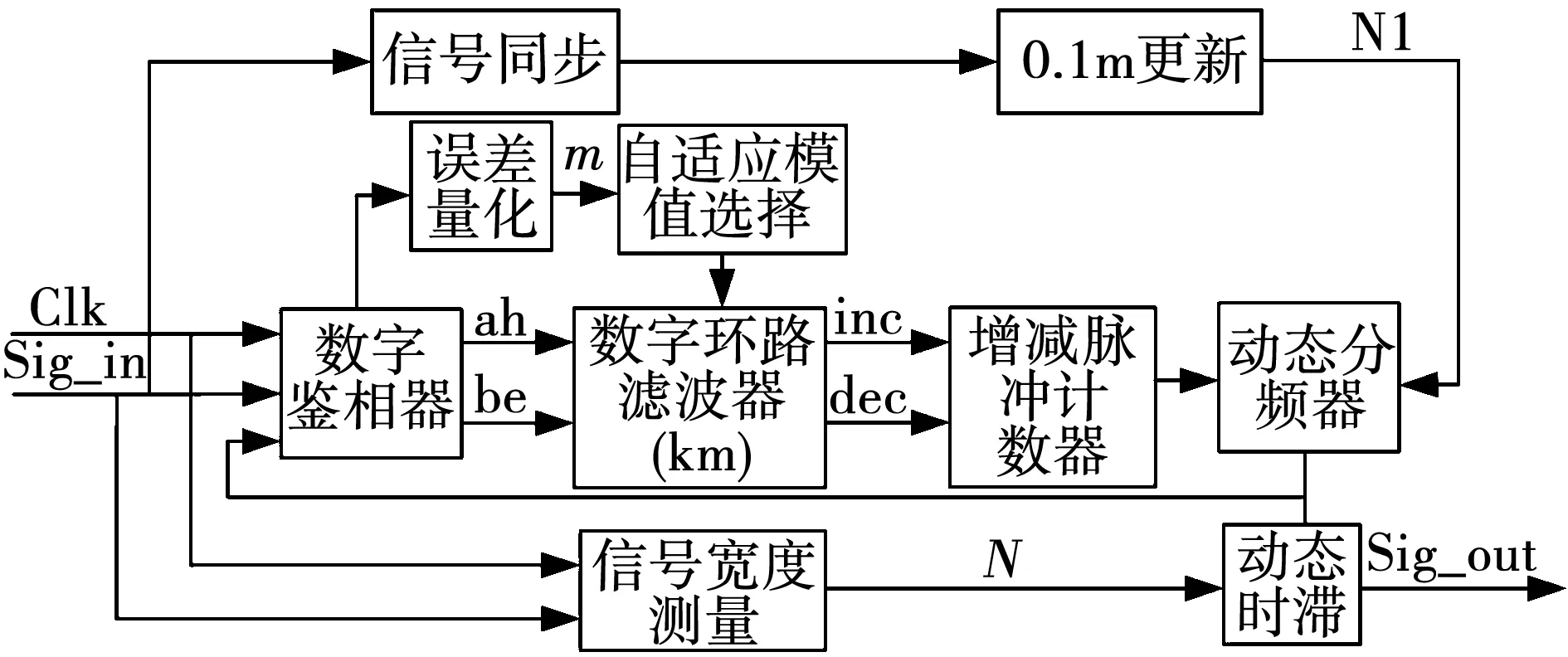

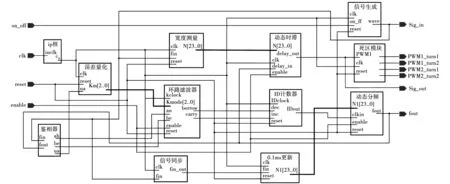

为了解决传统锁相环锁相时间和锁相精确度之间的矛盾,本文改进了传统的锁相环,提出了一种自适应模值全数字锁相环对发射线圈的电流进行实时快速跟踪。自适应模值选择模块可以根据鉴相误差实时动态调整K模值,使该锁相环始终工作在最优K模值状态下,保证了控制系统的稳定性和快速性。此ADPLL主要由数字鉴相器、数字环路滤波器、增减脉冲计数器、信号宽度测量以及动态分频、动态时滞等部分组成,其整体结构图如图4所示。

图4 改进的全数字锁相环整体结构图Fig.4 Improved overall structure diagram of all-digital phase-locked loop

数字鉴相器采用双D触发式鉴相器,主要由两个D触发器组成,主要功能是比较两个信号的相位差。该鉴相器可在输出相位超前信号ah和相位滞后信号be的同时输出相位误差信号ua。

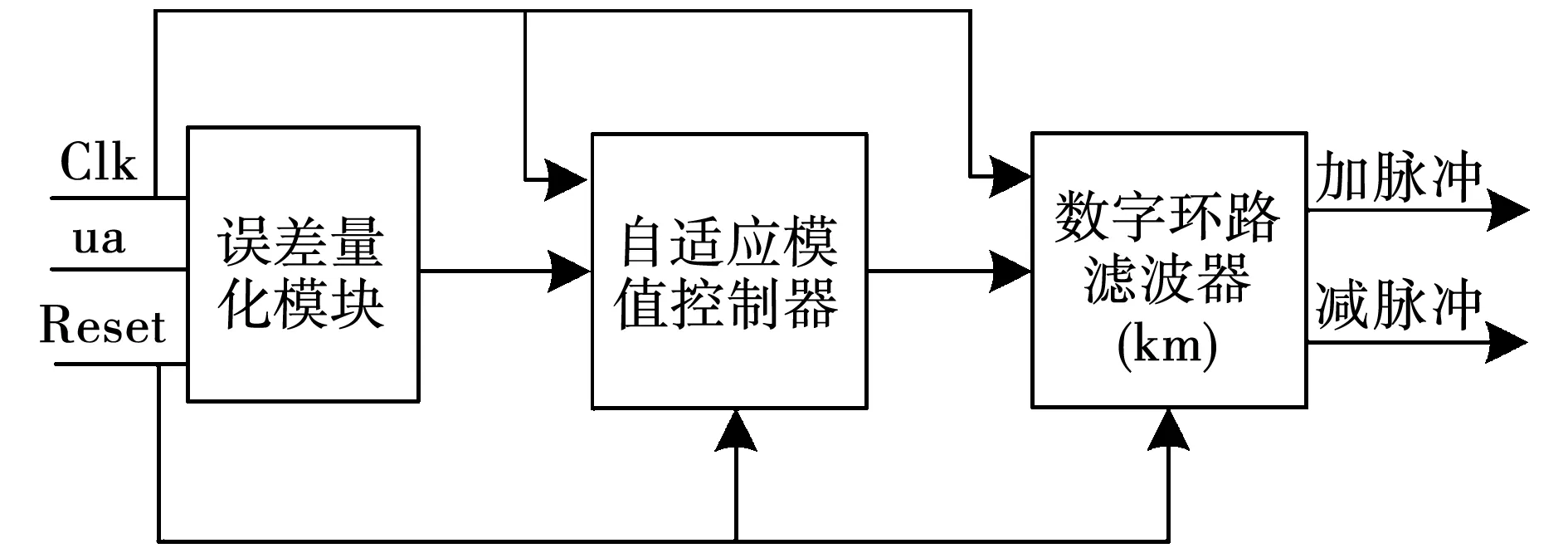

如图5所示,为自适应模值选择模块结构图,由误差量化环节、自适应模值控制器和数字环路滤波器组成。ua为鉴相器输出的相位误差信号,Clk为系统时钟信号,Reset为系统复位信号。

图5 自适应控制器结构图Fig.5 Adaptive controller structure diagram

误差量化环节根据数字鉴相器输出的鉴相误差ua来确定不同m值,输出到自适应模值选择器中。其主要原理是:当ua为高电平时,误差计数器会对其进行计数,在ua的下降沿,误差计数器清零,并将计数值以时钟周期为单位转换为计数值m。

自适应模值选择控制器内有比较器和数据选择器,可将计数值m与预先设定的值Emax=150、Emid=50、Emin=20进行比较,当计数值大于Emax时,输出model=00;当计数值大于Emid时,输出model=01;当计数值大于Emin时,输出model=10;当计数值小于Emin时,输出model=11。

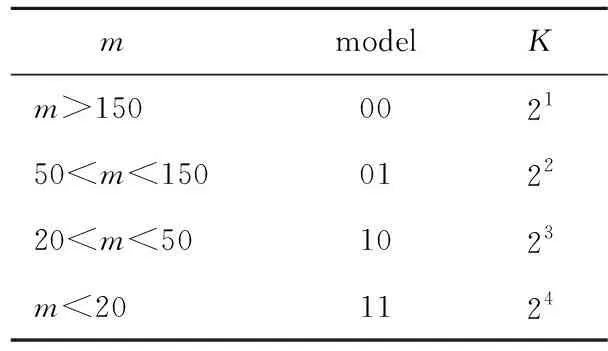

数字环路滤波器根据输入的model值来设置可逆计数器的Km值。当model=00时,Km=2;当model=01时,Km=4;当model=10时,Km=8;当model=11时,Km=16。K模计数器计数方向由脉冲超前信号ah和脉冲滞后信号be控制,环路滤波器根据ah和be的高低电平输出进借位脉冲信号。K模计数器的参数如表1所示。

表1 K模计数器参数表

脉冲增减计数器起到调整输出信号频率和相位的功能,它会根据inc信号和dec信号对输出信号进行加脉冲或者减脉冲处理,从而使输出信号频率和相位趋近于输入信号,完成锁相。

定频工作情况下,系统的谐振频率为46.4 kHz,输入信号的一个周期的长度约为0.02 ms。如果更新时间设置过长,将不能及时将N1值送入到动态分频器中,会导致锁相环短时间内处于一种固定分频的状态,不能满足控制系统快速性的要求。如果更新时间过短,更新过于频繁,会加大FPGA资源的使用率,导致锁相时间过长,不利于系统长时间运行。综合以上考虑,让N1值约5个输入信号周期更新一次。动态分频部分由信号同步和0.1 ms更新两个模块组成。信号同步模块使输入信号Sig_in经过两级寄存器,消除由组合逻辑和延迟产生的竞争冒险以及在逻辑值发生跳变时产生的毛刺。0.1 ms更新模块里有信号周期测量环节,利用系统时钟对Sig_in的高电平进行计数,每一个时钟上升沿计数一次。在系统工作过程中,输入信号频率会在中心频率附近振荡,因此计数值也会随之跳变,0.1 ms更新模块会把在0.1 ms内出现次数最多的计数值N1送入动态分频器中。当系统谐振频率发生变化时,ADPLL的中心频率也会随着系统谐振频率动态变化,从而实现了动态分频。改进后的全数字锁相环的锁相范围为10 Hz~1 MHz。

2.3 ADPLL的改进方案

采用线圈结构和参数配置实现ZVS[22-23],系统输入阻抗角没有进行闭环控制,会随着参数的变化而变化,无功损耗也会随之波动,因此并不能使系统维持在一个最优阻抗角状态。针对这个问题,在ADPLL中加入了动态时滞模块,使得输出信号超前输入信号一个固定角度α,这样既能使系统有一个良好的ZVS特性,又可保证系统无功损耗处于一个较低的水平。

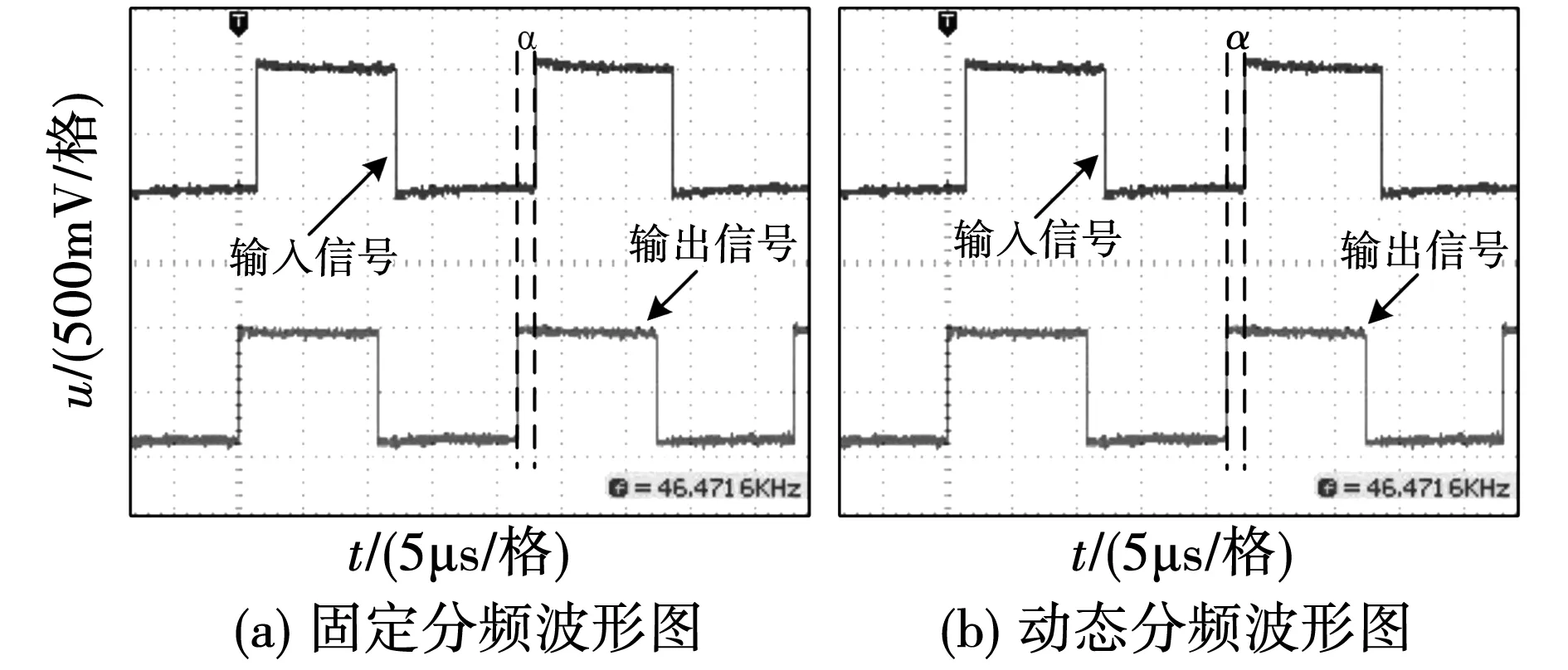

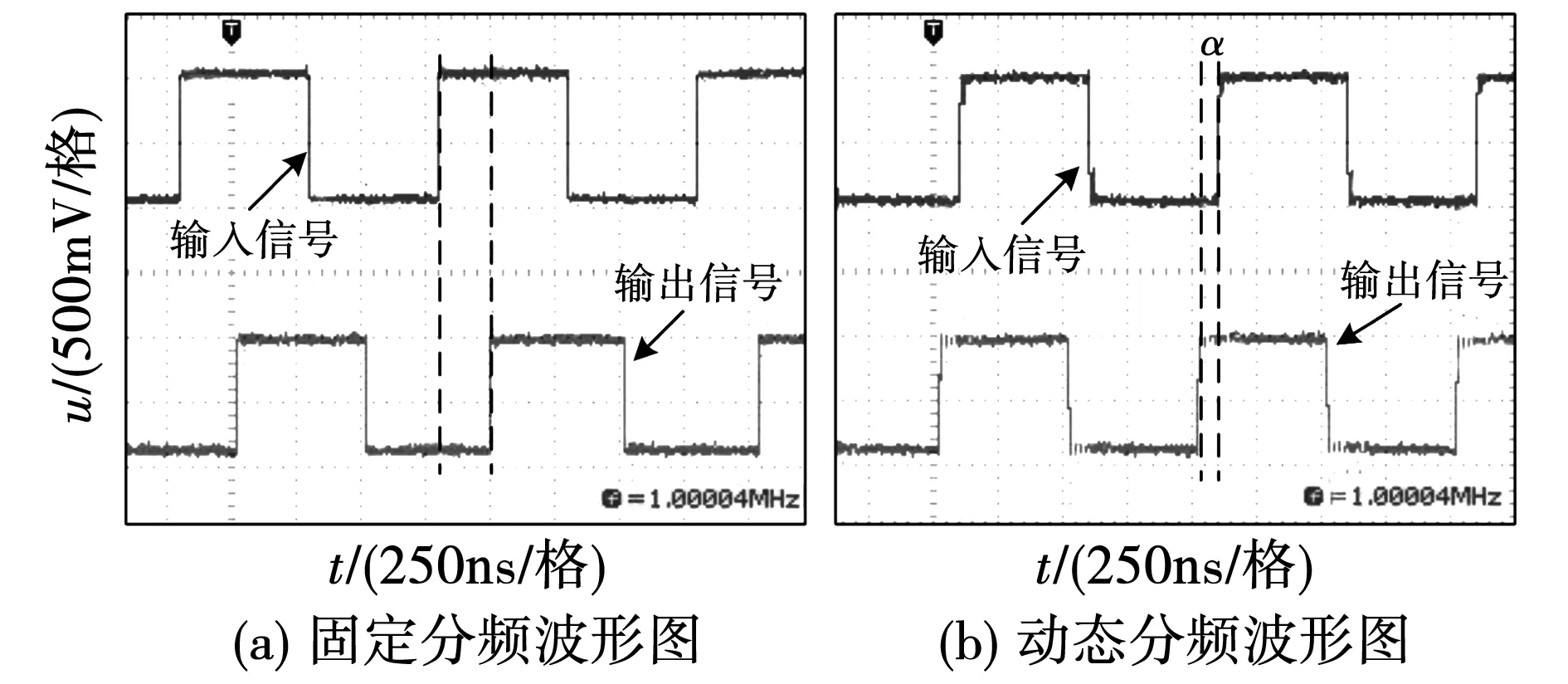

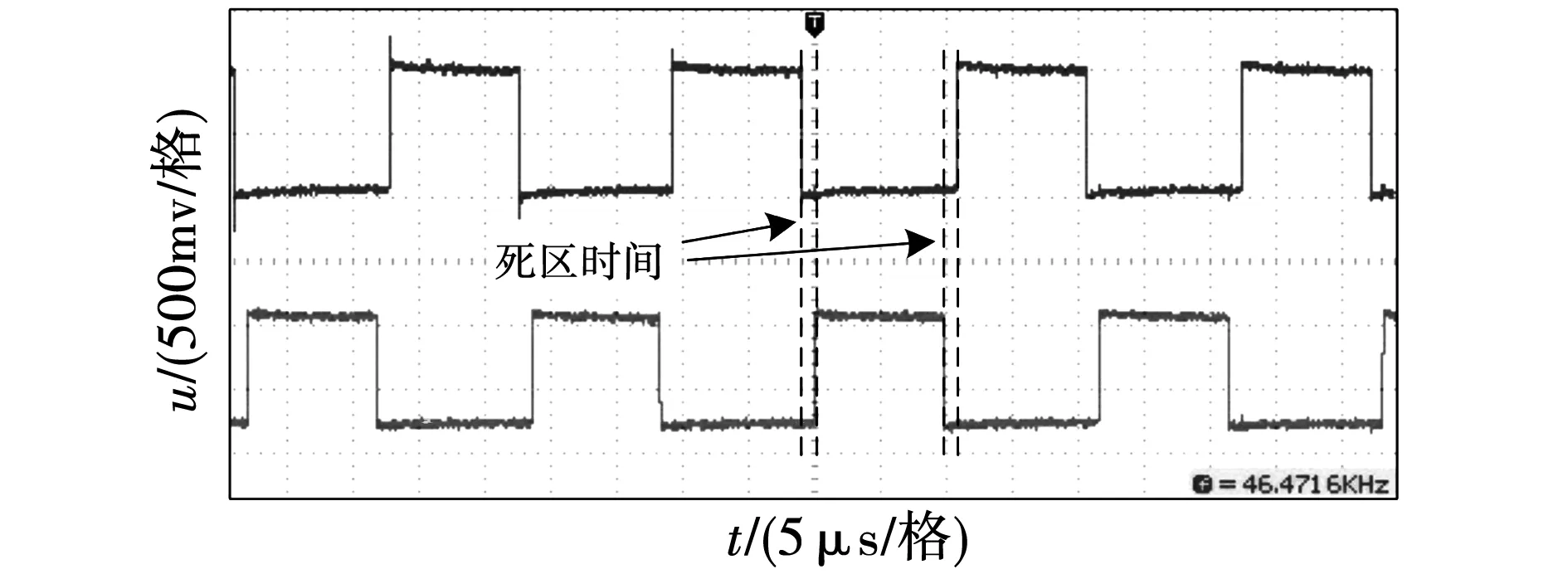

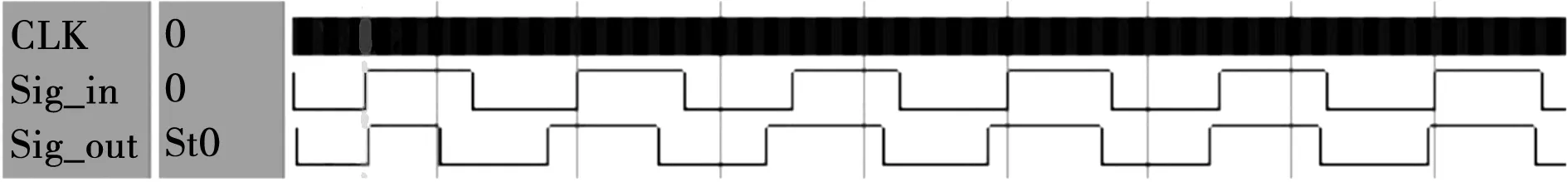

动态延时输出部分由信号宽度测量和动态时滞两个模块组成。信号宽度测量模块对输入信号周期进行计数,每个时钟的上升沿计数一次,并将计数值N输出给动态时滞环节中。动态时滞环节内设两个计数器,计数器1用来延迟信号输出,当检测到动态分频器输出信号为低电平时开始计数,计数到N-αN/180时,输出信号置1,其中α为输出超前角度。计数器2用来生成和输入信号相同周期的信号,计数到N时输出信号电平反转。当输入信号频率发生变化时,计数器值也会随之动态调节,从而实现了输出信号超前输入信号一个固定角度α。设置α=20°,通过示波器分别采集46.4 kHz、1 MHz和19.5 Hz频率下波形对比图,如图6~图8所示。

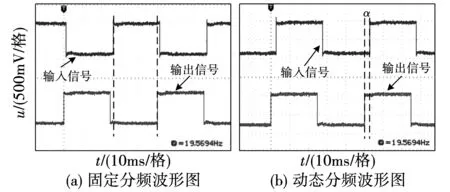

图6 两种分频方式下fin=fout=46.4 kHz波形图Fig.6 Waveform diagram of fin=fout=46.4 kHz in two frequency division modes

图7 两种分频方式下fin=fout=1 MHz波形图Fig.7 Waveform diagram of fin=fout=1 MHz in two frequency division modes

由图3~图8对比可得,当频率为46.4 kHz时,无论是固定分频还是动态分频,输出信号都会超前输入信号α度。但当把频率升到1 MHz或降到19.5 Hz,固定分频情况下,输入信号和输出信号之间存在较大的相位差,系统失锁;动态分频情况下,不仅可以快速完成锁相,而且可以使输出信号稳定超前输入信号α度。因此,在ADPLL中添加动态时滞部分和动态分频部分,不仅提高了锁相范围,还提高的系统供电的稳定性。

图8 两种分频方式下fin=fout=19.5 Hz波形图Fig.8 Waveform diagram of fin=fout=19.5 Hz in two frequency division modes

2.4 WPT系统的设计与实现

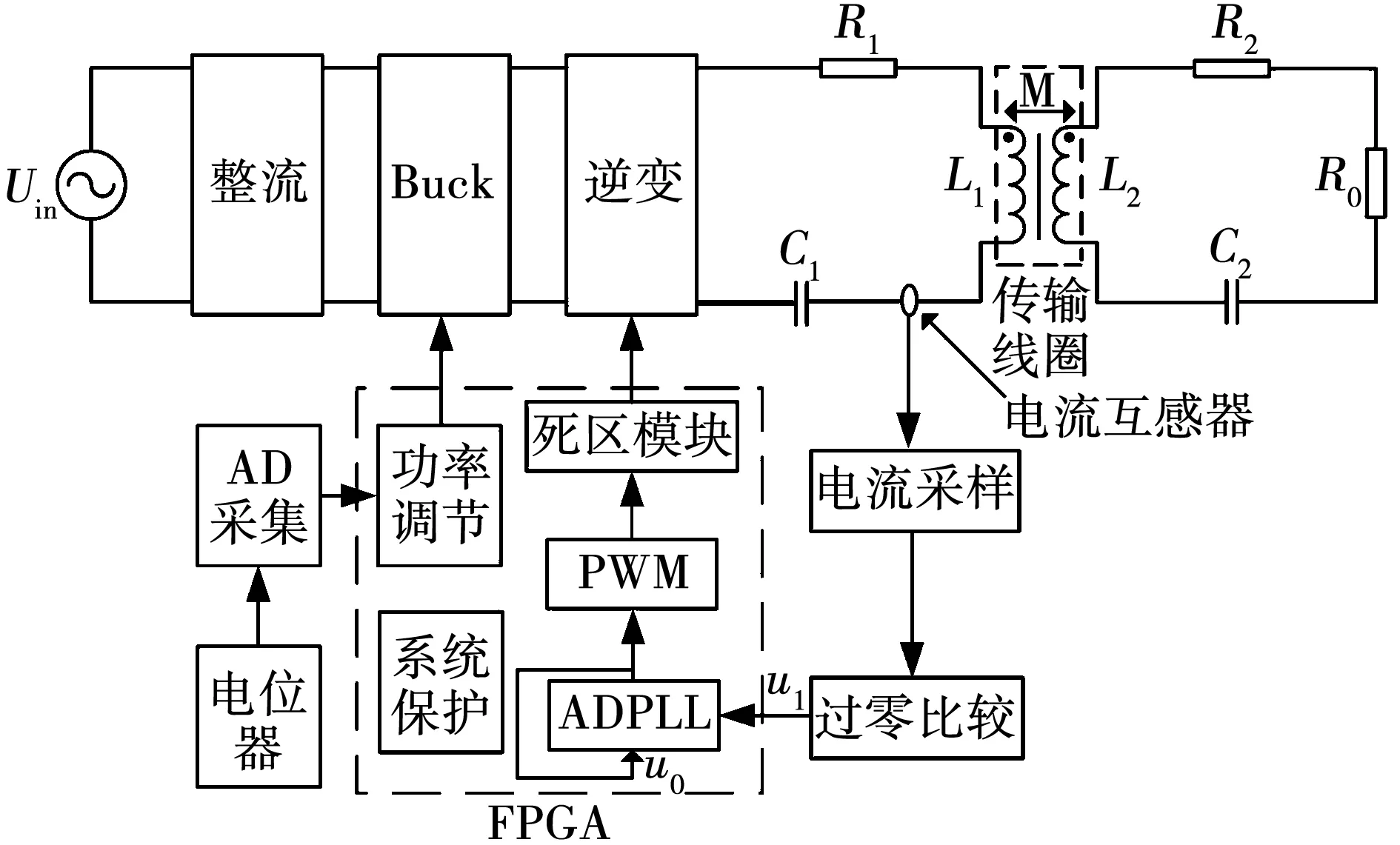

WPT控制系统由频率跟踪控制和功率调节控制两部分组成。频率跟踪控制系统由电流采样、过零比较、ADPLL、PWM和死区模块等五部分组成。功率调节控制系统由功率调节、AD采集和系统保护等三部分组成。控制系统的整体结构图如图9所示。

图9 控制系统整体结构图Fig.9 Overall structure of the control system

本文使用Altera公司EP4CE10F17C8型号的FPGA作为频率跟踪控制系统和功率调节控制系统的控制器,频率跟踪算法实现的具体过程为:

1)系统正常工作时受到干扰系统谐振频率发生改变;

2)电流采样模块实时检测发射线圈的电流,得到线圈谐振电流i0;

3)采样到的电流信号i0经过50:1的电流互感器,将大电流信号转换为小电流信号i1;

4)过零比较器将小电流信号转化为同频同相的电压方波信号u1;

5)电压方波信号u1送至ADPLL的输入端,ADPLL将u1与反馈信号u0比较,经过运算调整频率消除电压电流相位差,生成与i0同频同相的电压方波信号u2;

6)电压方波信号u2输入到PWM模块的输入端,经过死区模块,生成四路PWM波;

7)FPGA将四路PWM波分别输送至MOSFET的VT1、VT2、VT3、VT4,完成频率跟踪。

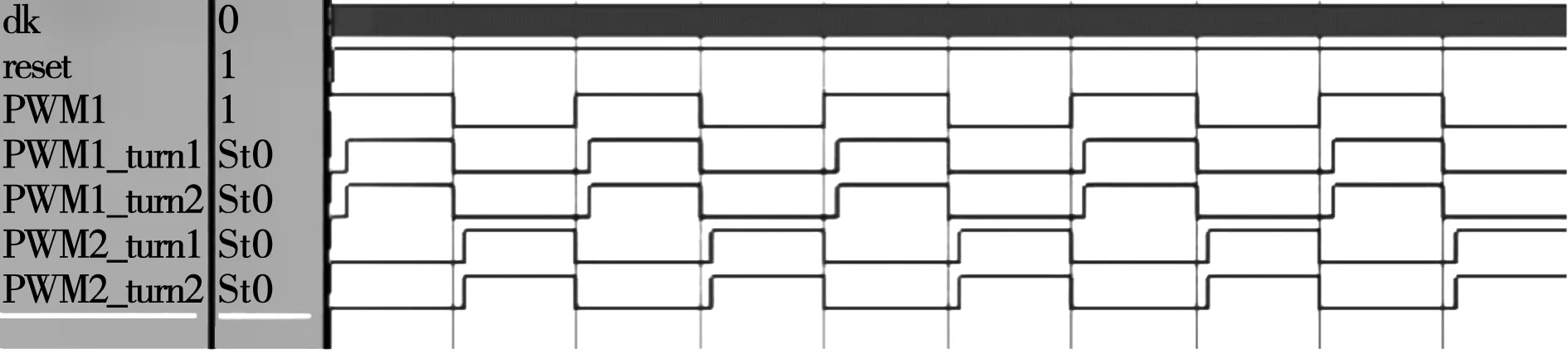

具有死区时间的四路PWM波形Modelsim仿真图如图10所示。通过示波器采集的具有死区时间的PWM波形图如图11所示。

图10 具有死区时间的四路PWM波形仿真图Fig.10 Four-channel PWM waveform simulation diagram with dead time

图11 具有死区时间的PWM波形图Fig.11 PWM waveform diagram with dead time

功率调节控制系统的具体实现过程为:AD采集模块采集电位器上的电压值,并通过FPGA内部ADC芯片将模拟电压值转换为数字信号,输入到功率调节单元。功率调节单元根据输入的数字信号调节Buck电路的占空比,以此来调节系统的输出功率。为了保护电源供电的安全性和可靠性,加入了系统保护部分,系统保护由过流保护单元和过温保护单元组成。当检测到采集的直流母线上的电流超过电流限幅值或当温度传感器检测到MOSFET散热片上的温度超过基准值后,都会关闭驱动Buck电路的PWM波,起到系统保护的功能。

本文采用Verilog语言,根据前文所述的改进的ADPLL自顶向下设计,实现了上述的WPT控制系统。为了提高ADPLL的最小分辨率并减小全数字锁相环的稳态误差,应选取频率较高的系统时钟,因此本文利用Altera这款FPGA自带的pll ip核将开发板50 MHz晶振转为250 MHz系统时钟。全数字锁相环的RTL顶层视图如图12所示。

图12 全数字锁相环的RTL顶层视图Fig.12 RTL top level view of all digital phase locked loop

3 仿真分析

3.1 锁相环仿真

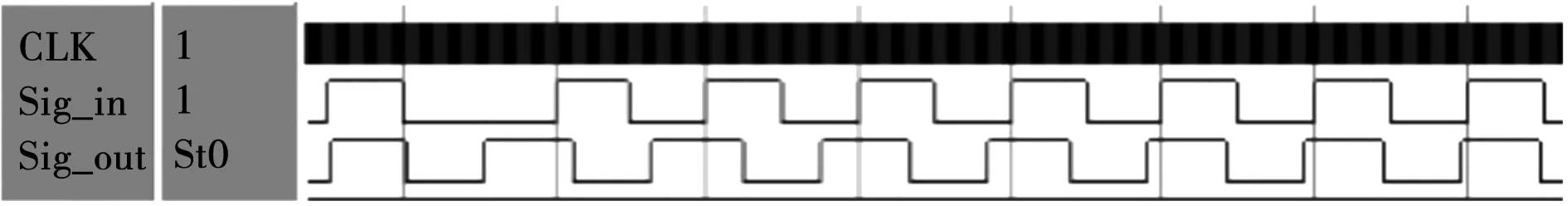

本文采用Modelsim软件对该锁相环进行功能仿真,设置超前角度α=8.5°。当输入信号频率由46.4 kHz跳变到30 kHz的Modelsim仿真图如图13所示,当输入信号相位突然改变180°的Modelsim仿真图如图14所示。

图13 输入信号频率由46.4 kHz跳变到30 kHz时跟踪 过程仿真图Fig.13 Simulation diagram of the tracking process when the input signal frequency jumps from 46.4 kHz to 30 kHz

图14 输入信号相位跳变180°时的跟踪过程仿真图Fig.14 Simulation diagram of the tracking process when the input signal phase jumps 180°

图中:Clk为时钟信号;Sig_in为ADPLL的输入信号;Sig_out为ADPLL的输出信号。

从图13中可以得出:当输入信号Sig_in频率由46.4 kHz跳变到30 kHz后,经过6个信号周期完成了锁相。从图14中可以得出:当输入信号Sig_in相位突然改变180°后,经过6个信号周期完成了锁相。从仿真结果可以得出:在输入信号发生突变之后,该ADPLL会快速响应,首先完成跟踪频率,然后在几个周期内就可以完成锁相,因此该ADPLL具有锁相速度快,锁相精度高等优点。不仅如此,在动态时滞模块的作用下,快速完成跟踪频率和锁定相位的同时,还可以使输出信号超前输入信号一个固定的角度α。

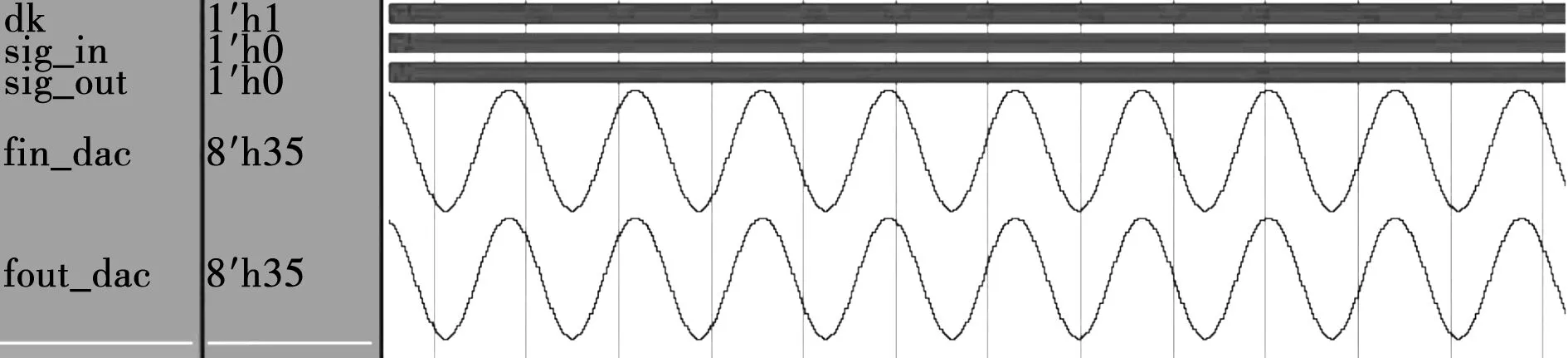

把输入信号和输出信号分别接上DAC模块,将数字信号转换为模拟信号,得到的仿真图如图15所示。其中fin_dac为输入信号sig_in经过DAC模块转化为的模拟信号,fout_dac为输入信号sig_out经过DAC模块转化为的模拟信号,由仿真图可见该锁相环具有良好的锁相性能。

图15 输入和输出信号转换为模拟信号仿真图Fig.15 Input and output signal conversion to analog signal simulation diagram

3.2 系统阻抗角仿真

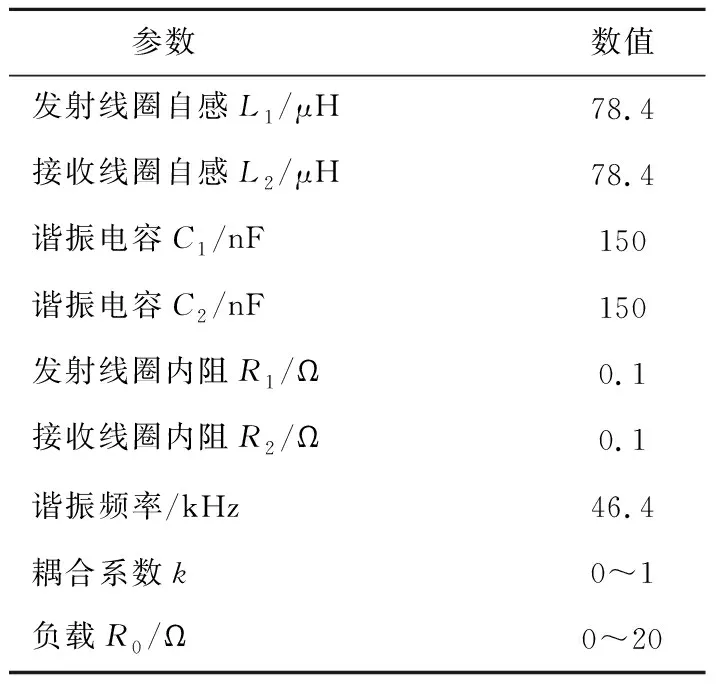

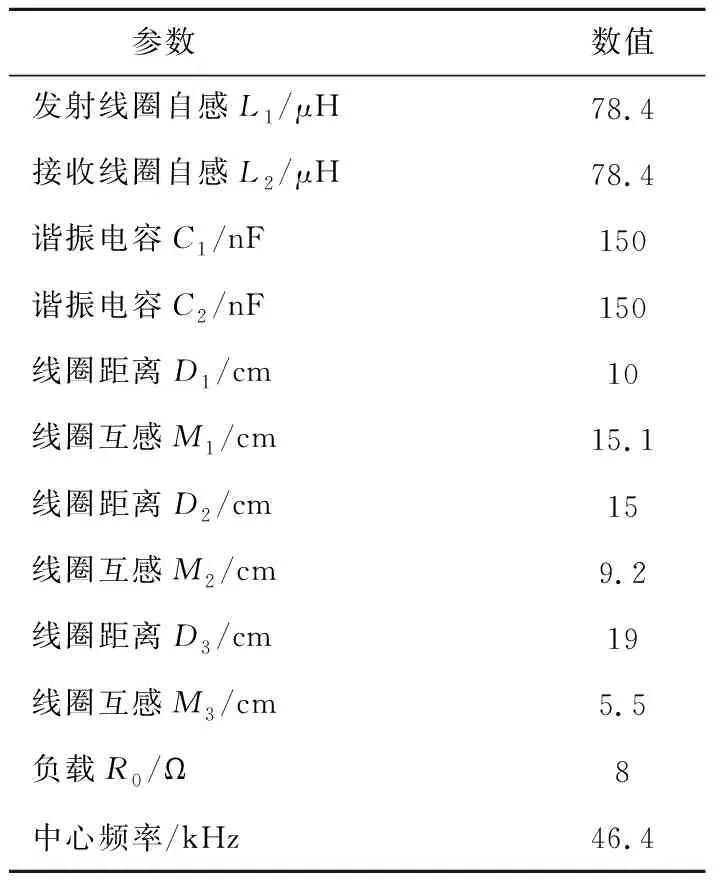

为了更好地研究系统容性、阻性和感性与不同传输距离和不同负载之间的关系,采用Matlab软件对式(12)进行仿真。仿真参数如表2所示。

表2 仿真模型的参数

按照表2所示参数进行仿真,仿真结果如图16所示。

图16 定频工作系统阻抗角Matlab仿真图Fig.16 Matlab simulation diagram of impedance angle of fixed frequency working system

由仿真结果可知:系统定频工作,当负载和耦合系数较小时,系统有较为明显的容性、阻性和感性的变化;当负载较大时,随着耦合系数的增大,系统由感性趋于阻性;当耦合系数较大时,随着负载的增大,系统由容性趋于阻性。因此系统定频工作,在线圈和谐振电容等参数固定的情况下,系统阻抗角与传输距离和负载大小都有关系。

4 实验验证

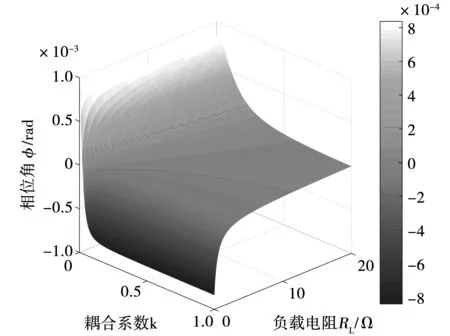

为了更好地验证仿真结果以及该系统的可行性,制作了一台实验样机并搭建了实验平台如图17所示。

图17 WPT系统实验平台Fig.17 WPT system experiment platform

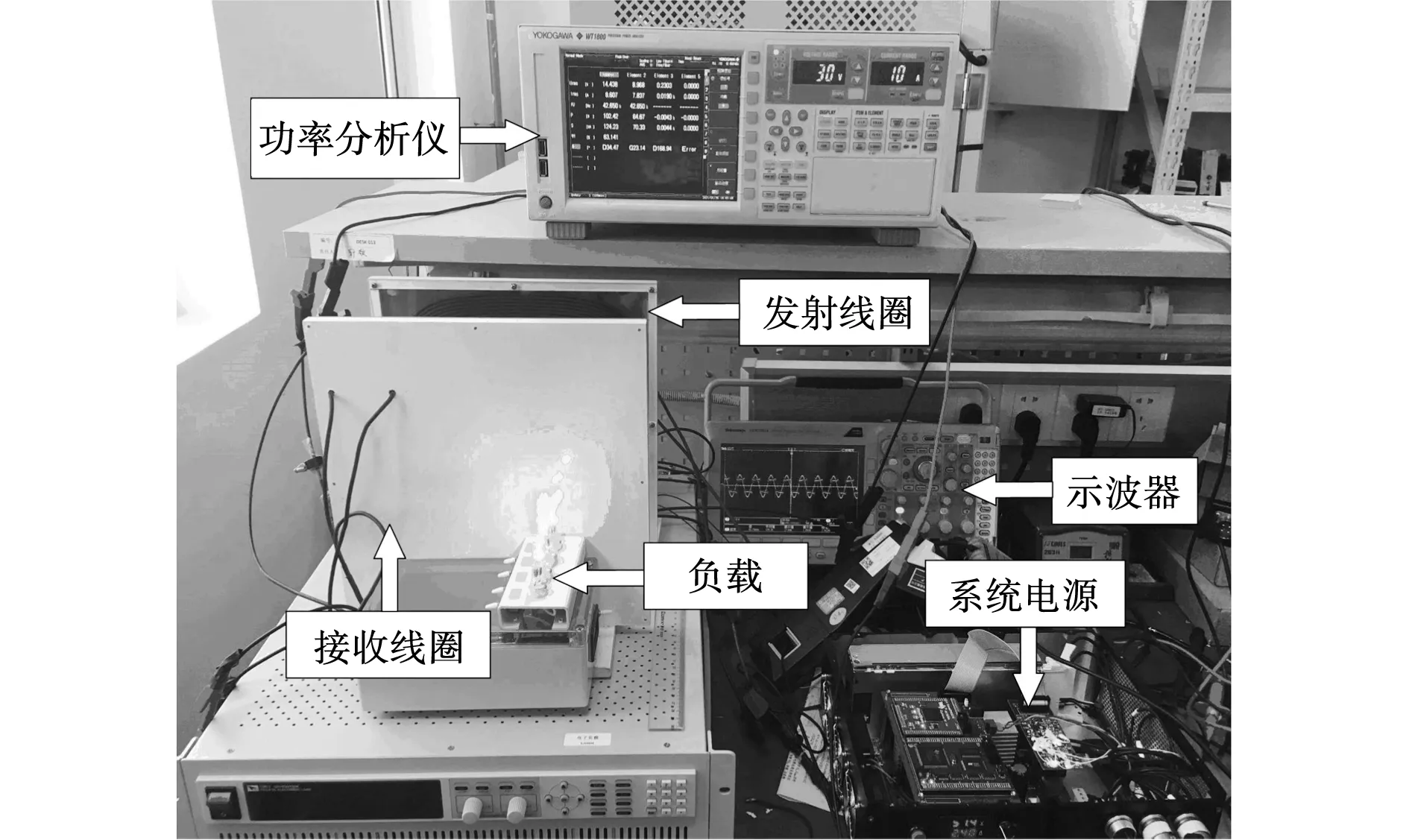

该实验平台包括高频交流电源、发射线圈、接收线圈、示波器、功率分析仪和负载等部分。其中高频交流电源由整流电路、降压斩波电路、逆变电路以及FPGA控制电路组成,逆变电路开关管采用160N15T2型号的MOSFET,驱动型号为MIC4421。实验系统的主要参数见表3。

表3 实验系统主要参数

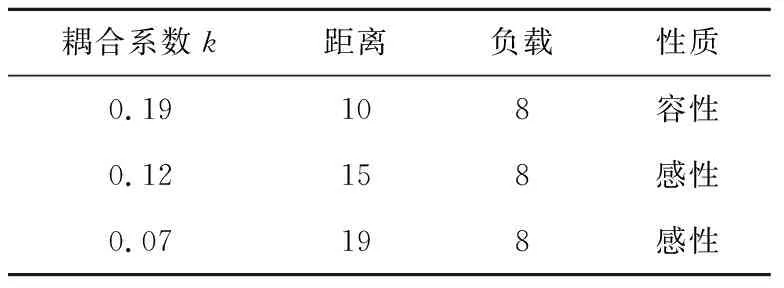

当两线圈距离改变时,线圈的谐振频率也会随之变化。系统定频工作情况下,电源输出频率为46.4 kHz,不会随着传输距离的变化而变化;频率跟踪情况下,电源输出频率会自动跟踪线圈谐振频率。为了防止逆变器上下桥臂同时导通,造成开关管损坏,应设定死区时间,鉴于所选MOSFET特性,设置死区时间为600 ns。死区时间所对应的角度φ=360°×f×td,其中f为开关管频率,单位是Hz,td为死区时间,单位是s,因此本文设置的死区时间所对应的角度为9.8°。为了保证ZVS软开关的实现,输入MOSFET的驱动电压应在其电流过零前为高电平,其次考虑到抑制逆变器输出电压极性反转现象,防止电压尖峰造成开关管损坏,开关管的驱动电压和流过其电流的相位差应大于死区时间的一半并留有一定裕量,因此本文所设置的锁相环相位角α=8.5°,使系统工作在弱感性状态。通过示波器分别采集线圈距离为10、15和19 cm的逆变器输出电压和发射线圈电流相位图。当负载为8 Ω,线圈距离分别为10、15和19 cm时,系统所呈现的特性如下表4所示。

表4 8 Ω负载系统所呈特性

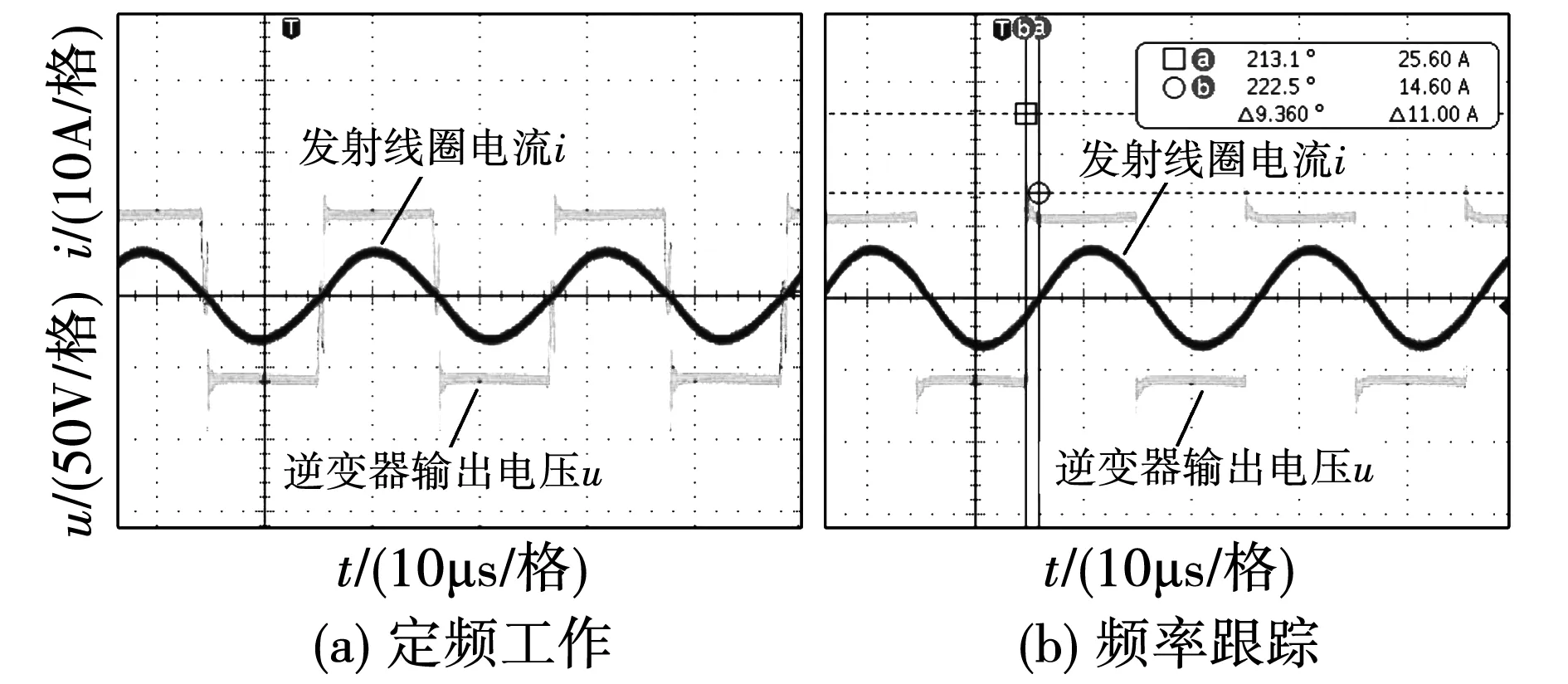

1)距离10 cm时电压电流相位图如图18所示。系统定频工作情况下,电流超前电压,呈弱容性,负载功率为310.54 W,传输效率为79.7%;频率跟踪情况下,系统频率为49.37 kHz,电压超前电流9.36°,呈弱感性,负载功率为334.68 W,传输效率为86.4%。

图18 线圈距离为10 cm时,电压电流相位图Fig.18 When the coil distance is 10 cm,the voltage and current phase diagram

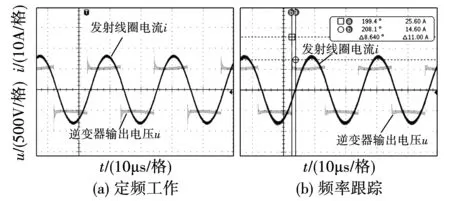

2)距离15 cm时电压电流相位图如图19所示。系统定频工作情况下,电流滞后电压,呈感性,负载功率为582.59 W,传输效率为74.5%;频率跟踪情况下,系统频率为46.55 kHz,电压超前电流8.64°,呈弱感性,负载功率为591.67 W,传输效率为76.1%。

图19 线圈距离为15 cm时,电压电流相位图Fig.19 When the coil distance is 15 cm, the voltage and current phase diagram

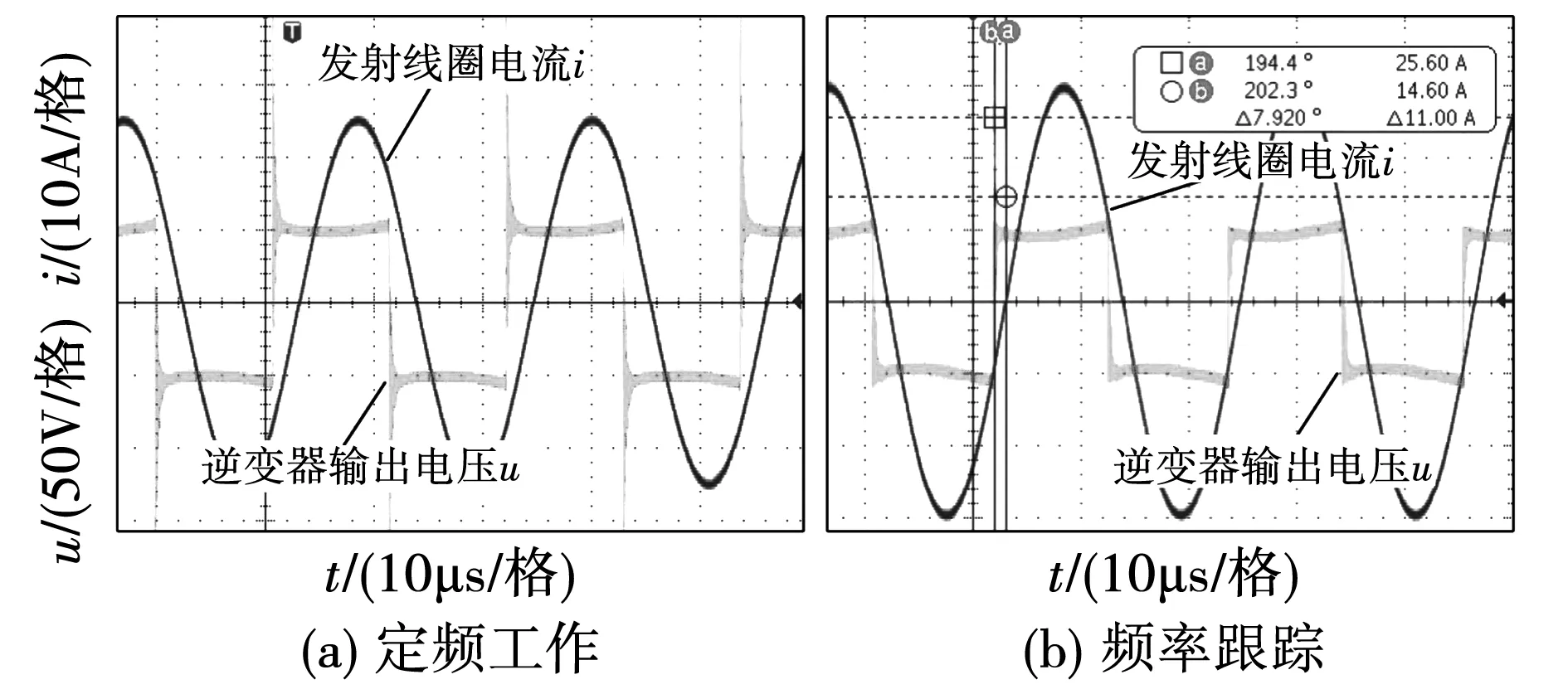

3)距离19 cm时电压电流相位图如图20所示。系统定频工作情况下,电流滞后电压,呈感性,负载功率为618.82 W,传输效率为63.2%;频率跟踪情况下,系统频率为46.04 kHz,电压超前电流7.92°,呈弱感性,负载功率为704.05 W,传输效率为71.3%。

图20 线圈距离为19 cm时,电压电流相位图Fig 20 When the coil distance is 19 cm,the voltage and current phase diagram

5 结 论

本文改进了传统全数字锁相环,提出了采用ADPLL对感应耦合式无线电能传输发射线圈电流频率和相位进行跟踪的方法。动态分频和自适应模值选择模块,提高了锁相范围,解决了锁相时间和锁相精度之间的矛盾。动态时滞模块可以使系统呈弱感性,以保证ZVS软开关实现,从而提高系统整体效率。从仿真和实验结果可以看出当线圈距离发生改变时,系统能够自动跟踪谐振频率并使其工作在弱感性状态下。在相同的线圈距离下,有频率跟踪比无跟踪状态传输功率和效率有明显提高。在系统工作过程中,电流始终跟随电压,呈弱感性,没有容性、阻性或感性的变化,提高了系统工作的稳定性。