面向申威处理器的高性能电源拓扑结构设计

高剑刚,周培峰,袁 博,杨培和,郑 浩

(1.国家并行计算机工程技术研究中心,北京 100190;2.江南计算技术研究所,江苏 无锡 214083)

0 引 言

随着处理器体系架构和生产工艺的不断创新发展,申威众核处理器的性能不断提升,频率越来越快、供电电压越来越低,对功耗需求也越来越大,电压稳定性和瞬态响应对供电单元的设计要求也越来越高[1,2]。近年来,基于脉冲宽度调制(Pulse Width Modulation,PWM)控制信号的多相开关电源,广泛应用于板卡级高性能芯片的核心供电设计中[3,4]。但是,当芯片供电需求超过PWM控制器输出相数时,业界通常采用单路信号控制多路功率器件的架构。该架构虽然可以在一定程度上满足供电需求,但是对于处理器电源,特别是电压稳定性和瞬态响应特性,会有比较大的影响和限制[5,6]。本文针对申威众核处理器供电需求,提出采用PWM控制器NCP4208和Dr-MOS功率芯片FDMF6823C等核心器件,结合ISL6617倍相器,设计开发了1种电源拓扑结构。其通过电源分配网络的目标阻抗获取,优化布局结构,可有效增强电源供电稳定性,扩展性良好,最高可扩展至1 000 A输出能力,满足高性能众核处理器等芯片的低电压、大功率、大波动供电需求[7]。

1 系统设计

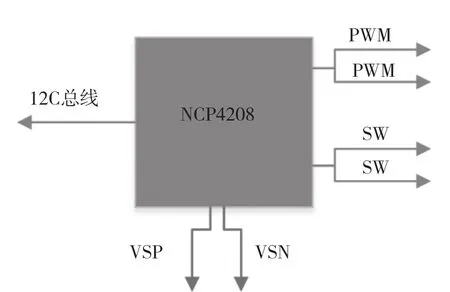

根据众核处理器的供电需求特点,电源系统的PWM控制器选用NCP4208。该控制器采用同步整流和8相交错并联技术,可大幅提高转换效率和功率密度,同时支持内部集成电路(Inter-Integrated Circuit,I2C)通信,远程在线配置各种电气参数。功率芯片选用FDMF6823C,该器件内部集成驱动器和功率MOSFET,最大输出电流为50 A。PWM倍相器选用ISL6617,该芯片支持2级倍相,可将NCP4208控制信号扩展至32相,有效扩展控制器驱动能力,增强电源稳定性,降低电源占板面积。同时,采用1片微控制单元(Microcontroller Unit,MCU)实现电源管理。电源系统拓扑结构如图1所示。

图1 电源系统拓扑结构

2 硬件设计

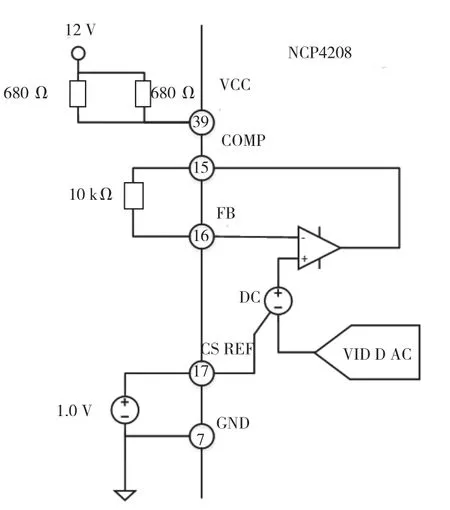

2.1 PWM控制器电路设计

通过PWM控制芯片NCP4208产生8相脉宽调制信号,再通过倍相器ISL6617将8相脉宽调制信号倍增至16相,进一步提高控制芯片驱动能力。通过外部引脚的高低电平控制NCP4208的输出启停。电压识别码(Voltage Identification Digital,VID)通过I2C接口设定。可以通过调节补偿元件的参数值改变反馈环路的稳定性。NCP4208可以对各路电流进行实时采样,并保证负载分配均衡,通过I2C端口读取工作状态和检测电压电流数值,对工作参数进行在线修改。PWM控制器原理如图2所示。

图2 PWM控制器电路原理

NCP4208的直流输出电阻可以通过I2C命令设为0,即输出电压不随负载增加而变化,保证输出电压始终为恒定数值。该电路在印刷电路板(Printed Circuit Board,PCB)布线设计时,须注意电源反馈差分信号线的电压检测正极(Voltage Sense Positive,VSP)和电压检测负极(Voltage Sense Negative,VSN),布线路径应保持平衡,并远离开关区域。

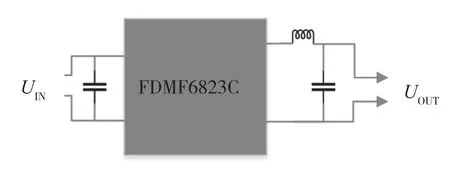

2.2 功率级电路设计

功率电路每相由1片型号为FDMF6823C的Dr-MOS芯片、电感以及输入输出电容组成。其中,Dr-MOS芯片中包含上、下金氧半场效晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)和驱动电路,采用贴装方式,有利于减少损耗和散热,功率级电路原理如图3所示。

图3 功率级电路原理图

FDMF6823C电流检测采用典型的电感直流电阻(Direct Current Resistance,DCR)检测方式,如图4所示。

图4 DCR电流检测原理

该信号连接至NCP4208相应的引脚,经内部采样获取输出电流值。同时,通过NCP4208的ILIM引脚电平来设置限流阈值,当引脚电平到达该阈值时,触发过流保护。

2.3 补偿电路设计

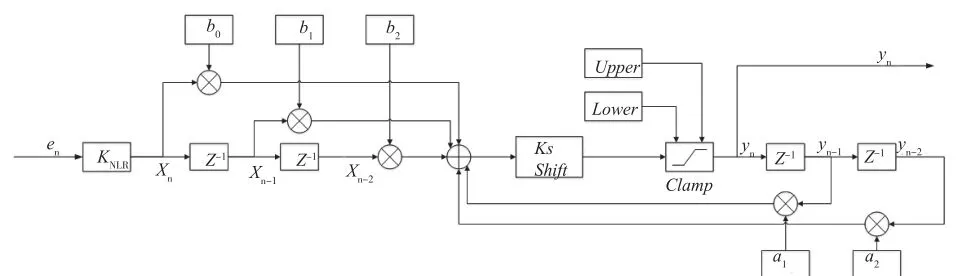

补偿器框架如图5所示。

图5 补偿器框架

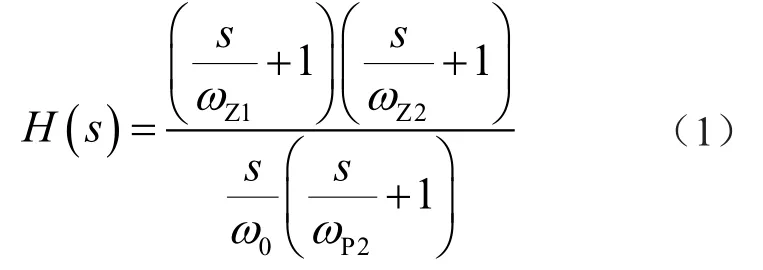

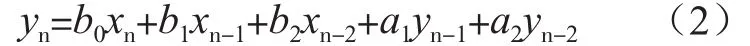

补偿电路传递函数公式为

式中:ωZ1与ωZ2为2个零点,用于抵消LC双重极点;ωP2为高频极点,用于消除高频噪声;ω0为直流增益,零极点用于消除直流误差,对应于模拟补偿器中的积分器。

上述传递函数在NCP4208中以离散化方式表示,其公式为

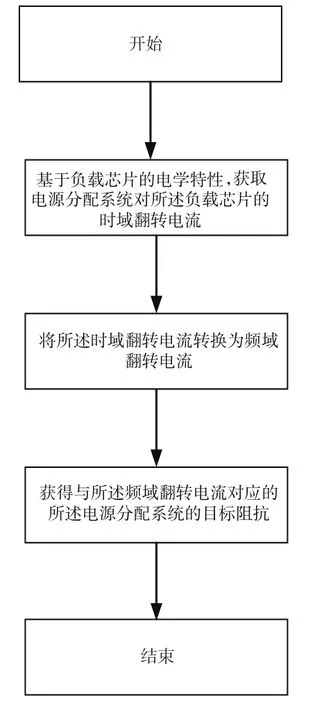

2.4 目标阻抗获取

基于众核处理器的电学特性,通过建立处理器核心电路的仿真模型,向仿真模型输入激励信号,获取处理器芯片对电源分配系统的时域翻转电流;通过傅里叶变换将时域翻转电流转换为频域翻转电流,获得与频域翻转电流对应的电源分配系统的目标阻抗,如图6所示。

图6 目标阻抗获取流程

目标阻抗公式为

式中:ZTarget为目标阻抗;USuppiy_Voltage为负载芯片的供电电压;RAllowed_Ripple为电源噪声容限;IF_Current为频域翻转电流。

2.5 电源Layout优化

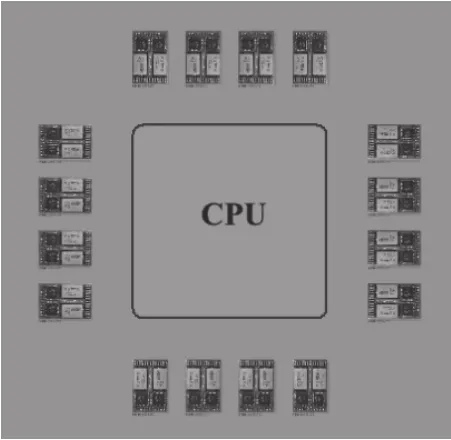

为应对低电压大电流的供电挑战,通过改进电源转换芯片的放置方式,在中央处理器(Central Processing Unit,CPU)四周布局放置,可以有效减小电源输出端到CPU负载端的距离,减小电源平面路径压降和功率损失,实现更高的电源供电性能。电源电路在CPU四面布局的结构如图7所示。

图7 电源供电电路在CPU四周的布局结构

3 性能测试

本电源系统测试时,以模拟电子负载代替处理器芯片进行相关实验,对PWM波形、静态纹波、动态特性、转换效率等进行测试,具体结果如下。

3.1 PWM波形

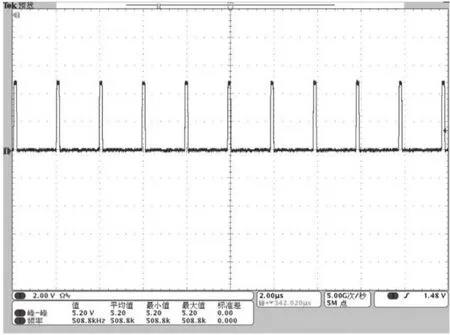

用示波器测试PWM信号的波形如图8所示。由图8结果可知,开关频率为508 kHz,与500 kHz设计值基本相吻合,控制信号稳定无抖动。

图8 PWM控制信号实测波形

3.2 静态纹波

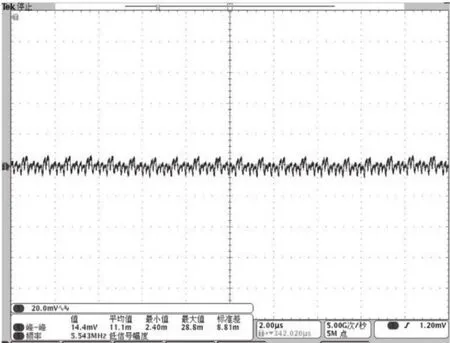

电子负载施加300 A负载电流,用示波器捕捉输出电压静态纹波,结果如图9所示。由图9结果可知,输出电压稳定,静态纹波峰峰值14.4 mV。

图9 静态纹波实测波形

3.3 动态特性

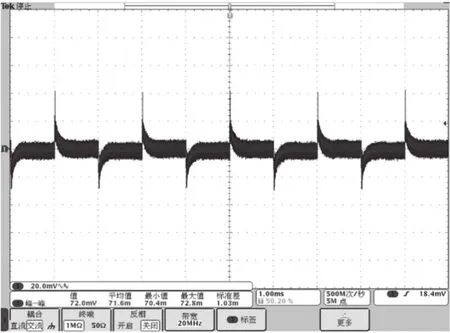

用电子负载施加动态负载(ΔI=300 A,di/dt=80 A/μs,fload=0.5 kHz,D=50%),用示波器捕捉输出电压波形,结果如图10所示。由图10可知,负载变化时,输出波动约为±50 mV,其中加载调整时间约为100 μs,去载调整时间约为100 μs。

图10 动态特性实测波形

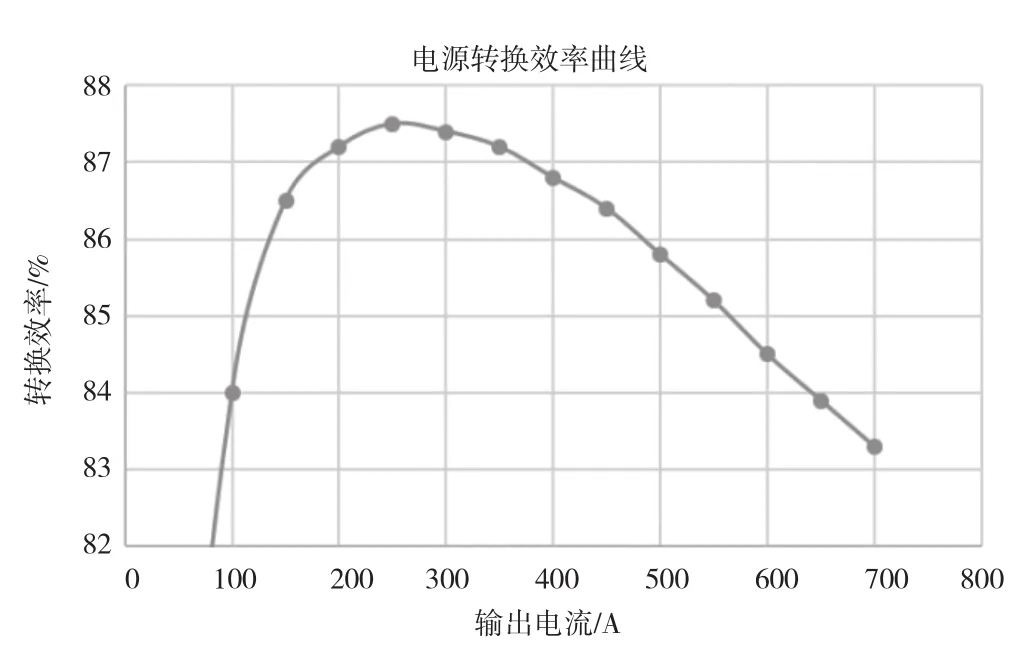

3.4 转换效率

用电子负载施加负载电流,调整负载电流大小,测试并记录输入输出电压和输入输出电流,并计算得出转换效率,结果如图11所示。由图11可知,转换效率最高可达87.5%。

图11 电源转换效率实测结果

4 结 论

本文面向申威众核处理器供电需求,提出并采用基于PWM控制器NCP4208和Dr-MOS功率芯片FDMF6823C设计了1种高性能可扩展的电源拓扑结构。通过目标阻抗获取,优化布局结构,有效提高了电源供电稳定性和并联特性,满足众核处理器等对供电能力、电压精度、动态特性等要求。同时,该拓扑结构可根据负载大小调整工作相数以适配不同功耗芯片的设计需求。实际测试结果表明,该电源系统的各项性能指标优良、运行稳定,能够满足众核处理器低电压、大功率、大波动供电要求,已成功应用在神威系列高性能计算机和多款高端服务器中,取得了良好的技术效益。