FLTD大规模气体开关同步触发技术研究

王志国,孙凤举,姜晓峰,降宏瑜,魏 浩,邱爱慈,楼 成,文振明

(1. 西北核技术研究所,西安 710024; 2. 西安交通大学,西安 710049)

快直线型变压器脉冲功率驱动源(fast linear transformer driver,FLTD)可直接产生百纳秒级电脉冲,无须脉冲压缩,是下一代快Z 箍缩驱动源中最有前景的技术路线[1-2]。为获得高峰值功率,FLTD需要数目庞大的开关同步工作,对开关提出了非常严苛的低抖动同步触发要求。大型FLTD脉冲源包含数万至数十万只的高功率气体开关,大规模气体开关同步触发是制约FLTD技术工程应用的瓶颈之一[3-4]。

目前,FLTD常规触发方法为单级模块引入4路触发脉冲,每路脉冲触发6~10只气体开关[5-7],为获得低抖动,触发脉冲幅值一般大于120 kV[8]。美国圣地亚国家实验室提出的Z-300(48 MA),Z-800装置(60 MA)概念设计[9],中国工程物理研究院提出的50 MA电磁驱动聚变大科学装置(50 MA、150 ns)概念设计均采用上述同步触发方式[10-14],需要引入数目庞大的高电压触发电缆,触发系统庞大、复杂,触发电缆可靠性难以保证。

针对上述问题,本文提出一种单级FLTD模块内置触发支路[15]、共用腔体FLTD组件触发延时线触发、单路FLTD级联触发的内置级联同步触发新方法,可大幅降低引入触发脉冲数目和触发系统规模;建立了12级串联共用腔体FLTD实验平台,实验验证了内置同步触发方法可行性,实验结果表明,内置级联触发方法可实现单路FLTD触发时序调控,各级触发支路开关抖动小于2 ns。

1 内置级联触发原理

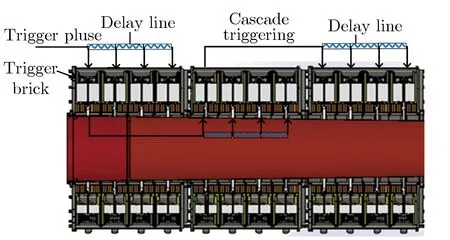

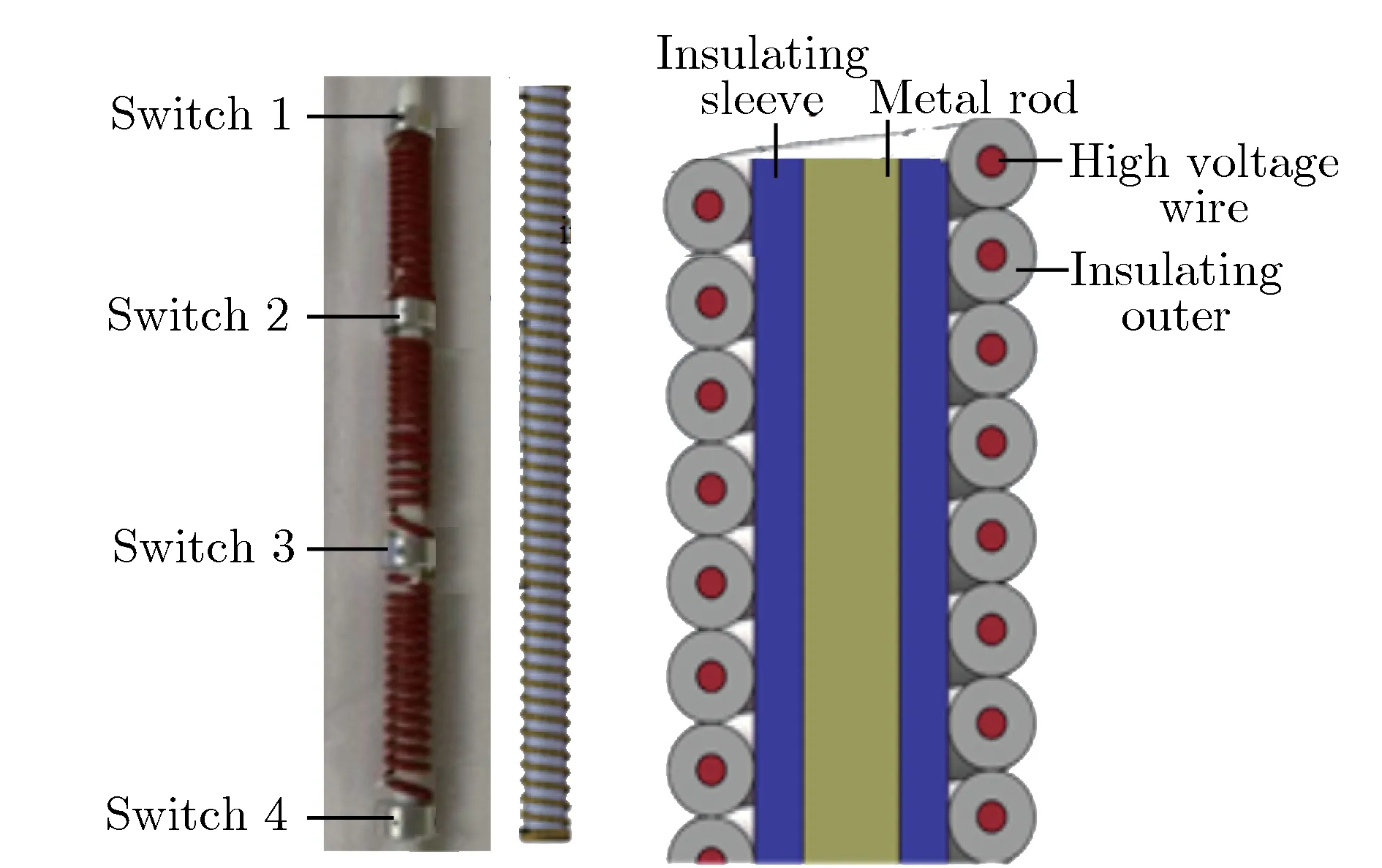

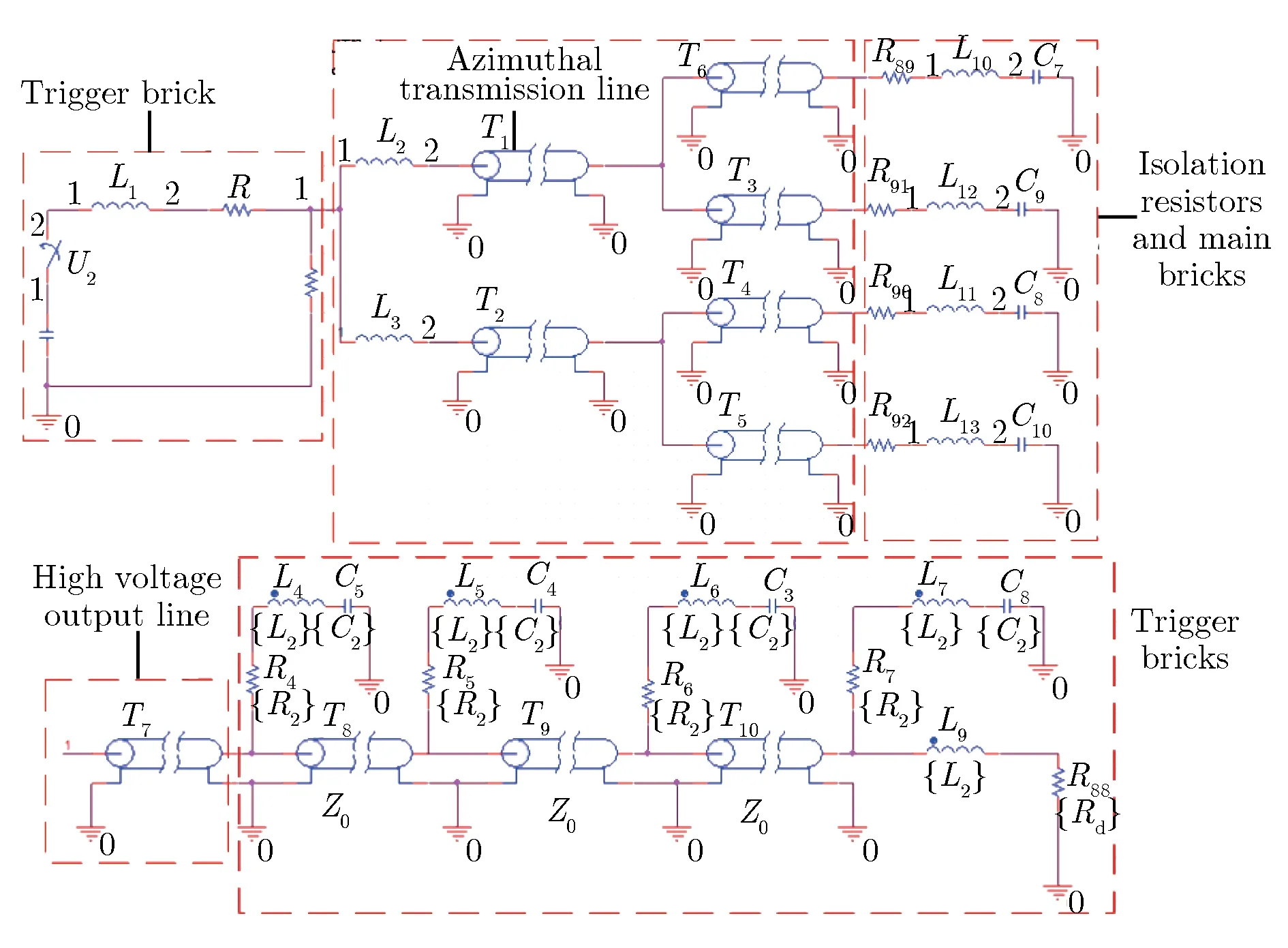

图1为多级串联FLTD内置级联触发原理示意图。多级FLTD模块共用一个外腔体,每级通过多根均匀分布的金属连接杆回流,每级FLTD单独放置一个支路用于触发其他并联支路,该支路称为触发支路,其他支路称为主放电支路。外部引入1路脉冲实现触发支路开关放电,触发支路产生电脉冲用于触发模块内主放电支路;4~6级FLTD模块串联构成1个FLTD组件,外触发脉冲经触发延时线触发组件内部的每级触发支路开关,触发延时线时延与次级电脉冲传输时间相同,实现组件内各级FLTD电脉冲按理想时序叠加;各个FLTD组件由前一个组件内部触发支路引出1路脉冲触发后一个组件内各级触发支路,实现单路FLTD的依次级联触发。

图1 多级串联FLTD内置级联触发原理示意图Fig.1 Schematic of inter-cascade trigger of multi-stage series FLTD

2 内置级联触发仿真模型

2.1 单级FLTD内置触发仿真模型

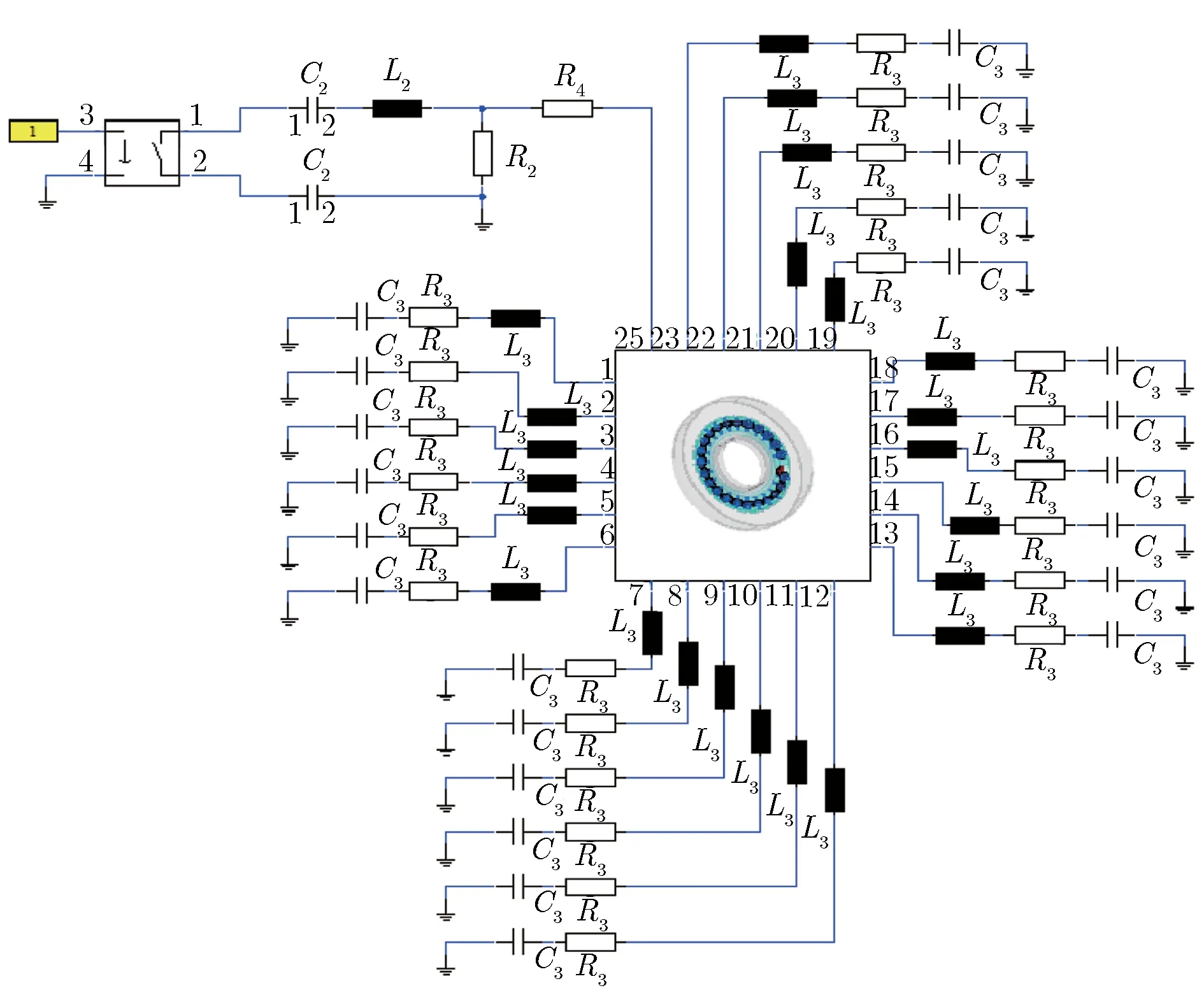

根据内置触发支路及角向传输线结构,建立场-路协同仿真模型如图2所示。其中,触发支路、主放电支路、触发隔离电阻及置地电阻等部分使用电路模型,元件参数均通过实际放电回路测量获得;角向传输线、中间绝缘板及外腔体等结构使用3维电磁模型,按器件实际材料及3维尺寸设置参数。其中:触发支路电容C2为50 nF;触发回路等效电感L为200 nH;触发回路等效电阻R4为0.3 Ω;置地电阻R2取2 kΩ;主放电支路等效为开关分布电容与主支路电容串联,开关等效电容C2为3 pF;发隔离电阻R3为300 Ω;发隔离电感L3为2 μH。

(b) Field-cricuit co-simulation model

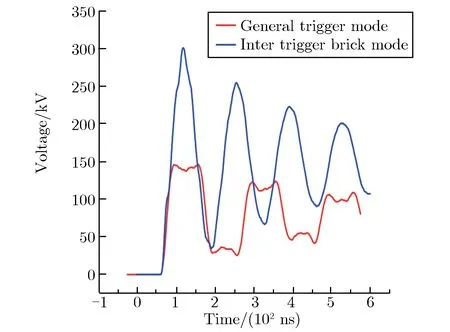

利用建立的场-路协同仿真模型分别获得了内置及常规触发方式下主支路开关的触发脉冲波形,如图3所示。内置触发方式触发支路充电电压为±80 kV,常规触发方式引入电脉冲140 kV/20 ns。常规触发方式下触发脉冲陡度为7.0 kV·ns-1,内置触发方式下触发脉冲陡度为7.4 kV·ns-1,且触发脉冲幅值更高(约为280 kV,是常规触发方式2倍),有利于主支路开关同步[16]。

图3 内置及常规触发方式下触发脉冲波形Fig.3 Waveforms of trigger pulses under inter and general trigger methods

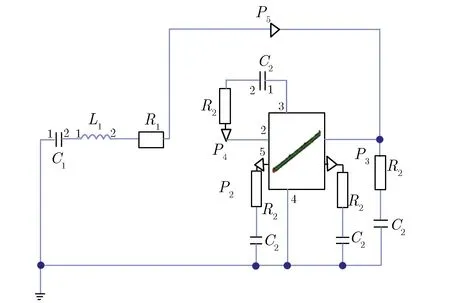

2.2 FLTD组件触发延时线仿真模型

建立触发延时线触发场-路协同仿真模型,如图4所示。其中,触发器及高压电缆、延时线末端电阻、触发隔离电阻及4级触发支路等部分使用电路模型,触发延时线使用3维电磁模型。电路模型中:触发器电容C1为25 nF;触发器回路电感L1为140 nH;等效回路电阻R1为0.1 Ω;触发高压电缆长度为10 m,阻抗为50 Ω;触发支路等效为开关分布电容与触发支路电容串联,等效电容C2为10 pF,触发隔离电阻R2为1 kΩ。

(a) Schematic of three-dimensional structure

(b) Field-cricuit co-simulation model

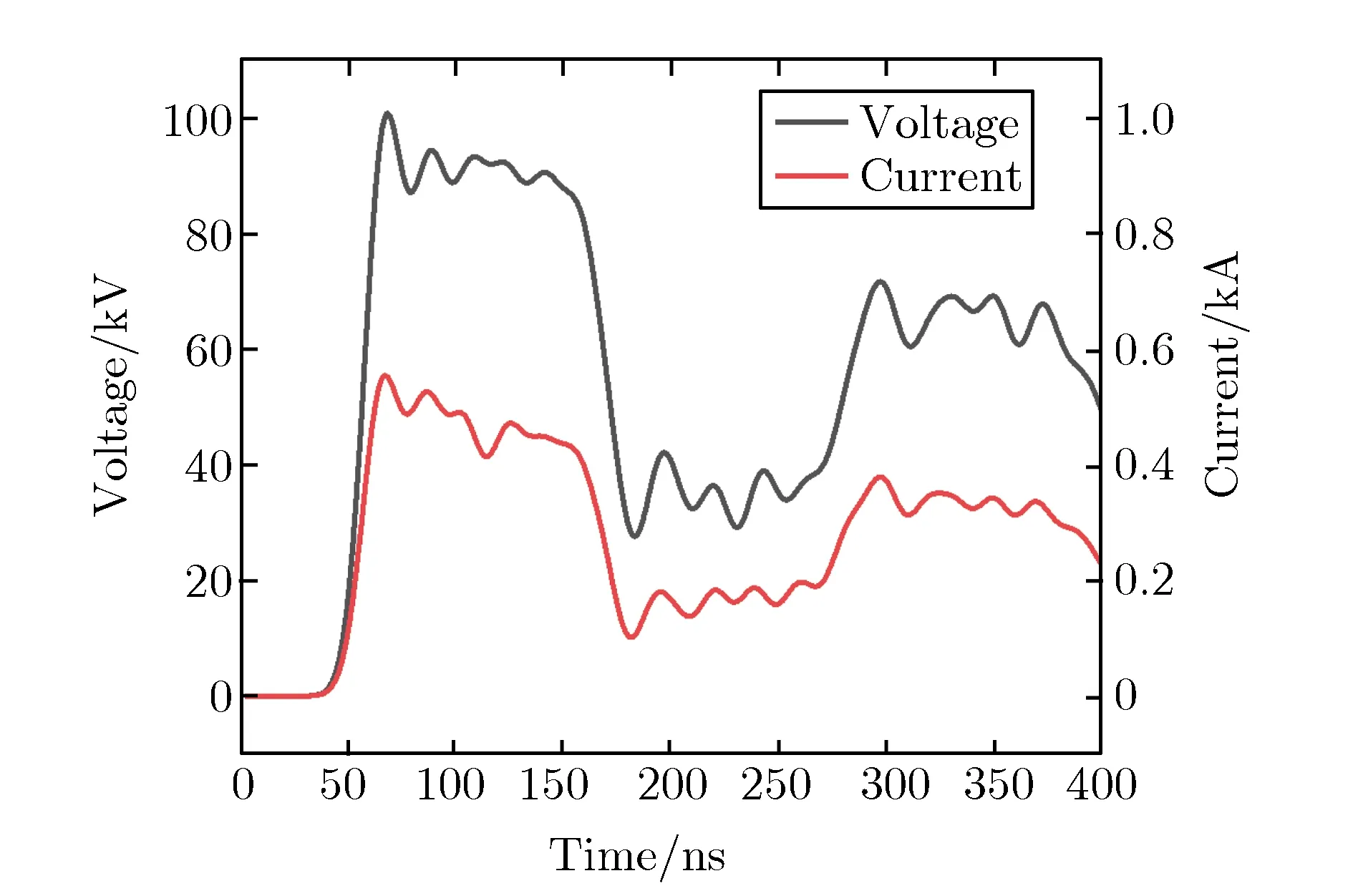

利用建立的场-路协同仿真模型获得了触发延时线触发方式下触发脉冲波形,如图5所示。

(a) Voltage and current waveforms of trigger delay line

(b) Trigger voltage waveforms of 4 stages

触发器输出前行波电压为60 kV时,触发延时线末端可获得幅值约为100 kV,前沿小于20 ns的触发脉冲,触发电流约为0.53 kA,计算触发延时线等效阻抗Z约为190 Ω。各级触发支路开关获得的触发脉冲幅值及前沿基本相同,各级延时约为6.0 ns,每级触发延时线长度为1.5 m,可得触发脉冲在触发延时线中的传输速率为0.25 m·ns-1。

2.3 多级串联FLTD级联触发仿真模型

建立了多级串联FLTD级联触发电路仿真模型,如图6所示。

图6 多级串联FLTD级联触发电路仿真模型Fig.6 Cricuit simulation model of multi-stage series FLTD

由图6可见,模型包括上游共用腔体单元内的触发支路、角向传输线、隔离电阻及主放电支路、高压引出线、下游共用腔体单元内的触发延时线、隔离电阻及触发支路等部分。内置触发支路参数与单级FLTD仿真模型相同,6个主支路参数等效为1个支路(其中1个支路为5个主支路参数等效),置地电阻R为2 kΩ,角向传输线阻抗Z1为60 Ω,高压引出线传输时间为5 ns,阻抗Z2与触发延时线阻抗Z3均为190 Ω。触发支路开关分布电容C2为10 pF,触发隔离电阻R2为1 kΩ。

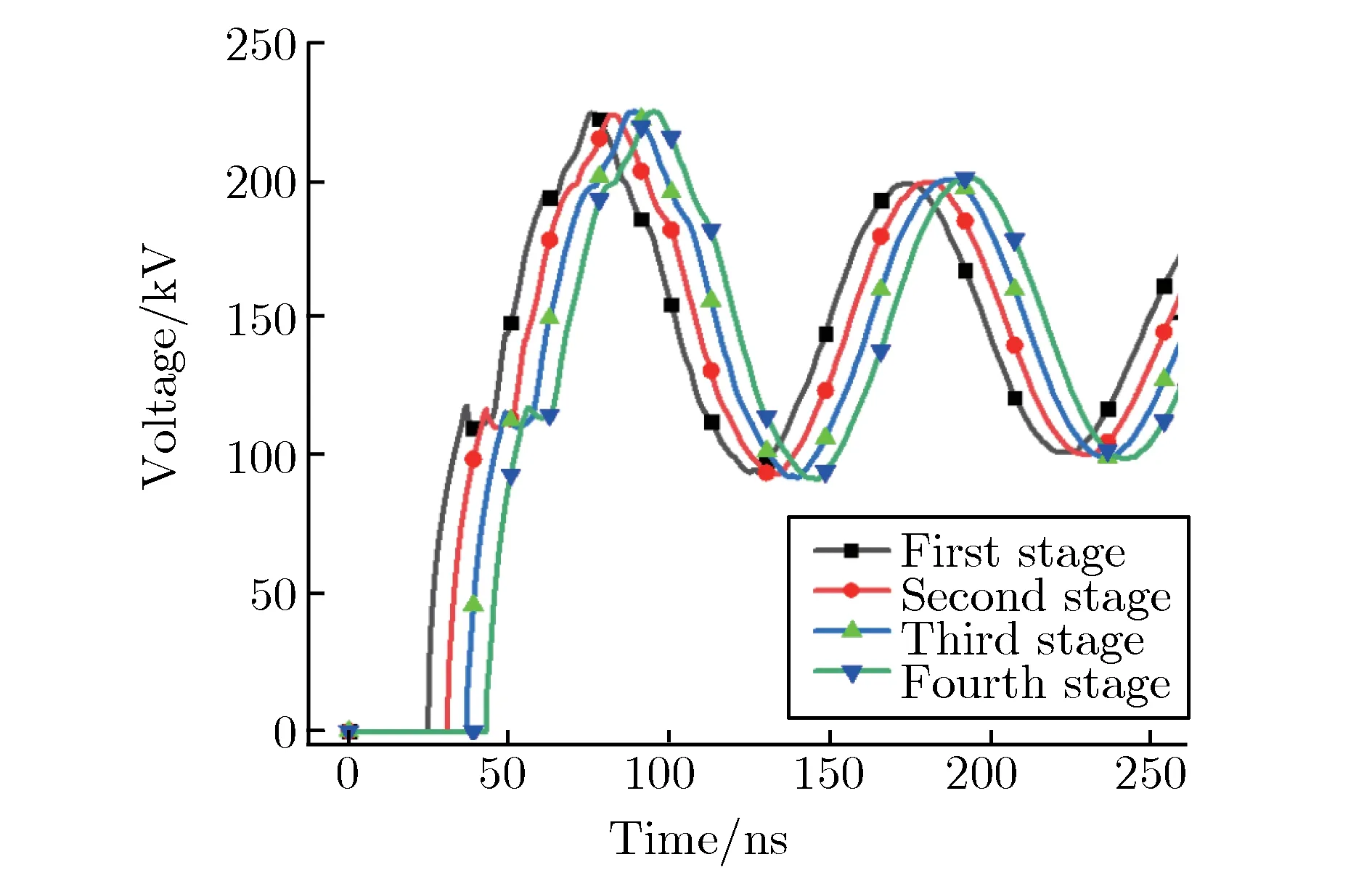

利用电路仿真模型获得了多级串联FLTD级联触发仿真波形,如图7所示。上游触发支路充电电压为±80 kV,经级联高压线馈入下游触发延时线的触发脉冲幅值约为225 kV,是触发支路充电电压的2.8倍,脉冲上升时间(0~100%)约为50 ns,在电压为120 kV处出现约10 ns的平顶。为获得较小的开关抖动,应使下游触发支路开关在触发脉冲到达120 kV之前导通。估算高压引出线传输时间为5 ns,次级电脉冲传输时间为39 ns(1.3 m水介质传输线),则下游触发支路开关导通时延为34 ns时,可实现多级串联FLTD次级电脉冲的理想时序叠加。

图7 多级串联FLTD级联触发仿真波形Fig.7 Simulation waveforms of cascade trigger pulses of multi-stage series FLTD

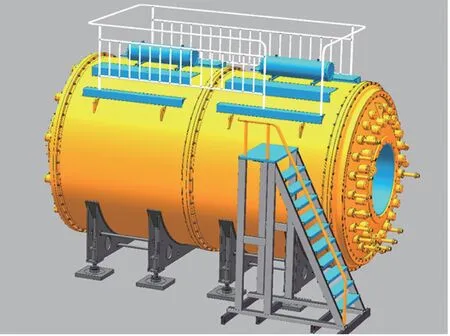

2.4 12级串联FLTD级联触发实验验证

建立了采用内置级联触发方法的12级串联共用腔体FLTD实验平台,如图8所示。这是国际上首台采用水介质传输线的太瓦级FLTD装置,总长度4.8 m,直径2.5 m,包含3个FLTD组件,276个主放电支路、12个触发支路,其中主放电支路电容器参数为100 kV/100 nF,触发支路电容器参数为100 kV/50 nF,每个组件由4级FLTD模块串联构成,每个FLTD模块采用内置触发支路触发,每个FLTD组件内部采用触发延时线触发,延时间隔固定为7.5 ns,FLTD组件之间采用级联触发,通过调节触发支路开关工作系数可在一定范围内调控触发时延。研制的12级串联FLTD装置仅需引入1路触发脉冲,6路充电电缆(正负各3路)和1路气路,大幅简化了辅助系统规模,同时可实现放电支路的原位在线维修替换。

(a) Design

(b) Picture

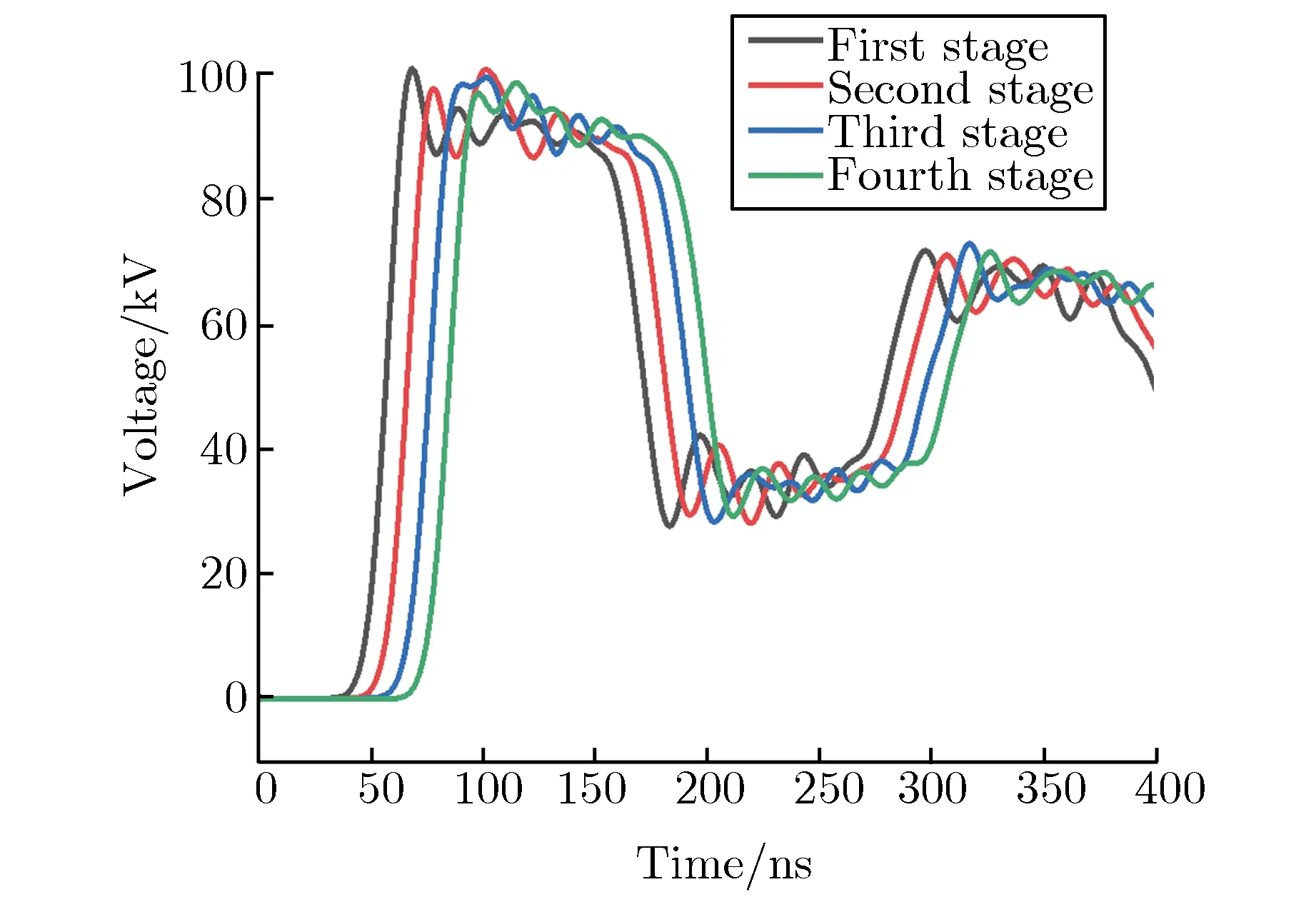

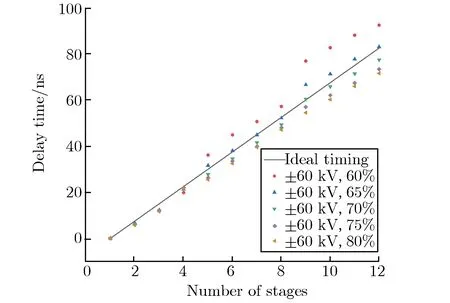

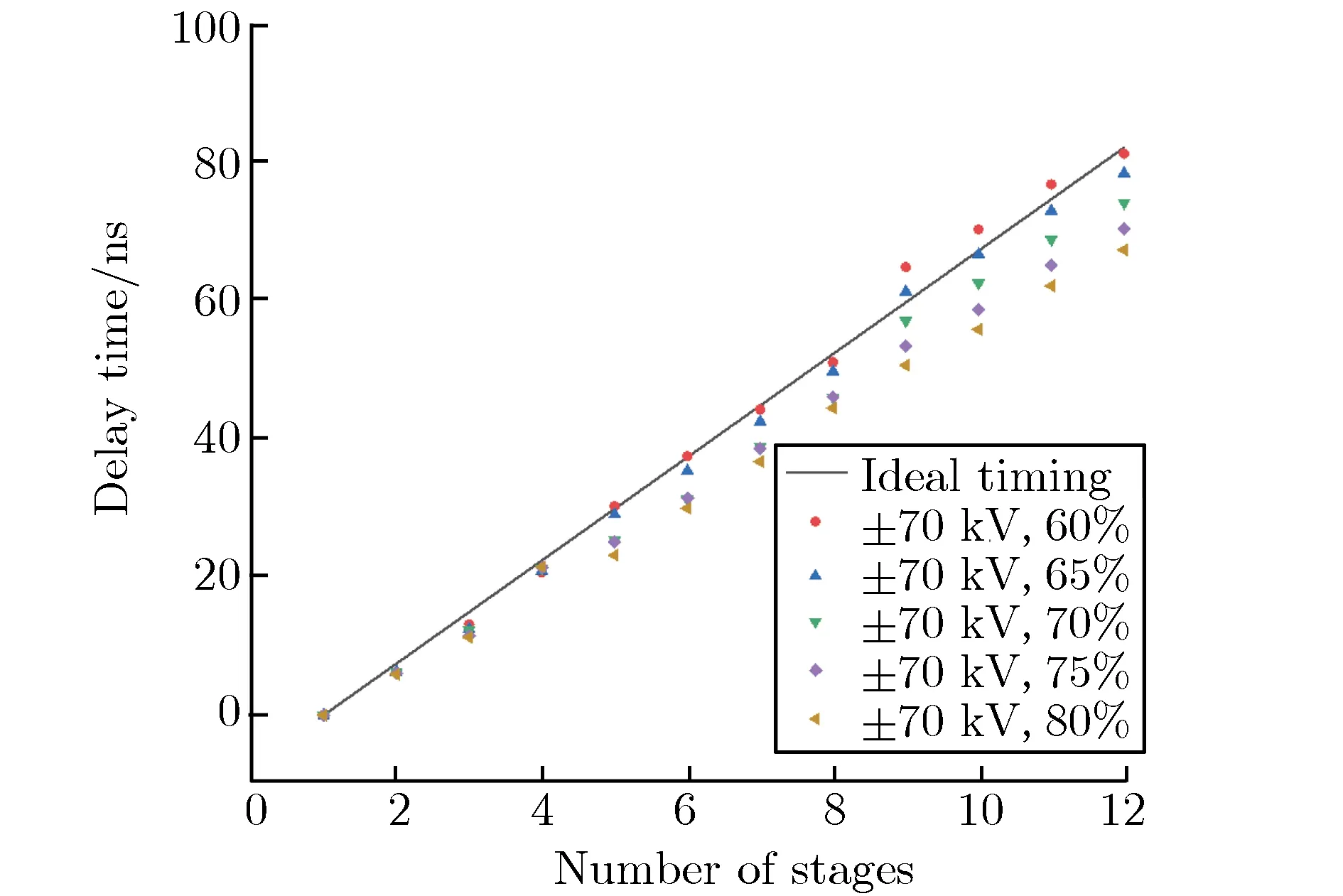

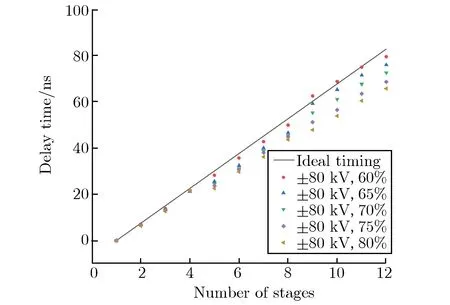

利用12级共用腔体串联FLTD实验平台开展了内置级联触发方法的可行性验证。通过每级触发支路开关上布置的B-dot探头,测量获得了±(60~80) kV充电电压、60%~80%工作系数下,12级FLTD模块触发支路开关时延与抖动如图9所示。由图9可见,12级FLTD模块可实现按理想时序依次触发放电,触发支路开关抖动小于2 ns。通过调节触发支路开关工作系数,可实现3个FLTD组件导通时序调控,第3个组件导通时刻最大调控范围约为20 ns,等效触发时序系数[12](相邻2级模块导通时间间隔与对应电磁脉冲传输时间的比值)为0.83~1.17。

(a) Trigger timing under ±60 kV charge voltage

(b) Trigger timing under ±70 kV charge voltage

(c) Trigger timing under ±80 kV charge voltage

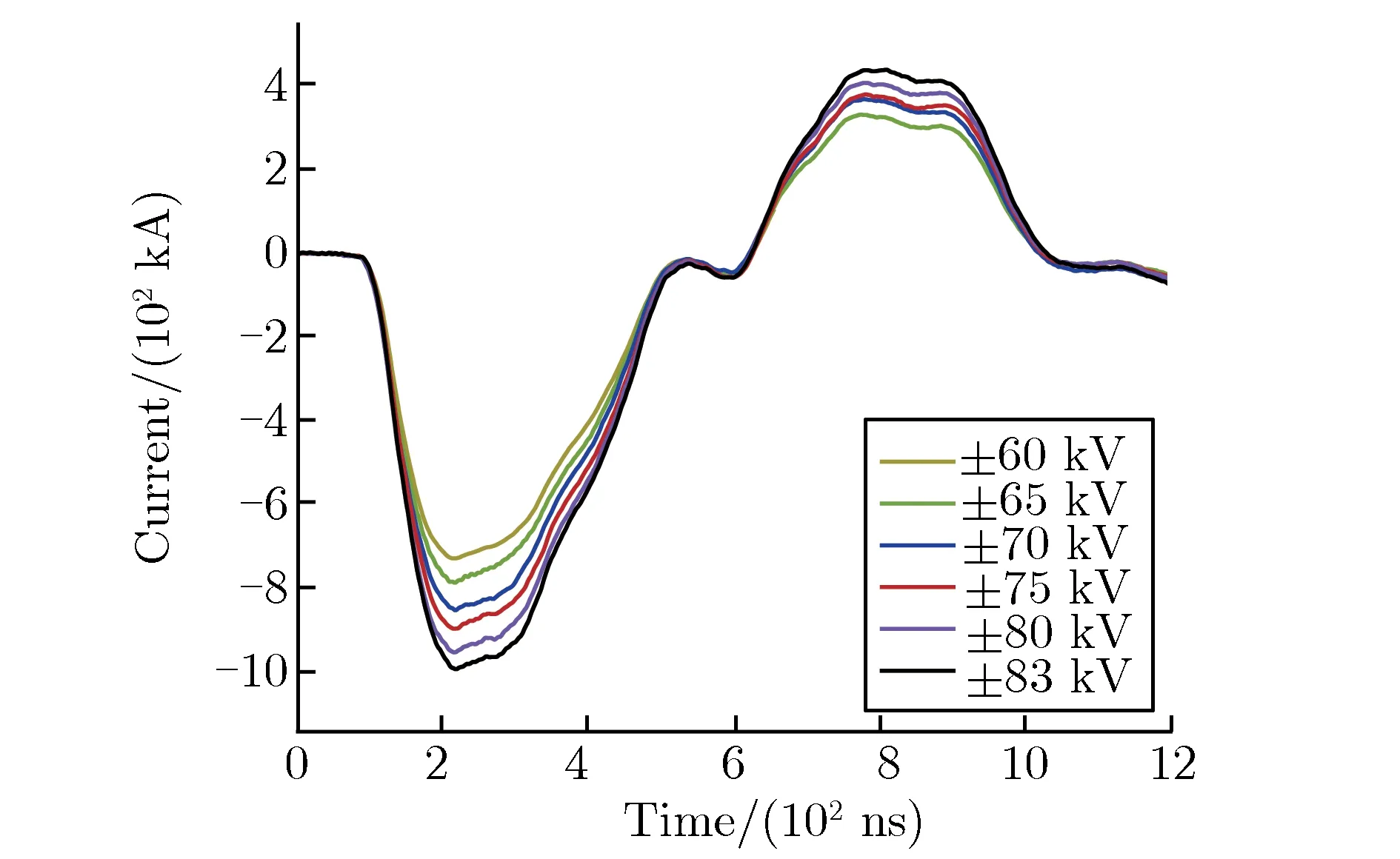

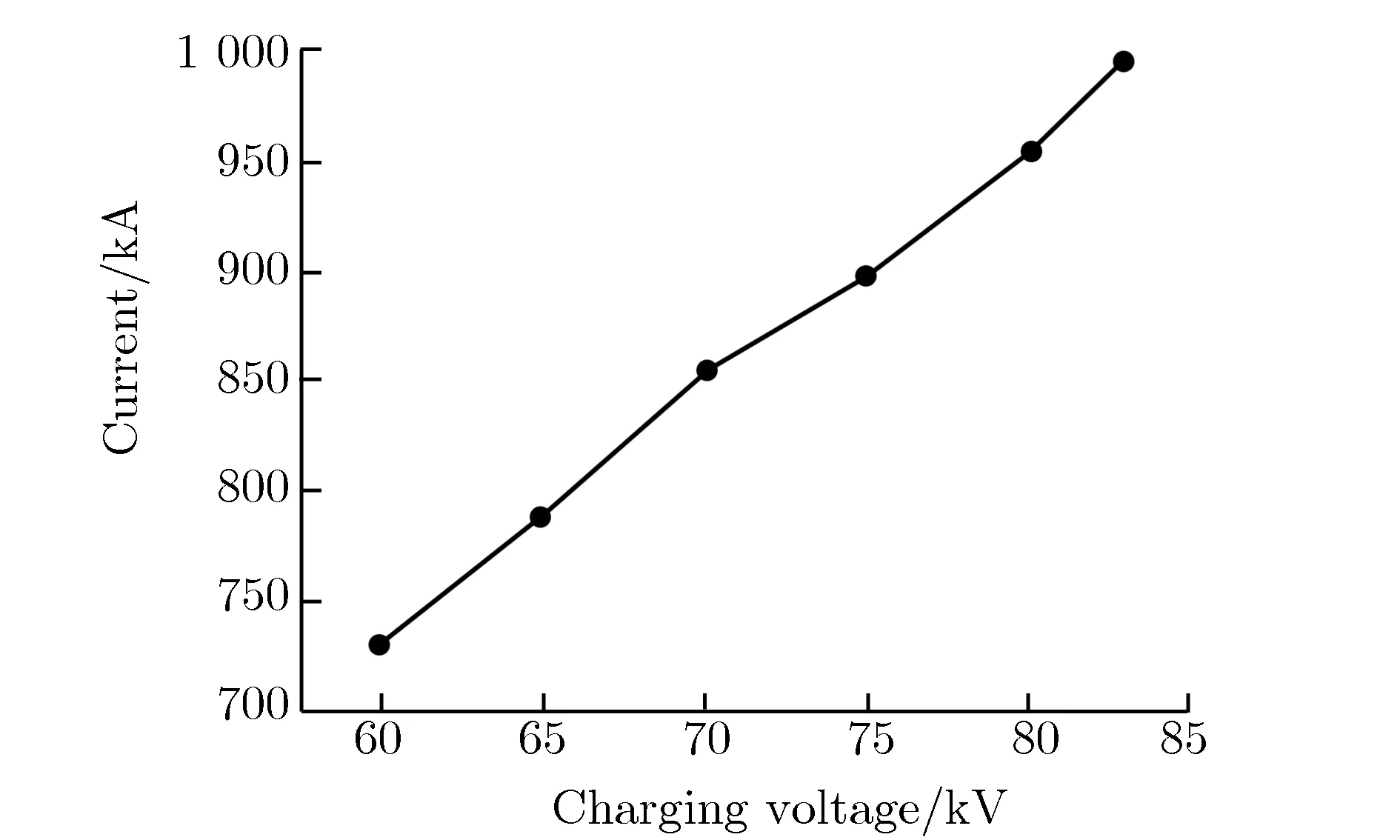

不同充电电压下,负载电流波形如图10所示。采用水电阻负载,近似匹配阻抗设计。由图10(a)可见,充电电压为±83 kV时,负载端可获得电压峰值约为1.1 MV、电流峰值约为1.0 MA、前沿约为74 ns的脉冲电流输出;由图10(b)可见,负载电流峰值随充电电压近似线性增加,表明FLTD装置内部开关触发放电同步性较好。

(a) Load current vs. time under different charging voltages

(b) Load peak current vs. charging voltage

3 结论

针对FLTD型驱动源大规模气体开关同步触发问题,本文提出了一种内置级联同步触发新方法,采用单级FLTD模块内置触发支路、共用腔体FLTD组件触发延时线触发及单路FLTD级联触发方法,可大幅降低引入触发脉冲数目和触发系统规模。建立了基于内置触发的FLTD 3维电磁及电路仿真模型,仿真结果表明:内置触发方式产生的触发脉冲陡度与常规触发方式相当,但触发脉冲幅值更高,是常规触发方式的2倍,更有利于主支路开关同步;触发延时线等效阻抗Z约为190 Ω,触发延时线中触发脉冲的传输速率约为0.25 m·ns-1,且各级触发脉冲幅值及前沿基本相同;级联触发脉冲幅值是触发支路充电电压的约2.8倍,上升时间约为50 ns,次级采用水介质传输线时可实现理想时序触发。

建立了12级串联共用腔体FLTD实验平台,实验验证了内置同步触发方法可行性,实现了引入1路脉冲同步触发12级串联FLTD,大幅降低了引入触发脉冲数目和触发系统规模。实验结果表明:内置级联触发方法可实现单路FLTD内气体开关按理想时序依次导通,各级触发支路开关抖动小于2 ns,通过调节触发支路开关工作系数,可实现单路FLTD导通时序调控,时序系数范围为0.83~1.17。

—— “T”级联